锁相环(PLL)电路设计及仿真分析

描述

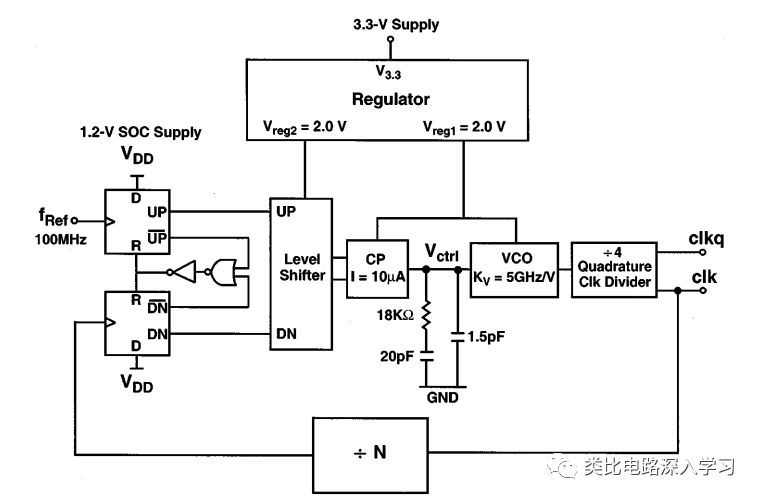

本文以SoC中的PLL为例,对PLL电路进行设计和仿真。

首先回顾一下核心参数:

| 参数 | 选定值 |

|---|---|

| 参考时钟频率FIN | 26MHz |

| 输出时钟频率FOUT | 104MHz~2.002GHz |

| 环路分频比N | 4~77 |

| 电荷泵电流Icp | 2uA |

| 压控振荡器的增益Kvco | 4GHz/V |

| 环路滤波器阶数 | 二阶 |

| 环路带宽BW | 500KHz |

| 环路相位裕度PM | 50° |

| R1 | 6.87kΩ |

| C1 | 55pF |

| C2 | 5.5pF |

设计指标:

| 参数 | 示例 |

|---|---|

| 参考时钟频率 | 13MHz~76.8MHz |

| 输出时钟频率 | 100MHz~2GHz |

| 锁定时间 | <100uS |

| Period Jitter RMS | <2ps |

| 输出时钟duty cycle | 40%~60% |

| 功耗 | <5mA |

| 输出时钟频率精度 | <±300ppm |

下面对子模块进行设计

1)鉴频鉴相器(PFD)

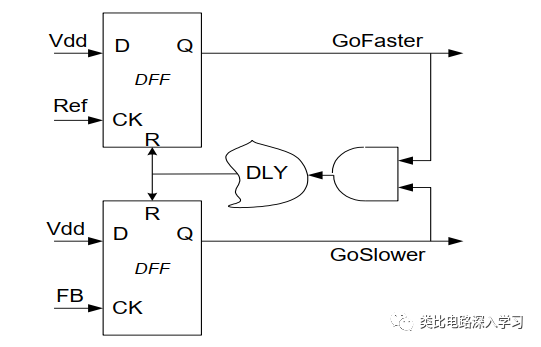

本文选择DFF based PFD,其电路结构如下

+

这里需要注意的就是dead zone,即死区时间。

假定不加入图中的DLY模块,当Ref和FB rising edge很接近,受限于电路的速度,GoFaster/GoSlower可能会是很窄的脉冲,那么charge pump将不能打开。从传输函数上看,当相位误差为0附近的这段区域,PFD+CP的增益将会变小甚至是0,导致传输函数出现非线性,从而jitter变大。

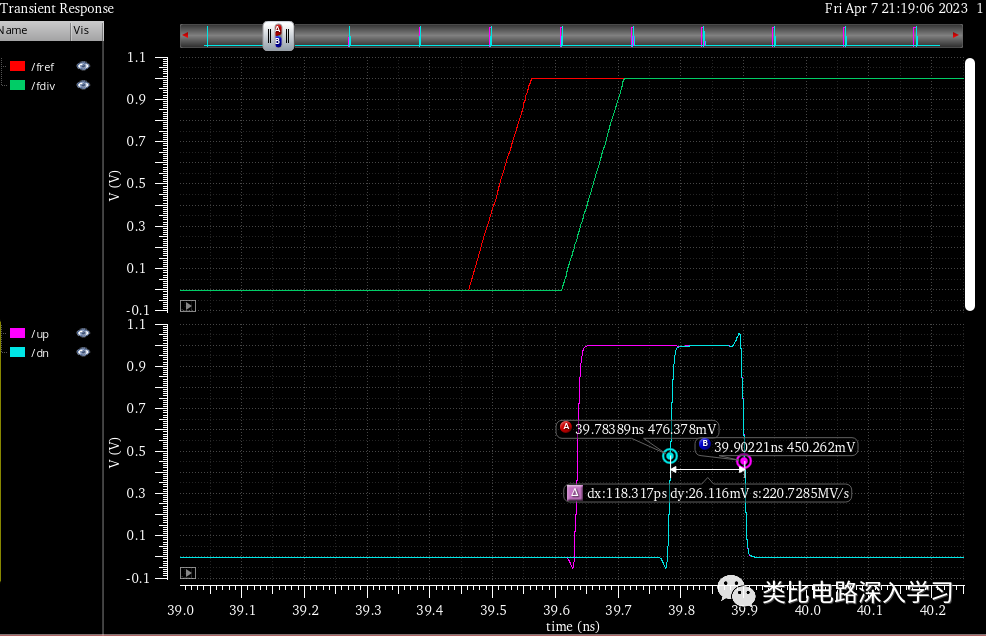

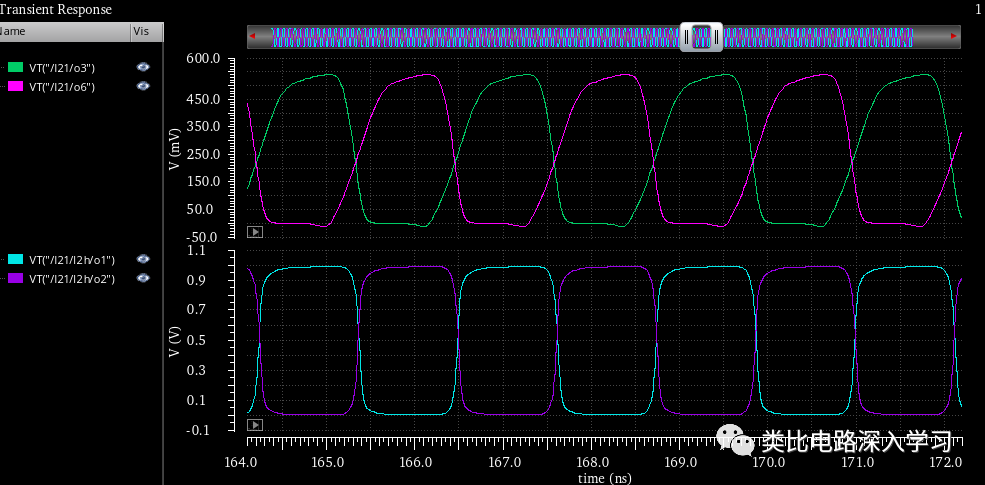

因为我们需要设计一定的死区时间,假定120ps,仿真看下PFD的行为如下

2)电荷泵(charge pump)

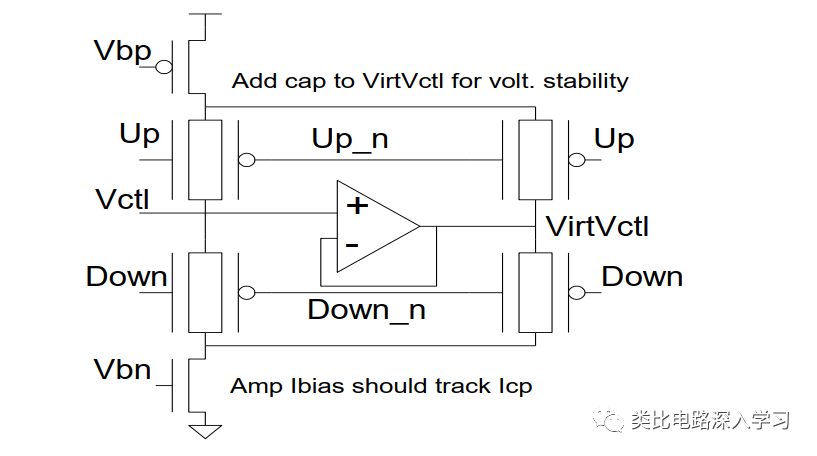

本文选择Young提出的经典结构,由于virtual vctl的引入,有效的对抗了时钟馈通和电荷注入,保证了CP具备良好的线性度。其电路结构如下

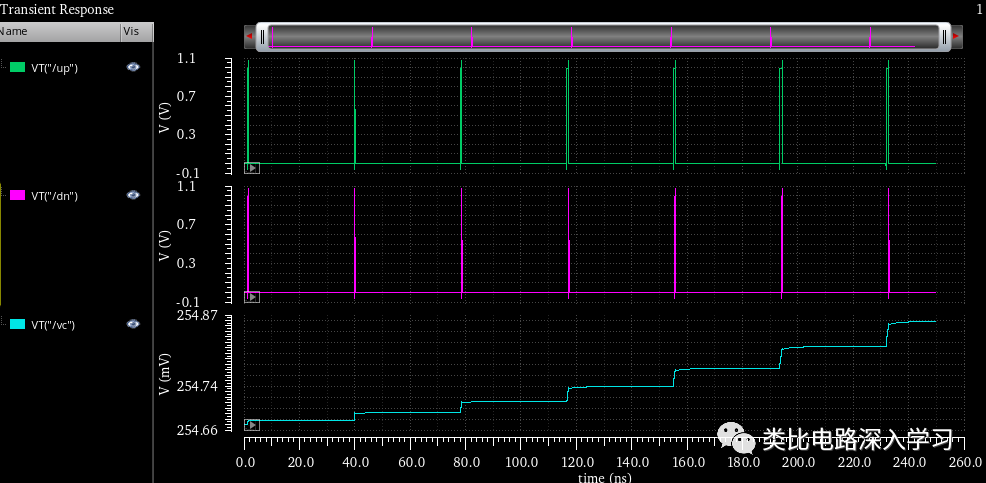

电荷泵的电流为2uA,PFD+CP联合仿真瞬态结果如下

如果是RF或者ADC应用,那么需要对CP的结构、电流、Noise进行优化。本文是SoC应用,所以CP的noise并不重要,这里只要保证基本的功能、良好的线性度即可。

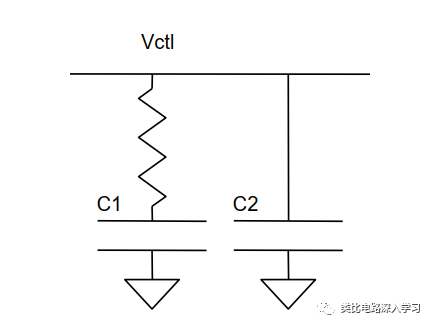

3)环路滤波器(LPF)

目前主流的环路滤波器结构为双CP、gm-C filter结构,可以有效的减小面积、提高CP线性度、降低电阻噪声。

针对SoC应用,为降低设计复杂度,本文采用了连续时间、无源环路滤波器结构,即仅R和C构成,如下图所示

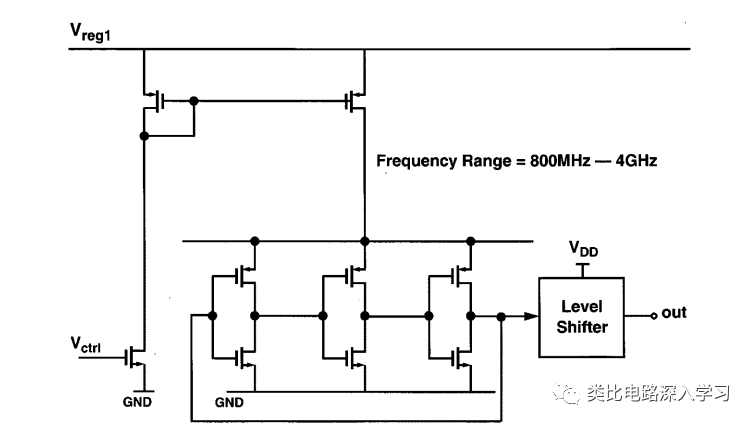

4)压控振荡器(VCO)

本文采用V2I+ICO(Ring)结构的压控振荡器,环形振荡器采用三级反相器实现。如下图所示,

charge pump的电压为1V,为保证up和dn电流线性度,vctrl电压范围设定为0.2V~0.8V,这样Corner下需要保证振荡器最高振荡频率>2GHz

Kvco~=4.1GHz/V

5)电平转换器(level shift)

VCO电平转换器,一般有dc和ac两种结构,本文采用dc结构,示意图如下

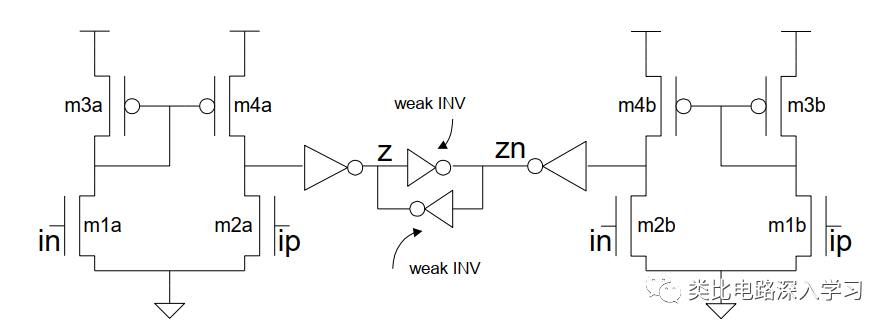

6)环路分频器(loop divier)

支持4~77连续分频,本文采用 2/3 Prescaler+N-divider结构

采用Prescaler目的是为了降低N-divider的速度要求,timing更好实现。

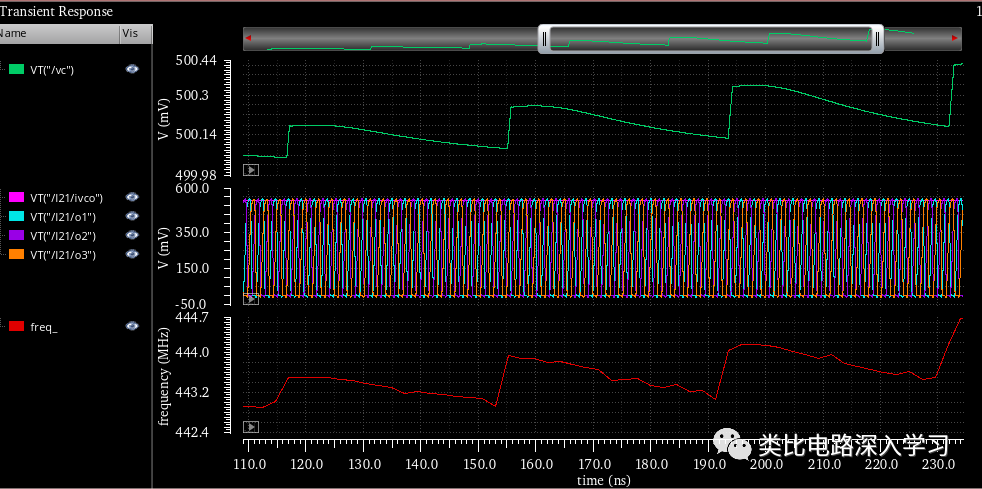

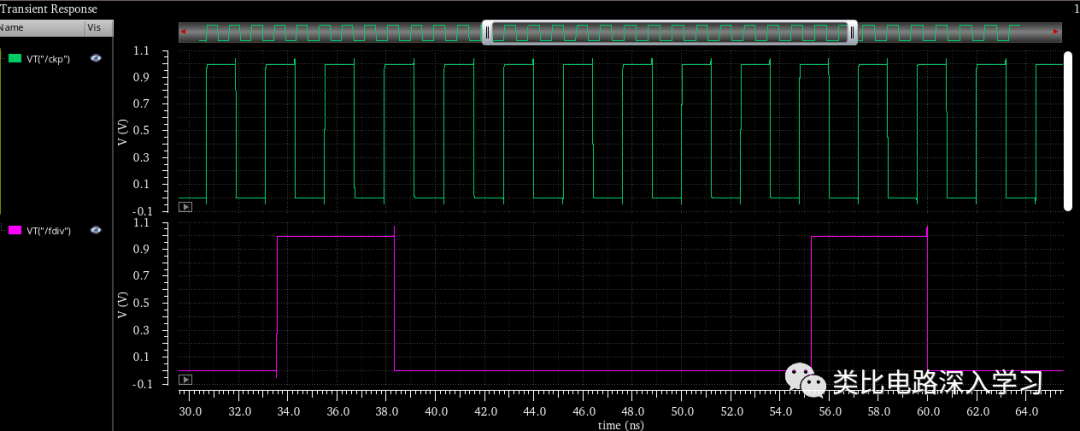

配置N_div=9,仿真波形如下:

7)锁相环顶层(PLL)

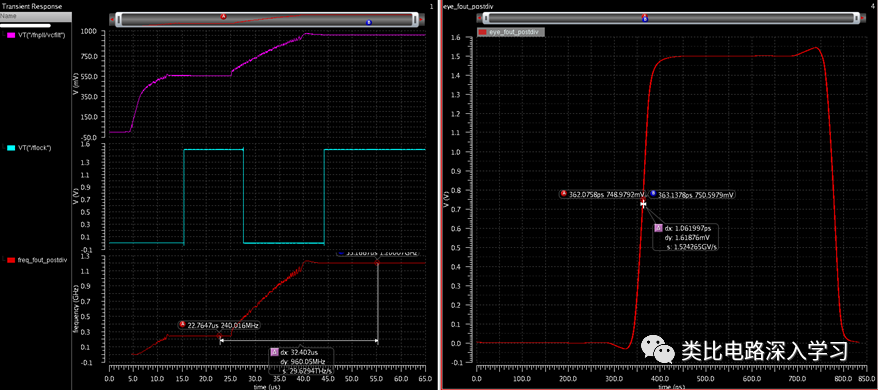

配置240M/1.2G,Top仿真结果如下

-

锁相环PLL的工作原理 锁相环PLL应用领域2024-11-06 4489

-

了解锁相环(PLL)瞬态响应 如何优化锁相环(PLL)的瞬态响应?2023-10-23 3386

-

pll锁相环的作用 pll锁相环的三种配置模式2023-10-13 5679

-

pll锁相环倍频的原理2023-09-02 5269

-

锁相环PLL的基础知识2022-12-23 6985

-

LabVIEW锁相环(PLL)2022-05-31 8104

-

锁相环(PLL)的工作原理及应用2022-03-29 16313

-

PLL(锁相环)电路原理是什么?2022-01-21 4109

-

如何设计并调试锁相环(PLL)电路2016-01-07 1343

-

锁相环(PLL)电路设计与应用(日)远坂俊_图解实用电子技术丛书2015-12-03 1725

-

锁相环2011-10-26 17708

-

锁相环(PLL)电路设计与应用2011-09-14 7986

-

锁相环(PLL),锁相环(PLL)是什么意思2010-03-23 6467

-

锁相环设计仿真与应用2008-08-16 1493

全部0条评论

快来发表一下你的评论吧 !