SystemVerilog实用知识点:覆盖率之Function Coverage

电子说

描述

SystemVerilog是一名芯片验证工程师,必须掌握的一门语言,其中Function Coverage是必须要懂的知识点之一;

看完这篇,应该就会写Function Coverage了;

一、概述

有一定基础,想直接看用法,直接看第二部分——实现(强调!代码部分要精读,文字略抽象,例子好理解)。

功能覆盖率(Function Coverage)是衡量验证完备性的重要标准之一。

其用于度量验证中已执行的测试点(cover point)占设计规范的比例,从而避免功能验证的遗漏。或者说,Functional coverage是验证工程师基于对DUT的认识来对验证feature进行分解后,将需要覆盖的点进行分析后写出,因此对于DUT Spec的信息提取非常重要。

Functional_coverage可以检查:

1. 你关心的场景是否覆盖完备;2. 验证工程师构造的随机激励的随机程度/合理性;3. 从Spec中提取的feature点是否覆盖完备;...

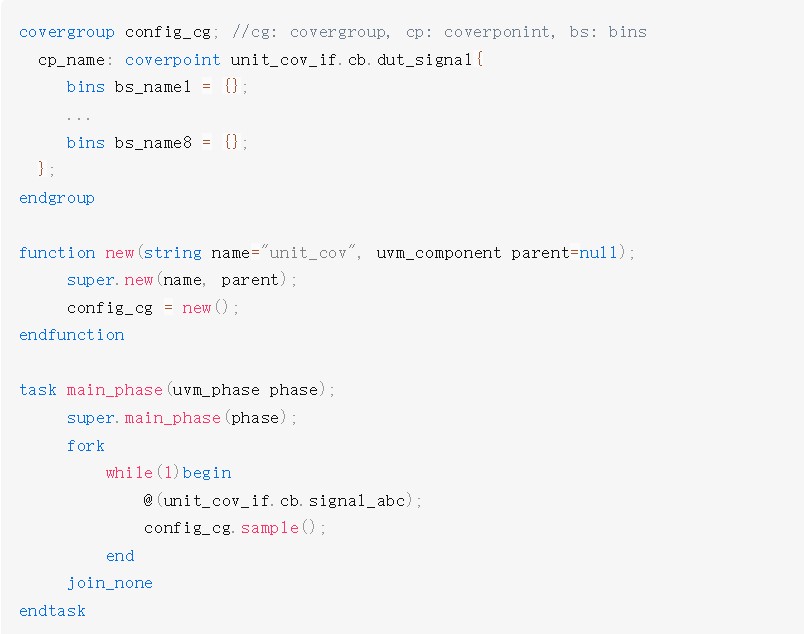

Function Coverage通过编写coverage group, coverage points和bins等来构造收集“容器”。这里我们不介绍Assertion Coverage, Code Coverage等,以后会单独介绍。

收集Function Coverage的相关验证文件是由验证工程师定义编写的,灵活度很高,所以更需要谨慎对待,这是个Review的过程,一般需要编写:unit_coverage.sv + unit_coverage_interface.sv + top.sv。

1. unit_coverage.sv (unit_cov.sv),可能包含多个功能覆盖模型coverage group,构造的收集“容器”,收集过程在这里实现;2. unit_coverage_interface.sv(unit_cov_if.sv),定义unit_cov.sv中需要用到的interface;3. top.sv,将unit_cov_if.sv中定义的interface与DUT中对应的interface连接起来;

二、实现

功能覆盖率模型/覆盖组(cover group):

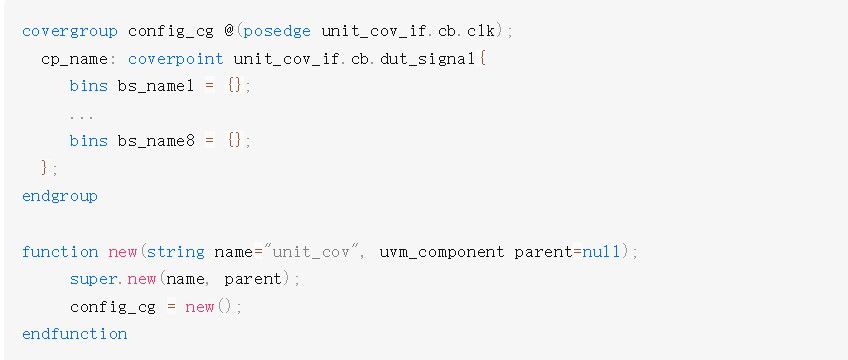

覆盖组是使用cover group构造定义的。

ex1: 会在指定的signal_abc变化时才采样

ex2:在时钟上升沿((posedge)采样。

覆盖点(cover ponit):

覆盖点是使用cover ponit和bins构造定义的。

一个覆盖组可以包含一个或多个覆盖点。每个覆盖点都与“ bins”关联。“bins”可自动创建,也可以明确定义。

ex1:自动创建bins

为coverpoint变量范围的每个值自动创建一个bins,这称为自动或隐式bins。

对于“ n”位的整数coverpoint变量,将创建2^n个bin,但是最多为64个,当2^n大于64时,每个bin不再是一个值,而是2^n/64

ex2:明确定义bins

该方式--- 常用,这里重点看每个bins定义代表的不同意义。

在覆盖点标识符(cover point)之后,在大括号{}中显式声明bins,其中声明bins名称和变量值/范围。

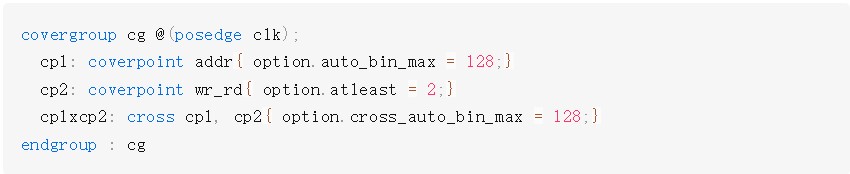

ex3:交叉覆盖(cross)

覆盖选项(cover options)

at_least

每个bins的最小匹配/采样次数。默认值为“ 1”,默认情况下,数值采样了1次就可以计入有效的bin(已覆盖)。可以通过修改at_least来修改每个bin对应的最小采样次数,注意,如果低于at_least数值,则该bin不算被覆盖。在covergroup里使用 option.at_least,会影响所有的coverpoint里的bin。在coverpoint里使用 option.at_least,只影响该coverpoint下的bin,但coverpoint中使用会覆盖covergroup中的使用。

auto_bin_max

没有为coverpoint明确定义bins时自动创建bins的最大数量。默认值为“ 64”。

cross_auto_bin_max

没有默认值,它是无界的。

如果对一个covergroup实例化了很多次,那么SV默认会把所有实例的覆盖率合并在一起。 option.per_instance = 1,表示covergroup的每一个实例的覆盖率都要单独计算。

goal

不论covergroup或是coverpoint的目标覆盖率皆是100%,不过也可以通过option.goal=value,来降低覆盖率目标,这个选项只会影响覆盖率报告。

......

更多options和关于Function Coverage更详细的描述/用法去翻阅《system verilog官方手册》:《IEEE Standard for SystemVerilog — Unified Hardware Design, Specification, and Verification Language》的第19章。

-

一文详解Modelsim代码覆盖率功能使用2020-12-09 7670

-

怎么用Vivado做覆盖率分析2024-01-03 3688

-

为什么覆盖率分析师没有证明电阻器已经过测试?2019-01-07 2485

-

如何改善5G覆盖率?2020-12-15 2073

-

如何提高DFT设计测试覆盖率?2021-05-07 3163

-

关于SpinalHDL中的验证覆盖率收集简单说明2022-06-24 3567

-

重点厘清覆盖率相关的概念以及在芯片开发流程中跟覆盖率相关的事项2022-09-14 3100

-

Systemverilog覆盖率的合并和计算方式2023-03-21 1885

-

Verilog代码覆盖率检查2012-04-29 9116

-

IP开发时如何考虑复用覆盖率2018-02-18 3413

-

嵌入式代码覆盖率统计方法和经验2021-01-06 4035

-

统计嵌入式代码覆盖率的方法和经验2021-03-29 2922

-

高覆盖率的Verilog代码的编写技巧2022-05-26 5235

-

脱离代码谈芯片验证关键指标:覆盖率2023-04-17 6684

-

SystemVerilog的覆盖率建模方式2023-06-25 2533

全部0条评论

快来发表一下你的评论吧 !