边沿检测电路设计

电子说

1.4w人已加入

描述

上升沿检测电路

01

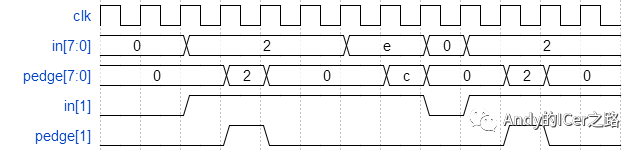

题目:对于8位向量中的每个位,检测输入信号何时从一个时钟周期的0变为下一个时钟周期的1(类似于上升沿检测)。应在从0到1的跳变发生后的周期内设置输出位。

以下为例子, 为了清楚起见,分别显示了in [1]和pedge [1]。

module top_module(

input clk,

input [7:0] in,

output reg [7:0] pedge);

reg [7:0] d_last;

always @(posedge clk) begin

d_last <= in;

pedge <= in & ~d_last; // A positive edge occurred if input was 0 and is now 1.

end

endmodule

第九行 d_last <= in ; 是记录信号in上一个cycle的状态;

第十行 pedge <= in & ~d_last; 检测上升沿,简答来说就是检测input由0变1。

双边沿检测电路

02

题目:对于8位向量中的每个位,检测输入信号何时从一个时钟周期更改为下一个时钟周期(检测任何边沿)。应在从0到1的跳变发生后的周期内设置输出位。

module top_module (

input clk,

input [7:0] in,

output [7:0] anyedge

);

reg [7:0] d_old;

always@(posedge clk)begin

d_old <= in;

anyedge <= d_old^in;

end

endmodule

第八行 d_old <= in ; 是记录信号in上一个cycle的状态;

第九行 anyedge <= d_old^ in ; 即现在的信号in与上一个状态不一样的话,输出1(异或是两个信号不一样置1),这样该电路就可以双边沿检测。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA设计经验之边沿检测2012-03-01 5480

-

FPGA设计中的边沿检测问题2012-02-01 1096

-

FPGA设计经验:边沿检测2017-08-16 2228

-

fpga应用篇(二):边沿检测2017-04-06 4024

-

微弱光检测的电路设计2009-04-22 1679

-

边沿检测与提取-轮廓跟踪知识详解2018-01-29 687

-

FPGA学习系列:12. 边沿检测设计2018-06-13 6290

-

边沿检测的目的及电路原理分析2019-11-19 11960

-

Verilog系统函数和边沿检测2022-03-15 3401

-

FPGA学习-边沿检测技术2022-11-26 2939

-

Verilog边沿检测的基本原理和代码实现2023-05-12 5803

-

如何设计边沿采样的触发器呢?2023-06-05 2596

-

什么是边沿检测2023-06-17 4241

-

Verilog实现边沿检测的原理2023-06-28 4586

-

高速过电流检测电路设计2025-06-06 940

全部0条评论

快来发表一下你的评论吧 !