***工艺流程图及成像过程详解

制造/封装

描述

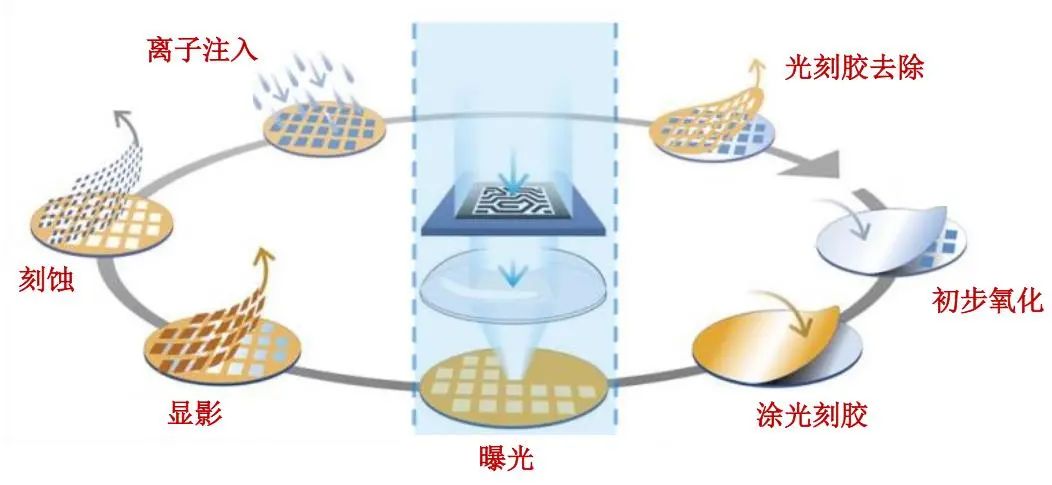

***是芯片制造中最复杂、最昂贵的设备。芯片制造可以包括多个工艺,如初步氧化、涂光刻胶、曝光、显影、刻蚀、离子注入。这个过程需要用到的设备种类繁多,包括氧化炉、涂胶显影机、***、薄膜沉积设备、刻蚀机、离子注入机、抛光设备、清洗设备和检测设备等。在整个半导体芯片制造过程中,光刻是最复杂工艺,光刻工艺的费用约占芯片制造成本的1/3左右,耗费时间占比约为40-50%,光刻工艺所需的***是最贵的半导体设备。

***可分为前道***和后道***。***既可以用在前道工艺,也可以用在后道工艺,前道***用于芯片的制造,曝光工艺极其复杂,后道***主要用于封装测试,实现高性能的先进封装,技术难度相对较小。

图表1:光刻工艺流程图

数据来源:***行业报告,中泰证券研究所

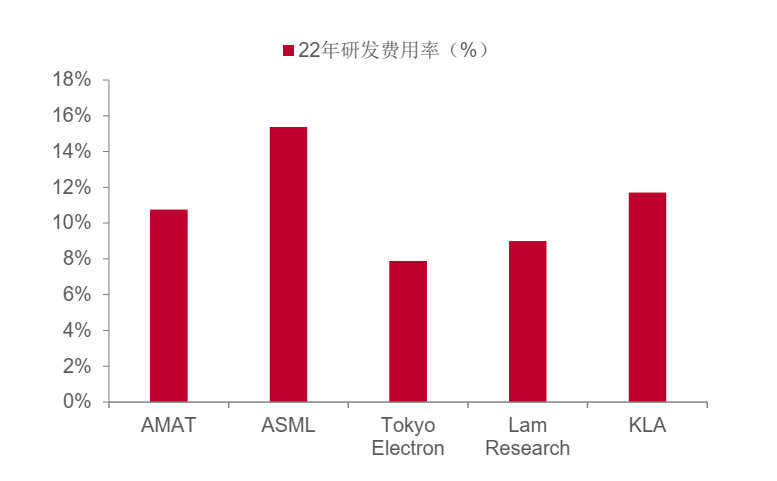

***研发难度大,零部件海外垄断 图表 2:全球前五大半导体设备厂商研发费用率

数据来源:***行业报告,中泰证券研究所

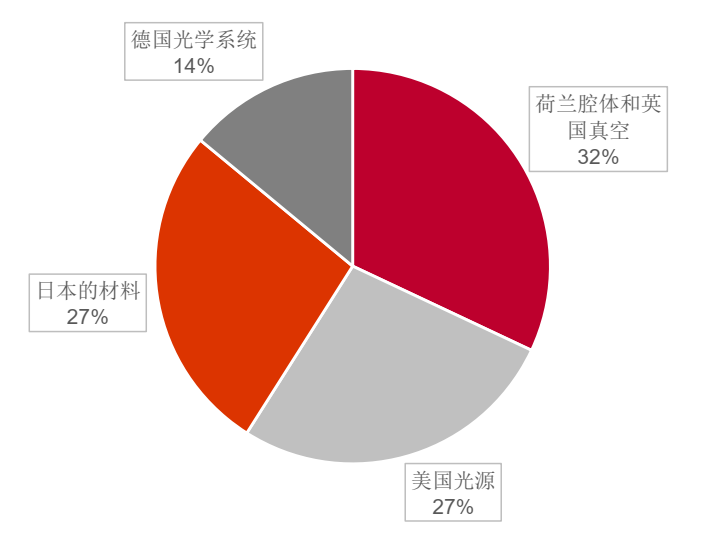

***厂商研发费用率高:22年全球前五大半导体设备厂商的平均研发费用率为11%, 其中ASML研发费用率为15%, 高于其他设备厂商。 ***零部件供应商遍布全球,核心零部件来自德国和美国:代表***最高端技术的EUV***里面有10万多个零部件,全球超过5000家供应商。整个***中,荷兰腔体和英国真空占32%,美国光源占27%,德国光学系统占14%, 日本的材料占27%。 图表 3:EUV***零部件占比

数据来源:***行业报告,中泰证券研究所

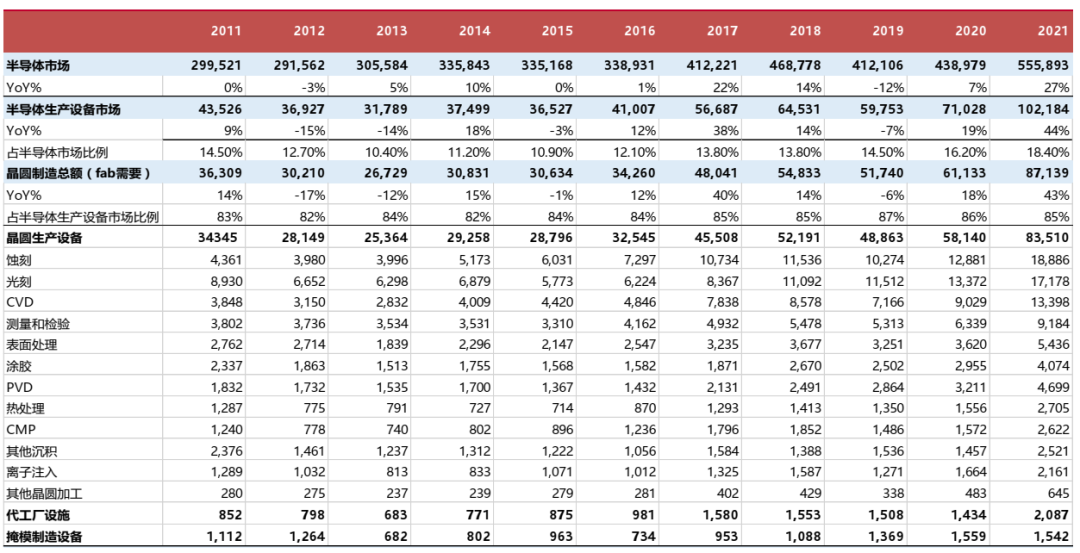

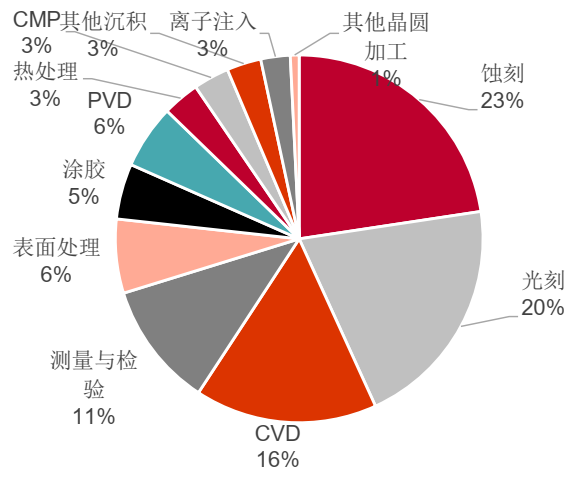

光刻设备单价最高,市场规模全球第二 2021年全球前道光刻设备市场规模为172亿美元,其市场份额在晶圆生产设备中占比为20%,仅次于刻蚀设备。***价格昂贵, ASML当前EUV***单价为1.5亿-2亿美元。 图表 4:全球半导体制造设备市场份额

数据来源:***行业报告,中泰证券研究所

IGBT相比MOSFET,可在更高电压下持续工作,同时需要兼顾高功率密度、低损耗、高可靠性、散热好、低成本等因素。一颗高性能、高可靠性与低成本的IGBT芯片,不仅仅需要在设计端不断优化器件结构,对晶圆制造和封装也提高了更高的要求。 图表 5:2021年晶圆生产设备市场份额占比

数据来源:***行业报告,中泰证券研究所

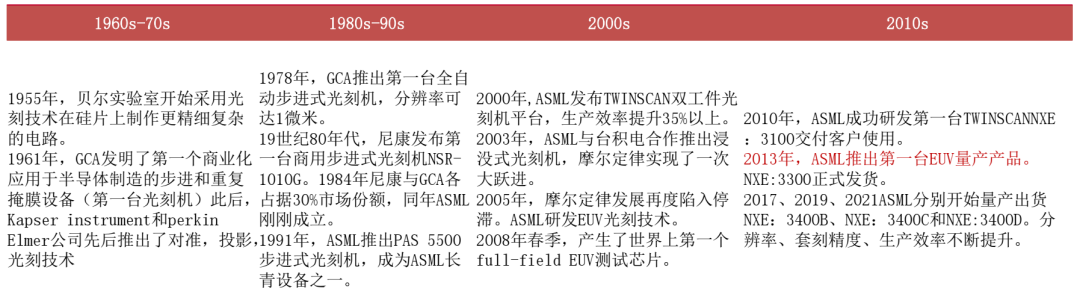

从接触式到EUV, ASML成为绝对龙头 1961年, 第一台接触式***由美国GCA推出, 历经60年的发展,ASML后来者居上,成为当前***行业的绝对龙头。

***问世:1955年,贝尔实验室开始采用光刻技术, 1961年,GCA公司制造出第一台接触式***。

步进式***推出:1978年,步进式***推出,1984年尼康和GCA各占30%份额,同年ASML成立。

浸没式***推出:2000年,ASML推出双工件台***,2003年ASML推出浸没式***,至此ASML一举超越其他厂商,后来者居上。

EUV***推出:2013年,ASML推出第一台EUV量产产品,进一步加强行业垄断地位。 图表 6:光刻技术发展历程

数据来源:***行业报告,中泰证券研究所

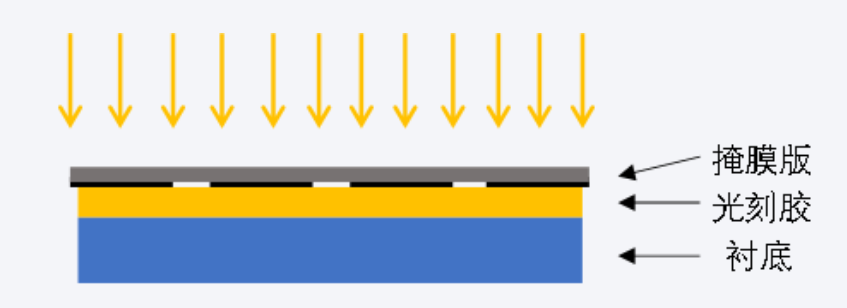

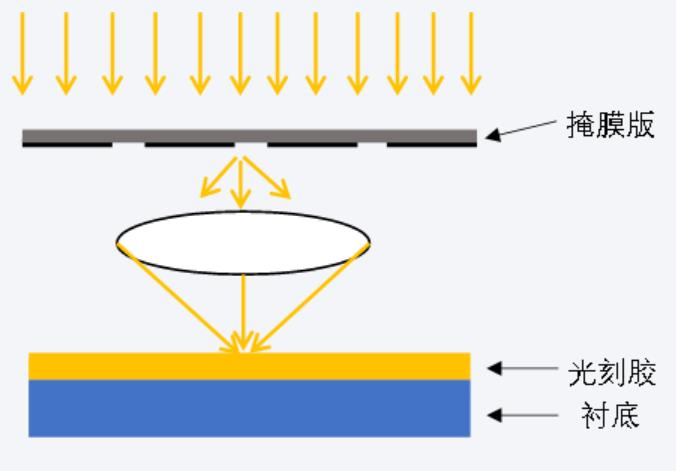

光刻技术:从接触式到接近式 接触式光刻技术良率低、成本高:接触式光刻技术出现于20世纪60年代,是小规模集成电路时期最主要的光刻技术。接触式光刻技术中掩膜版与晶圆表面的光刻胶直接接触,一次曝光整个衬底,掩膜版图形与晶圆图形的尺寸关系是1:1 ,分辨率可达亚微米级。

特点:接触式可以减小光的衍射效应,但在接触过程中晶圆与掩膜版之间的摩擦容易形成划痕,产生颗粒沾污,降低了晶圆良率及掩膜版的使用寿命,需要经常更换掩膜版,故接近式光刻技术得以引入。

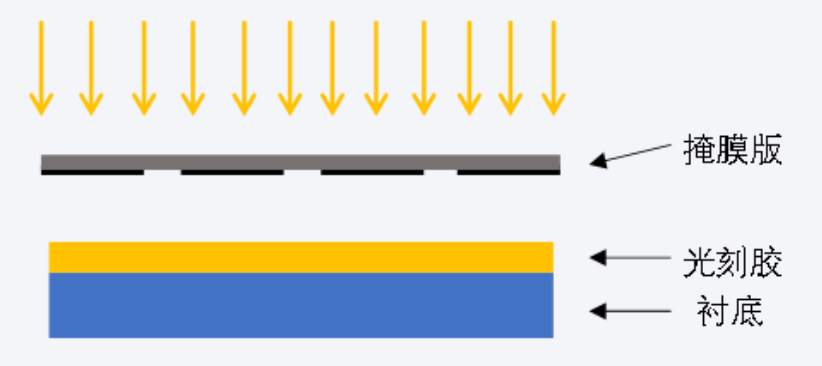

接近式光刻技术分辨率有限:接近式光刻技术广泛应用于20世纪70年代,接近式光刻技术中的掩膜版与晶圆表明光刻胶并未直接接触,留有被氮气填充的间隙。

特点:最小分辨尺寸与间隙成正比,间隙越小,分辨率越高。缺点是掩膜版和晶圆之间的间距会导致光产生衍射效应,因此接近式***的空间分辨率极限约为2μ m。随着特征尺寸缩小,出现了投影光刻技术。 图表 7:接触式光刻示意图

图表 8:接近式光刻示意图

数据来源:***行业报告,中泰证券研究所

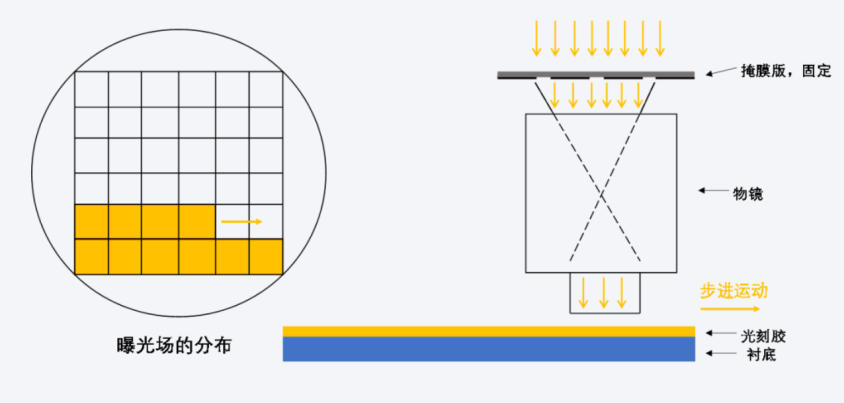

光刻技术:从接近式到投影式 投影光刻技术有效提高分辨率:20世纪70年代中后期出现投影光刻技术,基于远场傅里叶光学成像原理,在掩膜版和光刻胶之间采用了具有缩小倍率的投影成像物镜,有效提高了分辨率。早期掩膜版与衬底图形尺寸比为1:1,随着集成电路尺寸的不断缩小,出现了缩小倍率的步进重复光刻技术。

步进重复光刻主要应用于0.25μm以上工艺:光刻时掩膜版固定不动,晶圆步进运动,完成全部曝光工作。随着集成电路的集成度不断提高,芯片面积变大,要求一次曝光的面积增大,促使更为先进的步进扫描***问世。目前步进重复光刻主要应用于0.25μ m以上工艺及先进封装领域。

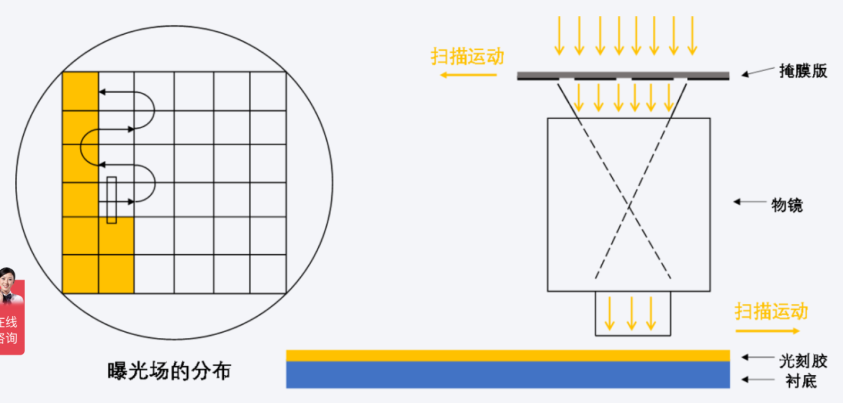

步进扫描光刻被大量采用:步进扫描***在曝光视场尺寸及曝光均匀性上更有优势,在0.25μm以下的制造中减少了步进重复***的应用。步进扫描采用动态扫描方式,掩膜版相对晶圆同步完成扫描运动,完成当前曝光后,至下一步扫描场位置,继续进行重复曝光,直到整个晶圆曝光完毕。从0.18μm节点开始,硅基底CMOS工艺大量采用步进扫描光刻,7nm以下工艺节点使用的EUV采用的也是步进扫描方式。 图表 9:投影光刻示意图

图表 10:步进重复光刻示意图

图表11:步进扫描光刻示意图

光刻技术:干法光刻和浸润式光刻

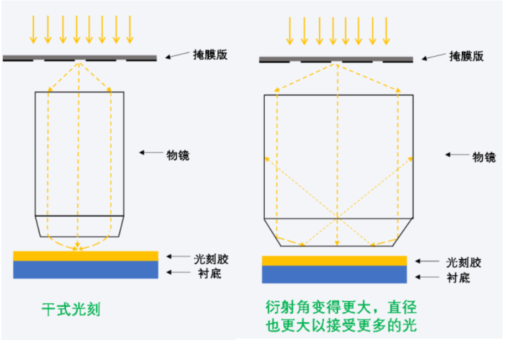

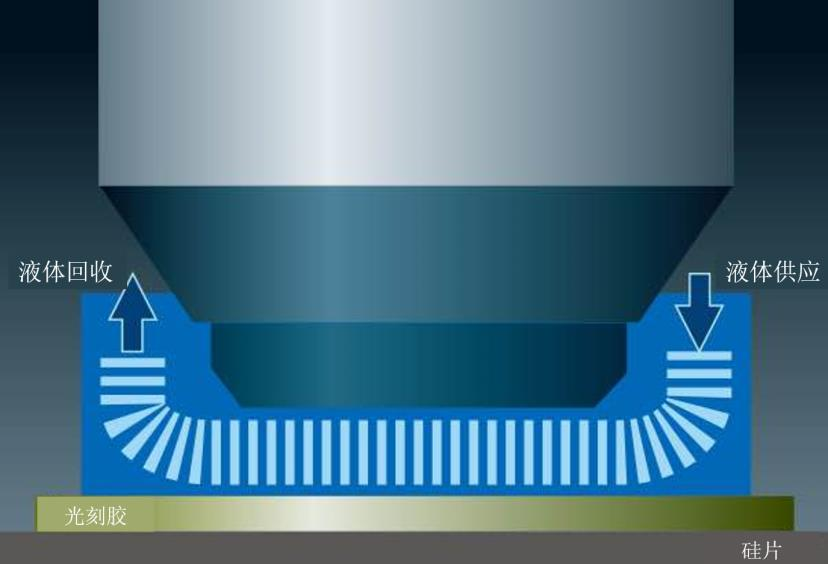

投影光刻技术根据投影物镜下方和晶圆间是否有水作为介质可以分为干式光刻和浸润式光刻。

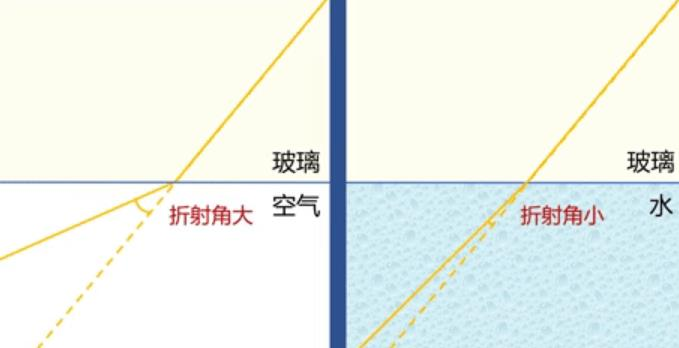

干式光刻技术无法满足不断缩小的线宽:光从投影物镜射出,由玻璃介质进入空气介质,会发生衍射,光角度发生变化,最终成像于晶圆表面。随着线宽不断缩小,衍射效应不断增加,需要增大投影物镜直径来接受更多的光, 这导致物镜内聚焦的光角度越来越大,再经过折射效应, 射出投影物镜的光角度接近水平,无法成像,因此出现了浸润式光刻技术。

浸润式光刻技术使光刻水平进一步提高:投影物镜下方和晶圆间充满水,由于水的折射率和玻璃接近(在193nm波长中,折射率空气=1,水=1.44,玻璃约为1.5),从投影物镜射出的光进入水介质后,折射角较小,光可以正常从物镜中折射出来。ArF光源加浸润技术实际等效的波长为193nm/1.44=134nm。 图表 11:干式光刻示意图

图表 12:浸润式系统示意图

图表13:光线在玻璃、空气、水中的折射

数据来源:***行业报告,中泰证券研究所

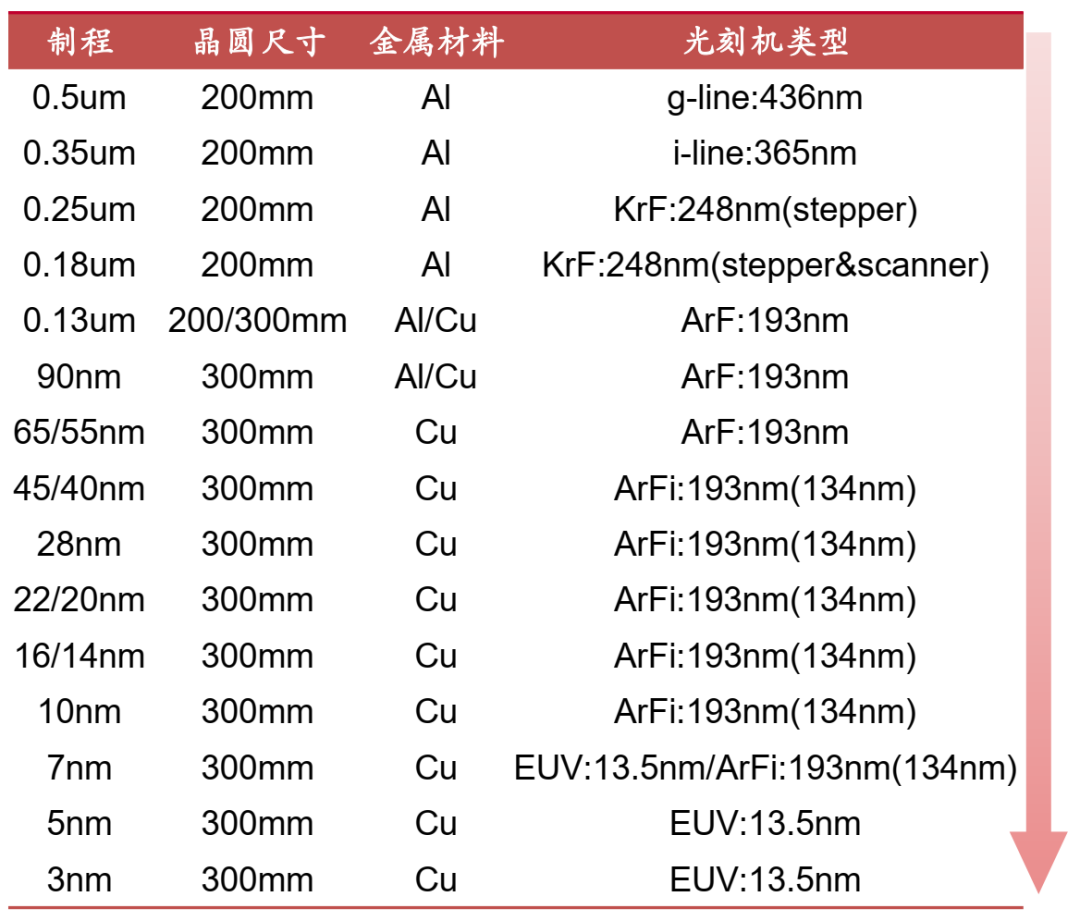

***的技术水平决定集成电路的发展水平

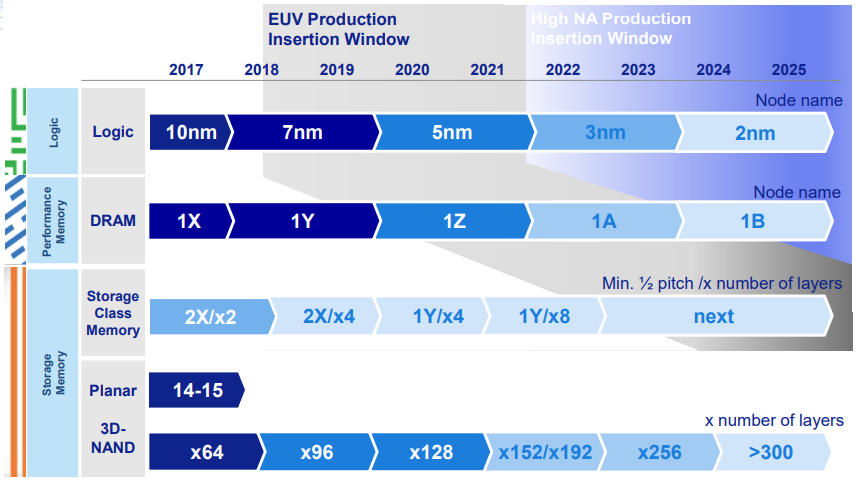

***的技术水平很大程度上决定了集成电路的发展水平。随着EUV***的出现,芯片制程最小达到3nm。目前ASML正在研发High-NA EUV***,制程可达2nm、 1.8nm,预计2025年量产。同时,英伟达在23年GTC大会上也表示其通过突破性的光刻计算库cuLitho,将计算光刻加速40倍以上,使得2nm及更先进芯片的生产成为可能, ASML、台积电已参与合作,届时将带动芯片性能再次提高。 图表 14:各个工艺节点和光刻技术的关系

图表 15:ASML对客户节点演进的预测

多重曝光亦可实现更小线宽,但工艺难度大

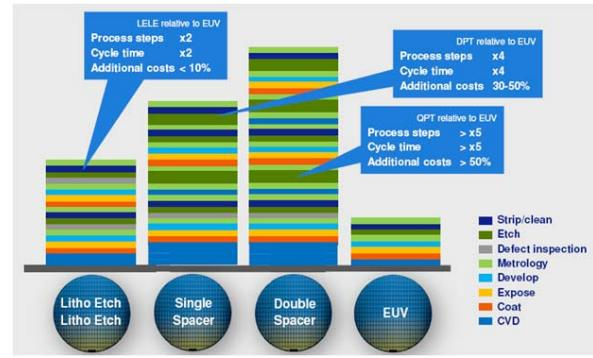

光刻技术利用多重曝光工艺实现更小线宽。三种多重曝光技术:LELE、LFLE、SADP,误差较小的是SADP。

1)LELE(LITHO-ETCH- LITHO-ETCH 光刻-刻蚀-光刻-刻蚀:原理是把原来一层光刻图形拆分到两个或多个掩膜上,利用多次曝光和刻蚀来实现原来一层设计的图形。

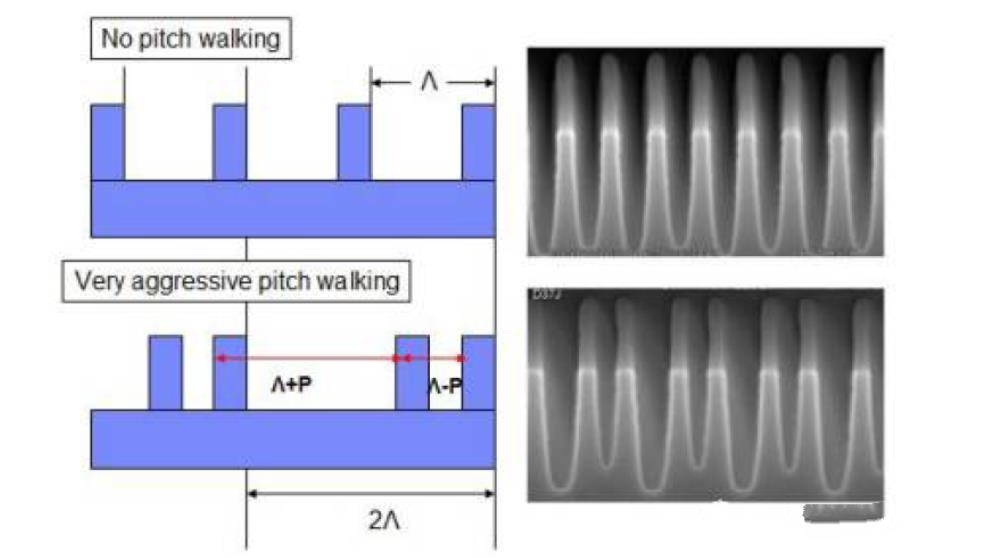

2)LFLE(LITHO-FREEZE-LITHO-ETCH 光刻-固化-光刻-刻蚀):原理是将第二层光刻胶加在第一层已被化学冻结但没去除的光刻胶上,再次进行光刻,形成两倍结构。LELE和LFLF技术的特点就是流程简单,缺点是两次光刻之间存在对准问题,如果工艺不够严谨, 每次曝光的线宽偏差和两次曝光图形之间套刻误差将导致图形局部周期性的起伏。 图表 16:LELE原理

图表 17:套刻误差引起的周期移动

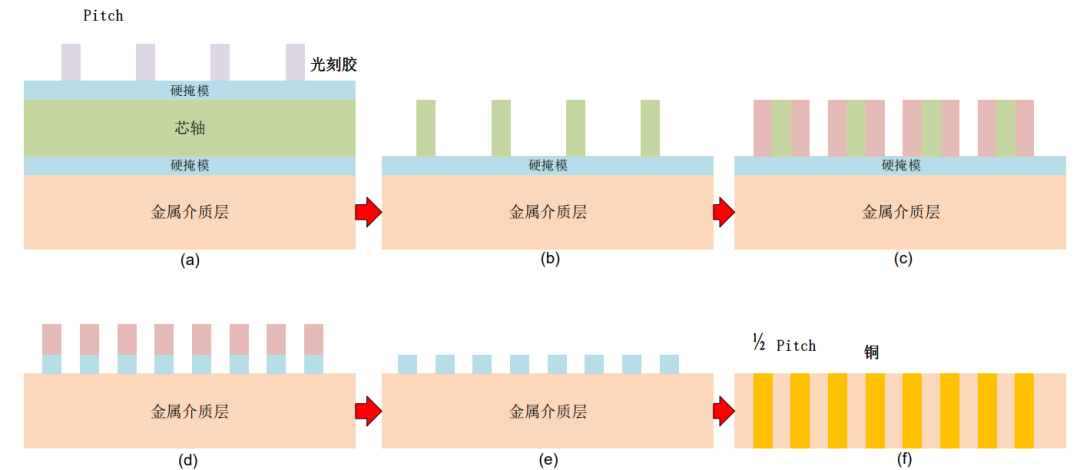

3) SADP又称侧墙图案转移,用沉积、刻蚀技术提高光刻精度:在晶圆上沉积金属介质层、硬掩膜材料和芯轴材料(牺牲层)旋涂光刻胶,曝光显影后留下所需图形并刻蚀核心芯轴在芯轴外围沉积一层间隔侧墙,侧墙的大小即互连线的线间距,要精确控制其均匀度保证互连线间距的均一性清除掉芯轴材料,仅留下侧壁,再一次刻蚀将侧壁图形转移到下层掩膜层侧墙清除,经过掩膜层修饰后的图形,经过再一次刻蚀后传递给金属介质层形成最终图形, 线宽仅为原来的1/2,SADP可以两次达到4倍精度。 总结:以沉积形成的侧墙为掩膜,在金属介质层上刻蚀形成最终图形。难点:工艺过程对侧壁沉积的厚度、刻蚀形貌的控制极其重要。

图表 18:SADP技术工艺流程

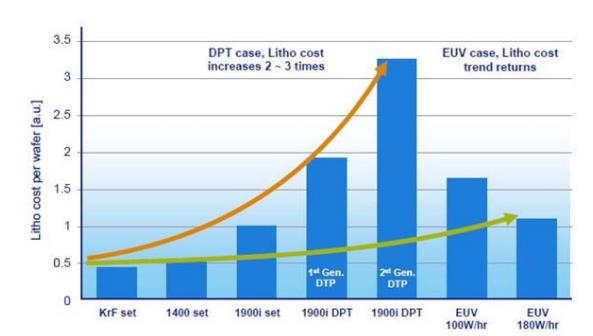

多重曝光可实现7nm制程但技术复杂成本高:多次LE或SADP可以实现7nm制程, 但多重曝光技术提高了对刻蚀、 沉积等工艺的技术要求并且增加了使用次数, 使晶圆光刻成本增加了2-3倍。

EUV可实现5nm以下制程且成本低:目前只有通过EUV能达到5nm及以下制程。此外, EUV的使用可以有效减少刻蚀、 沉积等工艺步骤, 工艺简单且光刻成本低。 图表 19:每片晶圆光刻成本

图表 20:对蚀刻和沉积的需求

从接触式到EUV, ASML成为绝对龙头 历史转折点:ASML凭借浸润式***垄断市场。 在浸润式光刻技术出现之前, 各厂商专注于157nm波长技术的研发, “浸润式微影技术” 被提出后, ASML开始与台积电合作开发浸润式***, 并于2007年推出浸润式***, 成功垄断市场。而同为光刻巨头的日本尼康、 日本佳能主推的157nm光源干式***被市场逐渐抛弃, 两家公司由盛转衰。

ASML一家独大, Nikon和Canon瓜分剩余市场。

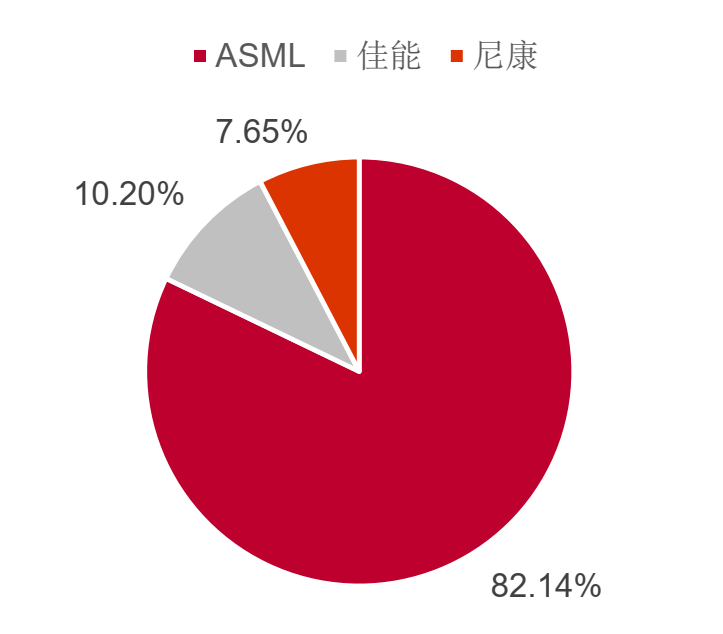

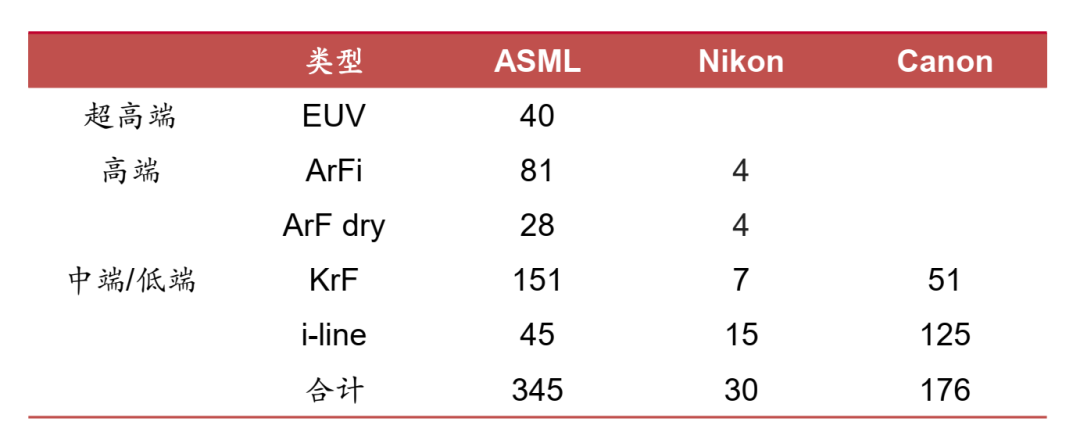

1) 全球***市场的主要竞争公司为ASML、Nikon和Canon。ASML在超高端***领域独占鳌头,旗下产品覆盖面最广。Canon***主要集中在i-line***, Nikon除EUV外均有涉及。 2) ***市场份额主要被ASML、Canon、Nikon包揽,从这三家的占比情况来看,2022年ASML占据82%,Canon占据10%,Nikon占据8%。 图表 21:2022年全球***TOP3市场份额占比情况

图表22:2022年全球半导体***TOP3厂商出货情况

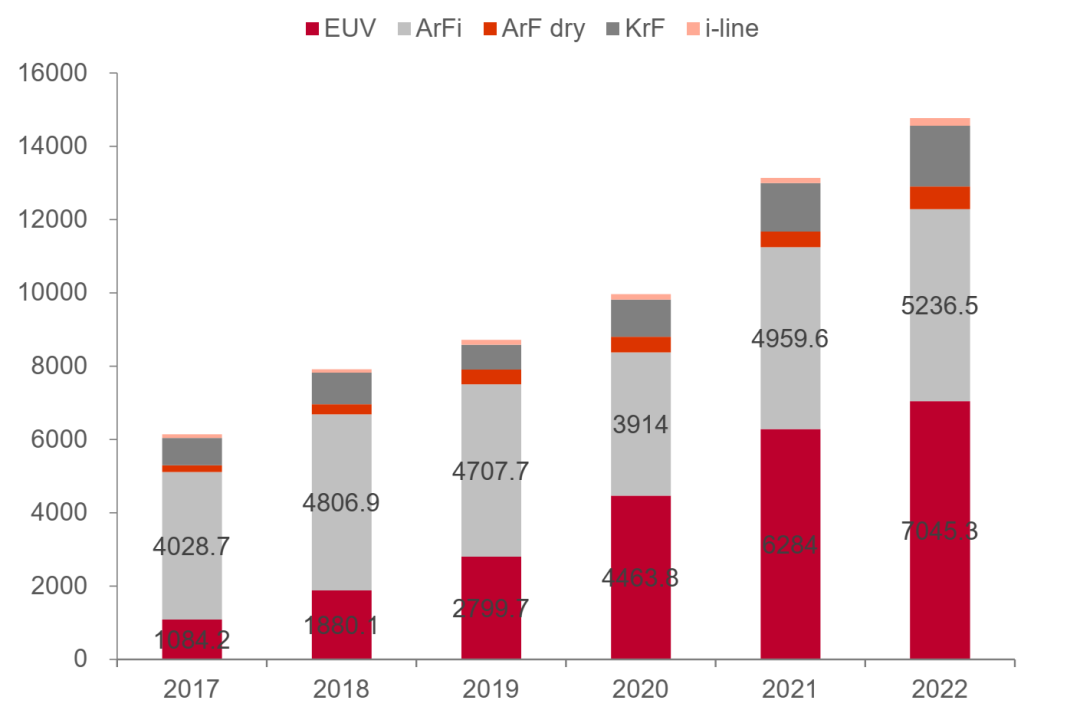

EUV***为ASML贡献最主要营收 EUV***为ASML贡献最主要营收。从ASML各产品销售额来看,2022年EUV***在ASML前道***产品销售额占比近50%,其次是ArFi的35%。EUV和ArFi 作为高端机型,单价较贵,为ASML贡献了主要营收增长动力。

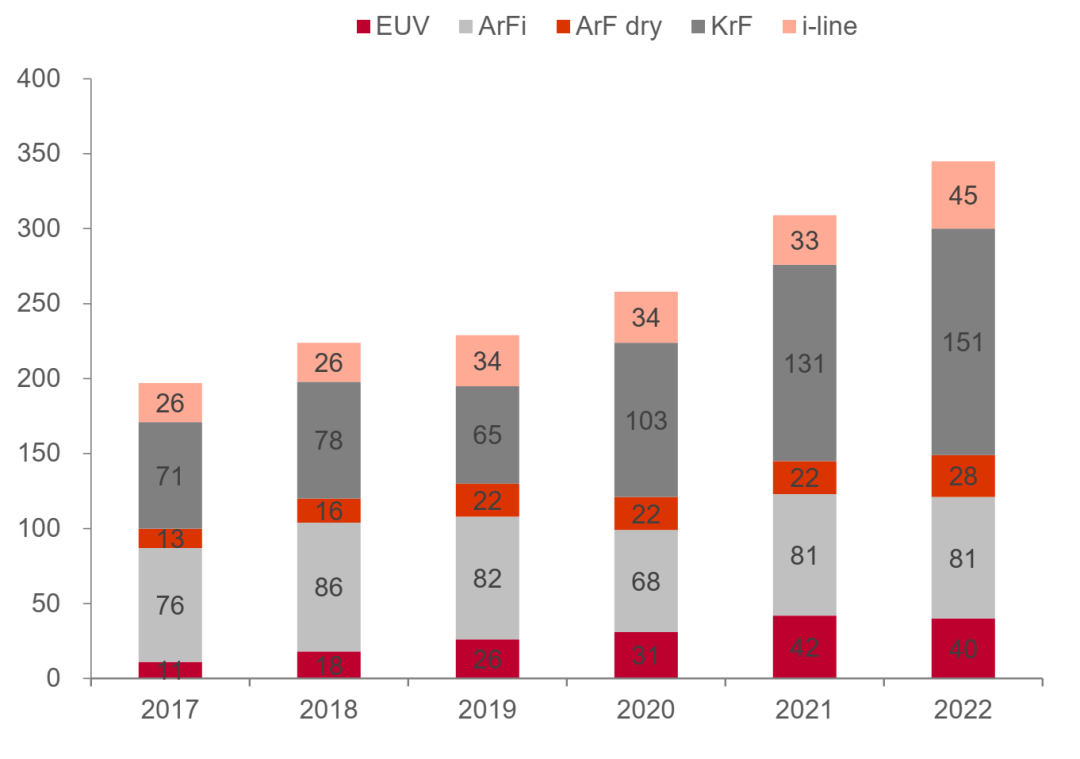

KrF出货量最多。从ASML各产品出货量来看,2022年KrF出货量最多,其次是ArFi,再到EUV。 图表23:ASML各类***销售额(百万欧元)

图表24:ASML各类***出货量(台)

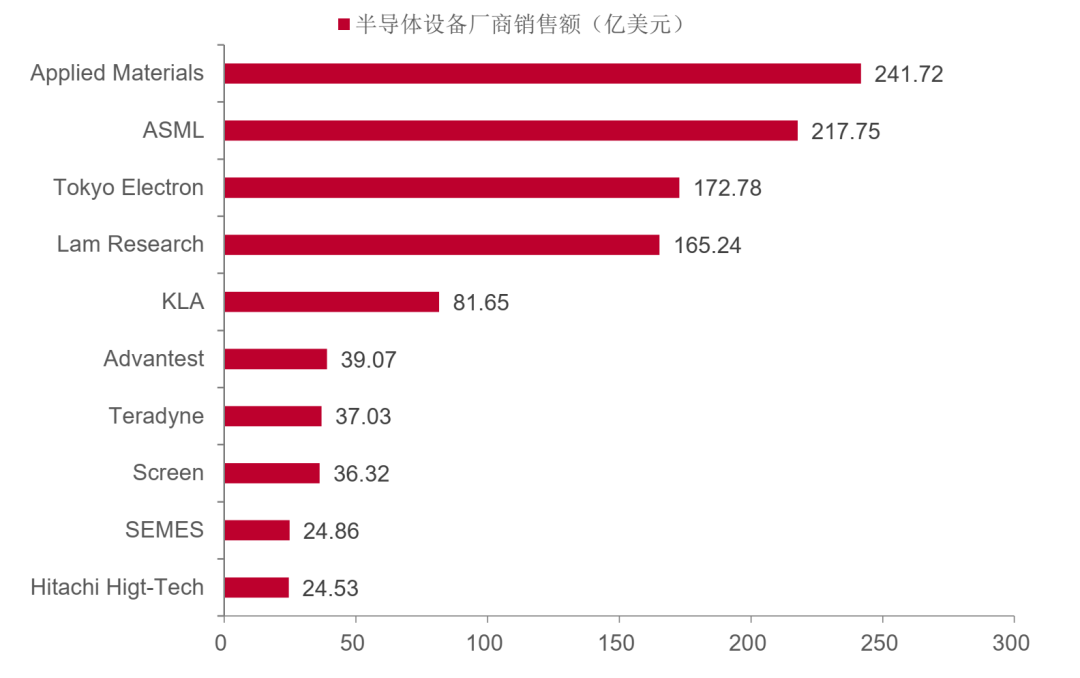

ASML凭借***在全球半导体设备厂商中位列第二

ASML凭借***在全球半导体设备厂商中位列第二。 根据统计数据, 在2021年全球半导体设备厂商销售额排行中, ASML位列第二, 销售额达到217.75亿美元, 仅次于美国应用材料。 图表25:2021年全球前十大半导体设备厂商(亿美元)

ASML是全球唯一的EUV供应商

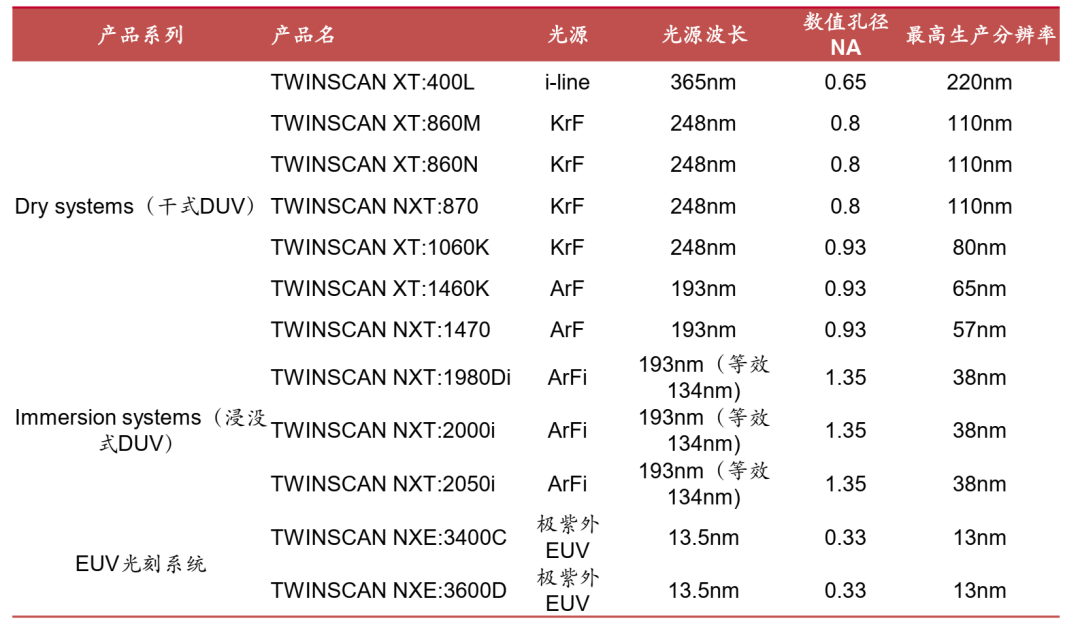

ASML***种类最齐全,是全球唯一可生产EUV***的公司,制程最小可达3nm。

1)从类型来看, ASML覆盖了干式DUV***、浸没式DUV***及EUV***,是全球唯一可生产EUV***的公司,具有绝对领先优势。

2)从光源来看, ASML覆盖了i-line、 KrF、 ArF和极紫外光源,最小光源波长为13.5nm。

3)从分辨率来看, ASML覆盖了220nm、 110nm、 80nm、 38nm、 13nm等节点, EUV***是目前全球分辨率最小的***,经过

多重曝光等工艺叠加制程可达到5nm/3nm。 图表26:ASML半导体***产品参数

图表27:ASML***发展历程

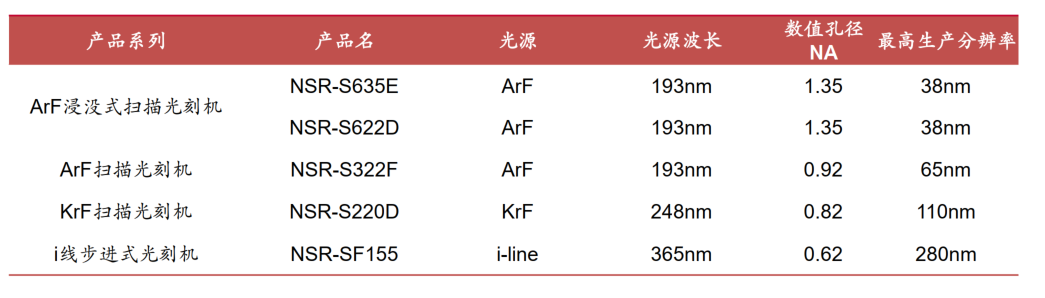

Nikon***集中于DUV

Nikon***集中于DUV,是除了ASML以外唯一可以生产浸没式***的厂商。 1)从类型来看, Nikon具有干式DUV***、浸没式DUV***,是除了ASML以外唯一可以生产浸没式***的厂商。 2)从光源来看, Nikon覆盖了i-line、 KrF、 ArF光源,最小光源波长为193nm。

3)从分辨率来看,Nikon覆盖了280nm、 110nm、 65nm、 38nm等节点。 图表 28:Nikon半导体***产品参数

数据来源:***行业报告,中泰证券研究所

Canon***集中于低端类型

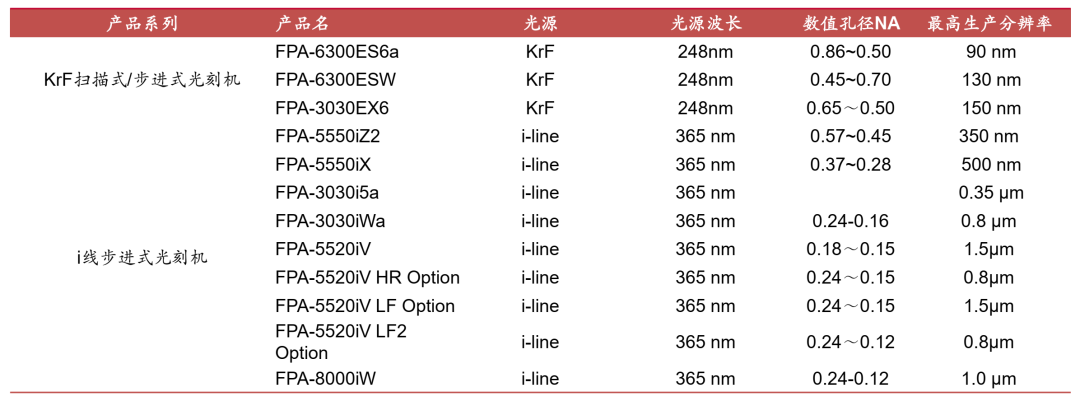

Canon半导体***主要集中于低端类型。 1)从类型来看, Canon具有低端半导体的i-line和KrF***,未覆盖EUV、 ArFi(浸没式)、 ArF等机型。 2)从光源来看, Canon覆盖了i-line、 KrF光源,最小光源波长为248nm。 3)从分辨率来看, Canon覆盖了1.5微米、 0.8微米、 350nm、 90nm等节点。 图表 29:Canon半导体***产品参数

数据来源:***行业报告,中泰证券研究所

***:多个先进系统组合,核心零部件被海外厂商垄断

***:人类科技之巅

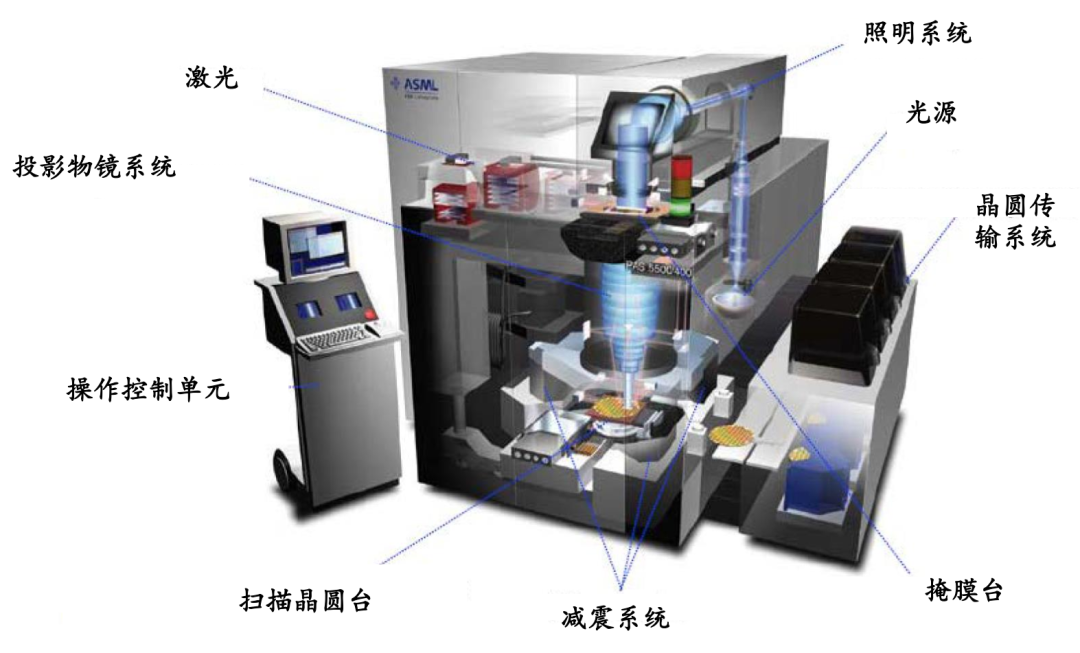

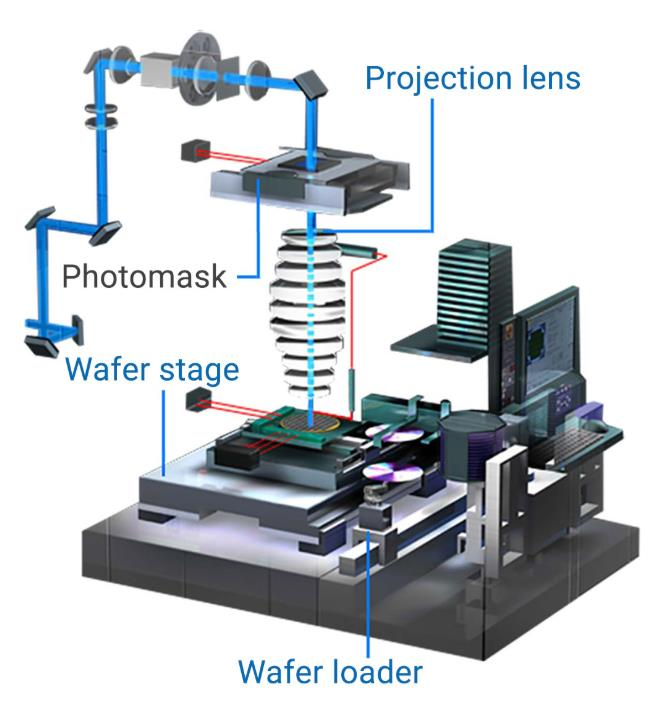

***是一种投影曝光系统:***由光源、 照明系统、 物镜、 工件台等部件组装而成。在芯片制作中, ***会投射光束, 穿过印有图案的光掩膜版及光学镜片, 将线路图曝光在带有光感涂层的硅晶圆上。通过蚀刻曝光或未受曝光的部分来形成沟槽, 再进行沉积、 蚀刻等工艺形成线路。

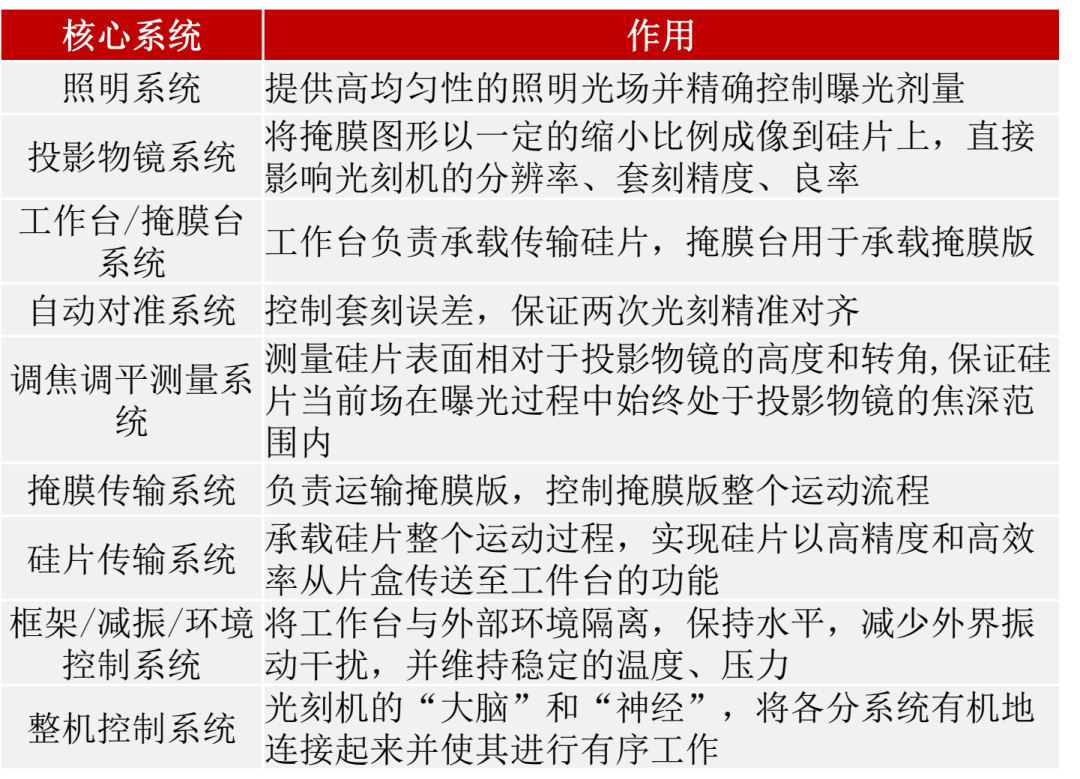

***的三大核心系统:光源系统、 光学镜头、 双工作台系统。 图表 30:***总体结构

图表 31:***核心系统介绍

图表 32:***结构

图表 33:***核心部件结构

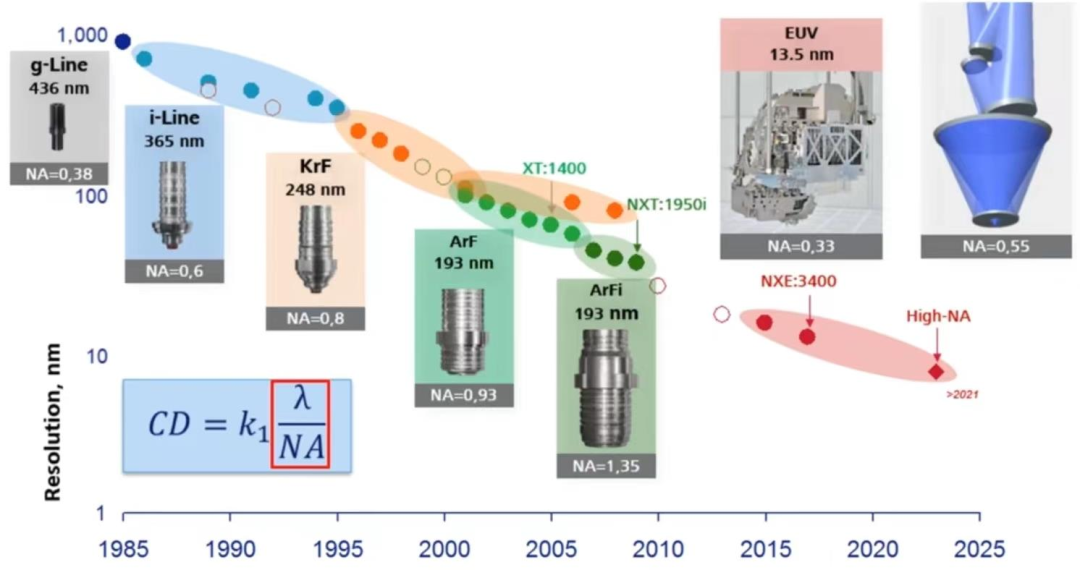

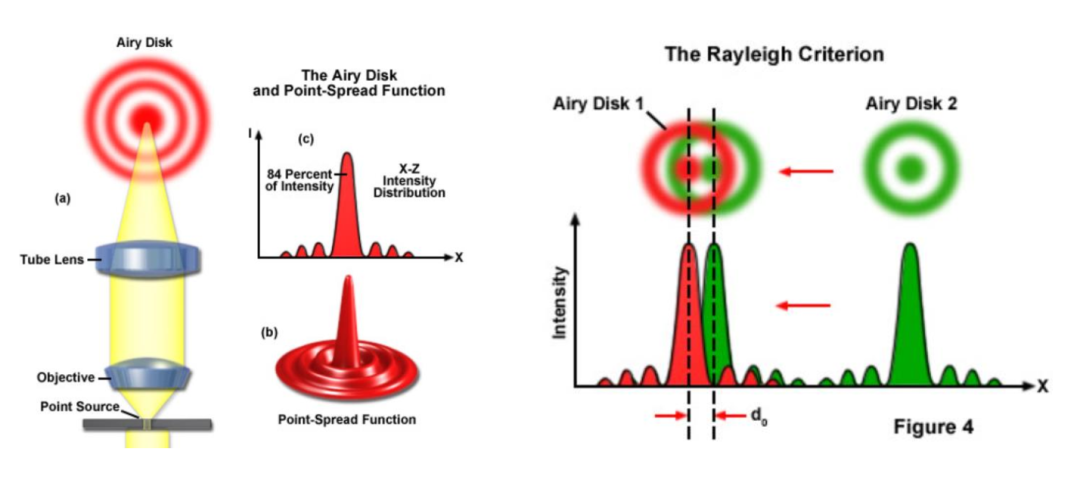

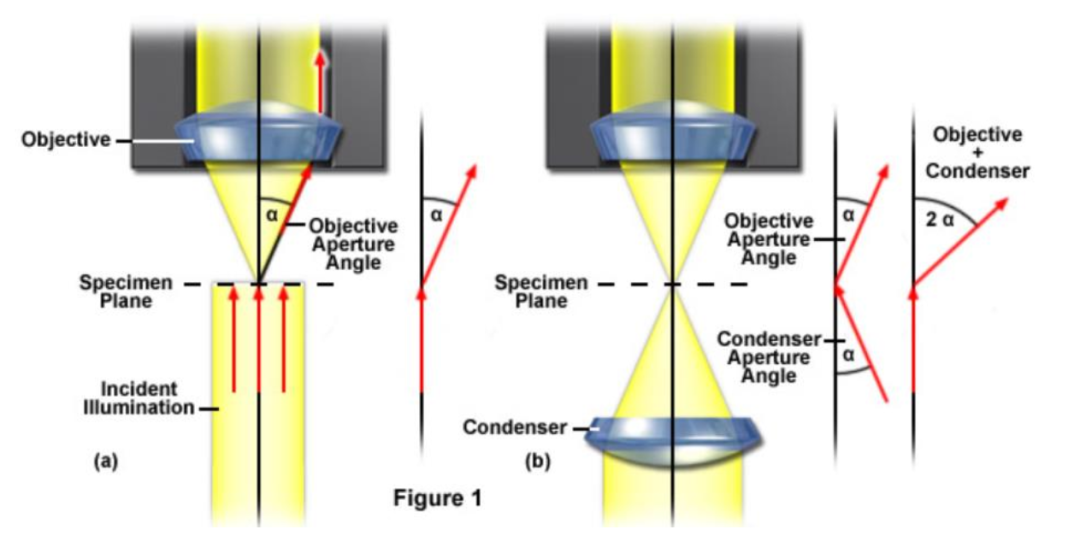

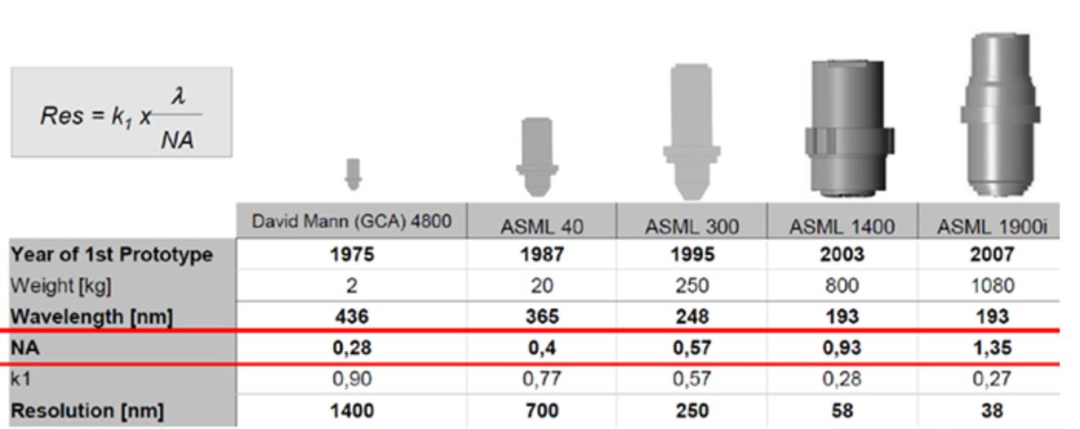

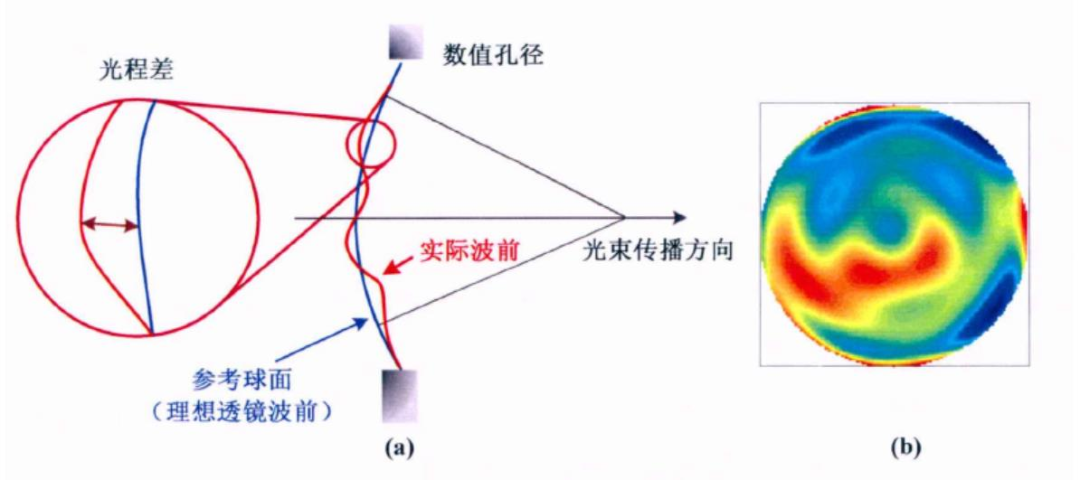

***分辨率由光源波长、数值孔径、 光刻工艺因子决定 光刻分辨率是光刻曝光系统最重要的技术指标,由光源波长、数值孔径、光刻工艺因子决定。根据瑞利准则, 分辨率公式为R= k1 * λ/NA,λ 代表光源波长,NA代表物镜的数值孔径,k1代表与光刻工艺因子。数值孔径指透镜与被检物体之间介质的折射率(n)和孔径角(2a) 半数的正弦之乘积。公式为:NA=n*sin α 。n 为投影物镜系统像方介质的折射率,α为投影物镜像方半孔径角。孔径角又称“镜口角” ,是透镜光轴上的物体点与物镜前透镜的有效直径所形成的角度。孔径角越大,进入透镜的光通量就越大,它与透镜的有效直径成正比,与焦点的距离成反比。

瑞利准则指衍射极限系统中的分辨率极限。理想的成像系统,一个点所成的像是一个完美的点,但实际光学系统中的透镜具有一定的孔径大小, 由此导致所成的像不是一个点, 而是一个艾里斑。对于两个距离较近的点, 所成的光斑也距离比较近。能够区分两个光斑的最小距离, 就是分辨率。当一个艾里斑的中心与另一个艾里斑的第一极小值重合时,达到极限点,该极限被称为瑞利准则。 图表 34:分辨率极限示意图

图表 35:孔径角示意图

三方面提高***分辨率:增大数值孔径、缩短波长、减小光刻工艺因子。分辨率指投影光学系统在晶圆上可实现的最小线宽。***分辨率由光源波长、数值孔径、光刻工艺因子决定。因此可以从以下三方面提高分辨率:1)增大投影光刻物镜的数值孔径;2)缩短曝光波长;3)减小光刻工艺因子。

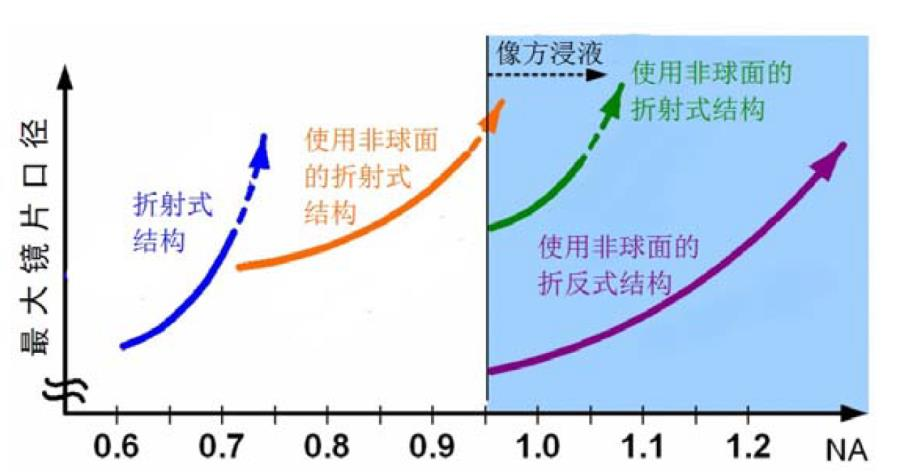

1) 增大投影光刻物镜的数值孔径:一方面可以改进投影式透镜系统来增大入射角,另一方面可以采用折射率高的介质-浸润式。非球面的使用能够在不增加独立像差数的前提下,增加自变量的个数,有利于改善像质,同时在同等约束条件下,减少了光学元件的数量。非球面的应用使物镜NA可以增加到0.9,接近物理极限(干式光刻);引入浸没式技术后,物镜NA可以增加到 1.1以上(浸没式光刻);加入反射镜组成折反式结构理论上物镜NA可到 1.35 (极限值)。趋势为(干式) 球面镜→非球面

镜→(浸没式)非球面镜→折返式。

2)缩短曝光波长:由于晶体管越做越小,元件线路越来越密集,***需要达到更高的分辨率,因此必须要寻找波长越来越短的光源。 图表 36:数值孔径变化趋势

图表 37:提高数值孔径的方法

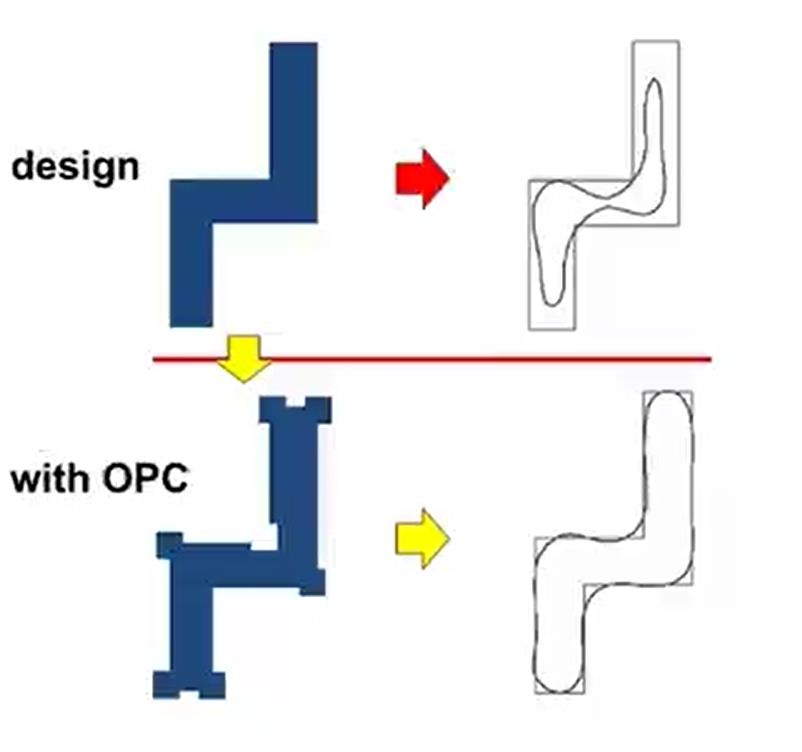

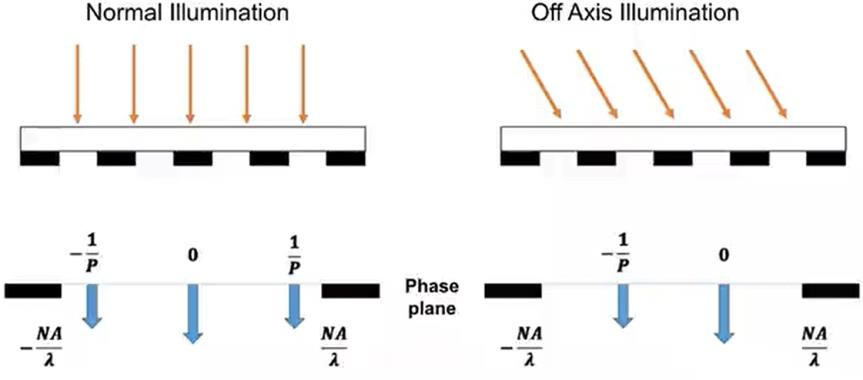

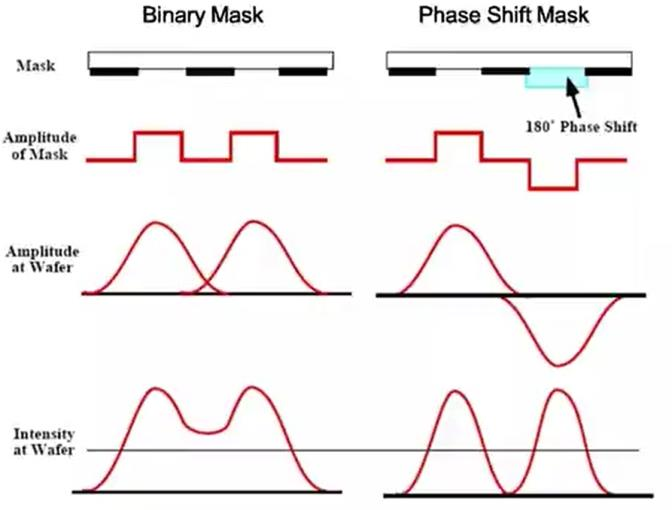

3) 减小光刻工艺因子: 计算光刻OPC——在掩膜上增加辅助结构来消除图像失真,实现分辨率的提高;离轴照明OAI ——通过采用特殊光源让正入射方式光变成斜入射方式,目的是在同等数值孔径内容纳更多的高阶光,从而曝光更小尺寸结构,提高分辨率;相移掩膜PSM ——当两个光源进行成像时会在重合部分产生干涉效应,使光强增大,导致两个光源不能有效地区分开,如果通过改变掩膜结构在其中一个光源处采用180度相移,这两处光源产生的光会产生相位相消,光强相消,两个光源可以区分开,提高分辨率。

工艺因子已突破理论极限:理论上对于单次曝光 k1 的最小极限约为 0.25,通过组合使用OPC、多重图形等分辨率增强技术,光刻工艺因子已突破其理论极限0.25。 图表 38:光刻OPC

图表 39:离轴照明OAI

图表 40:相移掩膜PSM

数据来源:***行业报告,中泰证券研究所

光源系统:能量的来源,光刻工艺的首要决定项

光源是***核心系统之一, ***的工艺能力首先取决于其光源的波长。

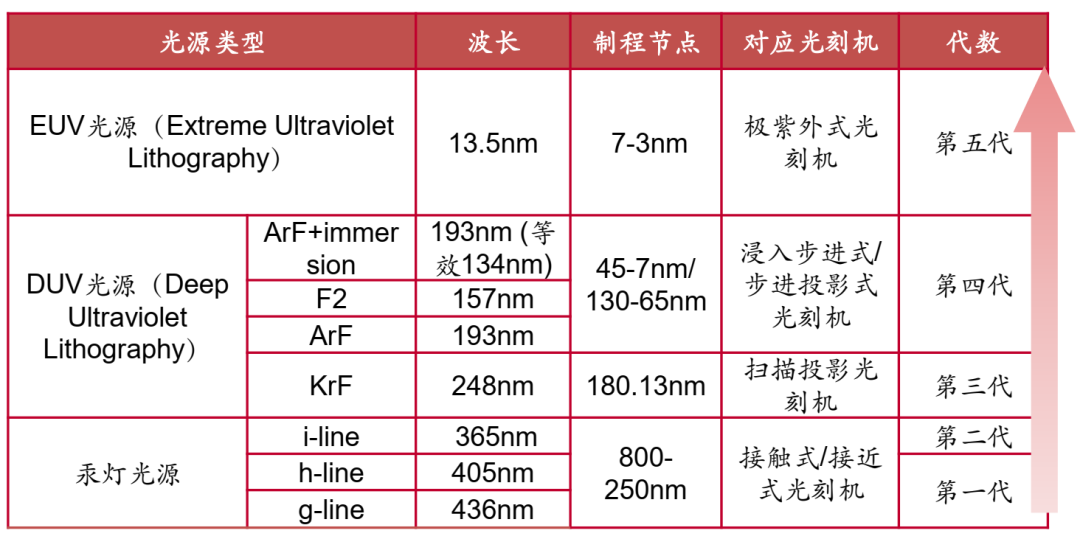

光源分为汞灯产生的紫外光、 深紫外光、 极紫外光, 目前光源波长已发展到13.5nm:为了追求更小的芯片制程, 需要光源波长不断变短, 最早***的光源采用高压汞灯产生的紫外光源,高压汞灯可产生436nm(g-line 、365nm( i-line ) 波长紫外光随后,业界选用了准分子激光器产生的深紫外光源, 深紫外光激光(DUV laser) 可达KrF(248nm)、ArF(193nm)、F2(157nm)制程突破7nm以下时,需要极紫外光激光(EUV laser) ,可达13.5nm极短波长的光源, 该光源无法从激光器中产生, 须由高能激光轰击金属锡激发的等离子体而产生。 图表41:光源波长发展历程

图表42:光谱图

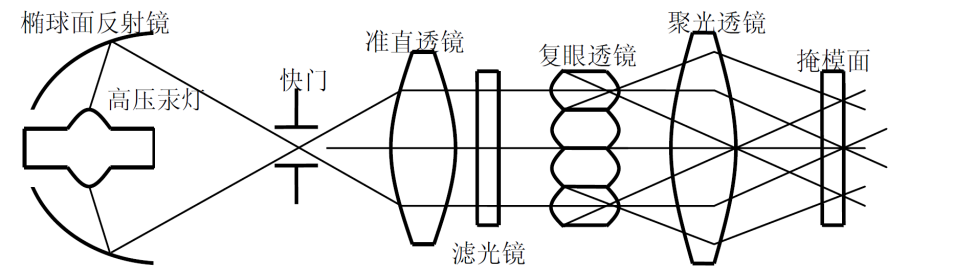

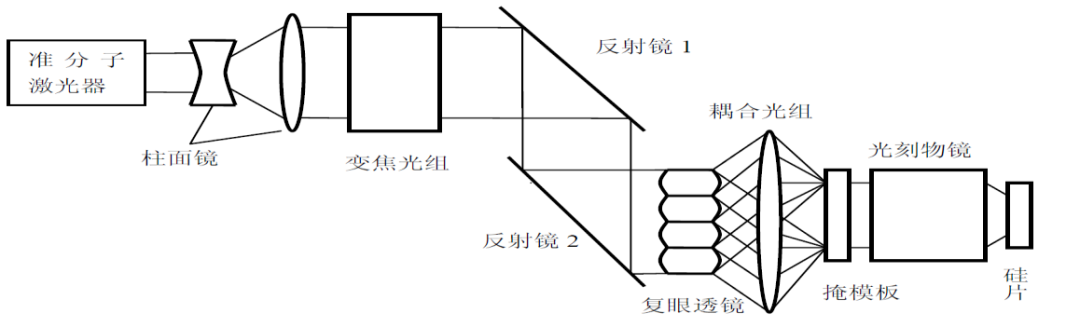

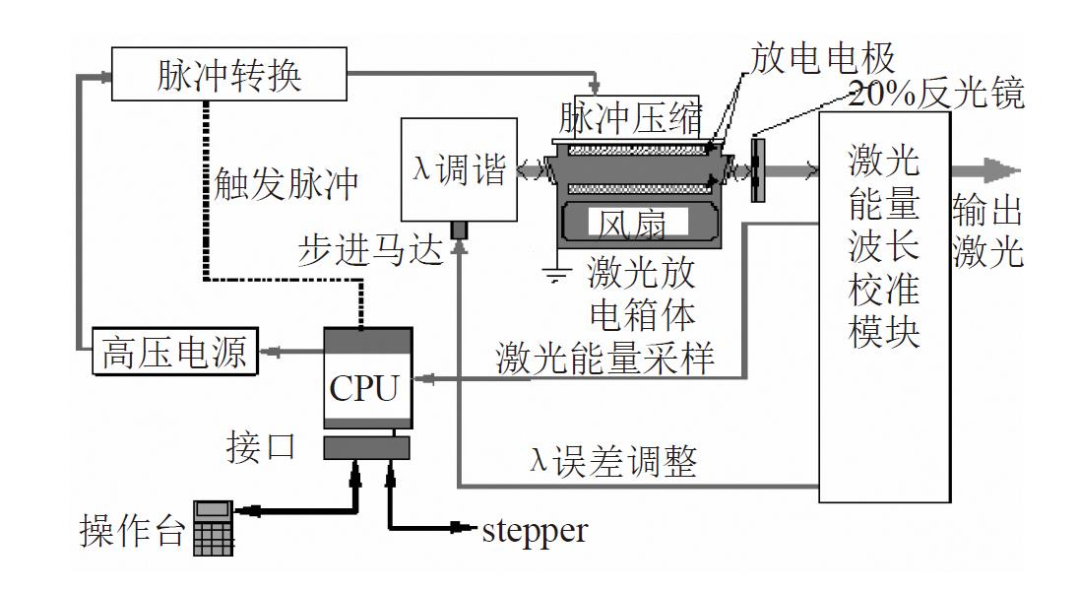

光刻光源系统不断发展, 从高压汞灯光刻光源到深紫外光光源再到极紫外光光源。 1) 高压汞灯:一种气体放电电光源, 汞蒸气被能量激发, 汞原子最外层电子受到激发从而跃迁, 落回后放出光子。放电管内充有启动用的氩气和放电用的汞。 2) 深紫外光光源: 一般采用准分子激光器作为光源。准分子激光光源工作介质一般为稀有气体及卤素气体, 并充入惰性气体作为缓冲剂, 工作气体受到放电激励, 在激发态形成短暂存在的“准分子” , 准分子受激辐射跃迁, 形成紫外激光输出。准分子激光器常在输出能量、 波长、 线宽、 稳定性等方面远超越前期的汞灯光源。 图表43:高压汞灯光刻光源系统结构图

图表44:紫外激光器照明系统结构图

图表45:Cymer准分子激光器的工作原理

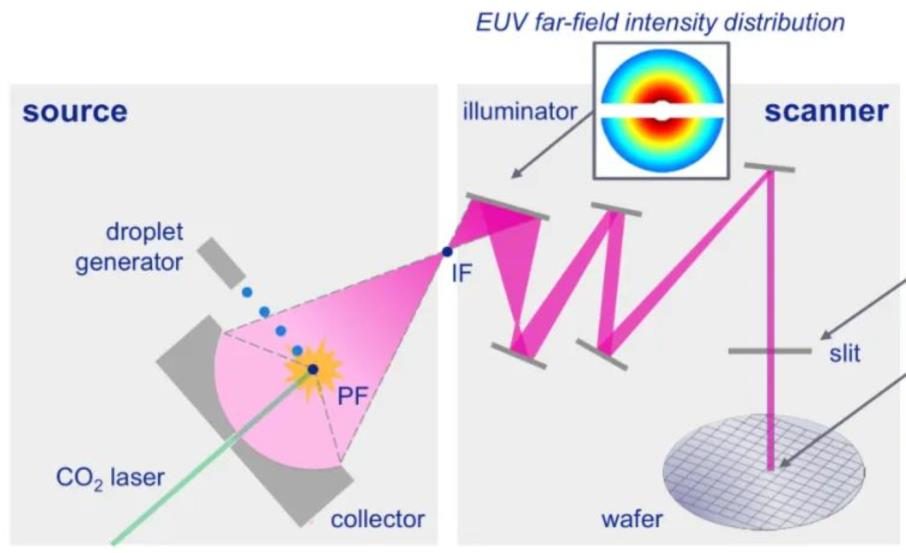

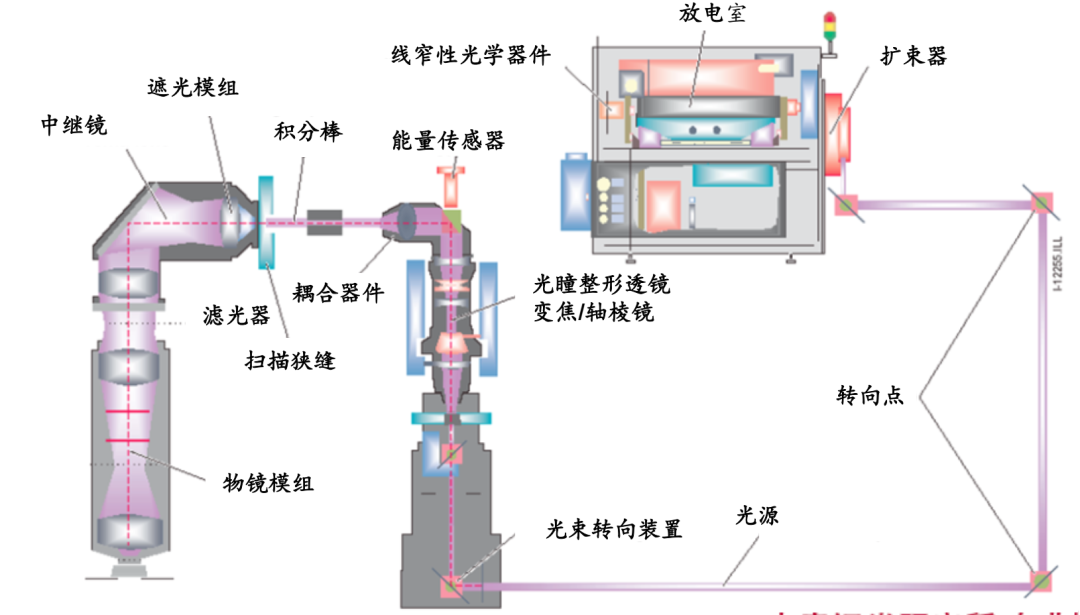

3) 极紫外光光源: 极紫外光光源由光的产生、 光的收集、 光谱的纯化与均匀化三大单元组成。工作元器件包括大功率CO2激光器、 多层涂层镜、 负载、 光收集器、 掩膜版等。

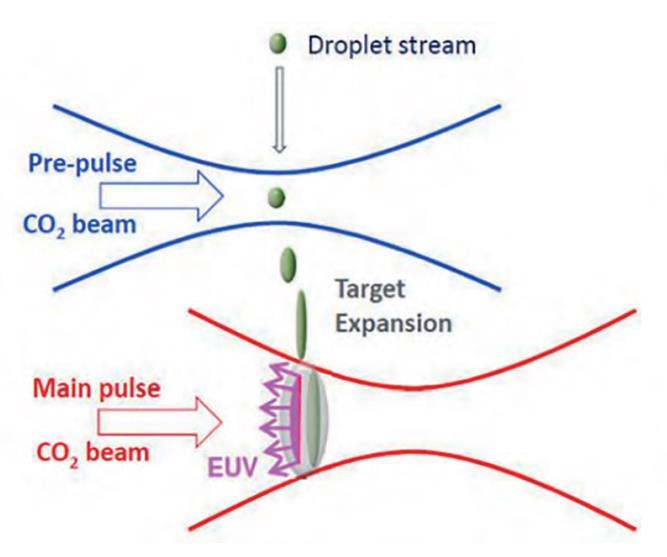

极紫外光光源原理:高功率激光击打金属锡,产生等离子体,辐射出极紫外光。将高功率的二氧化碳激光打在直径为30微米的锡液滴上,通过高功率激光蒸发锡滴, 把融化的锡从高处以每秒5万次的频率滴下,每一滴锡20微米的大小, 瞄准每一滴锡滴,以CO2激光器产生的高能激光击中并产生等离子体,从而发出13.5nm波长的EUV光。实际上激光会发出两个脉冲——预脉冲和主脉冲。预脉冲首先击中锡珠, 将其变成正确的形状,然后主脉冲将压扁的锡珠转化为等离子体,发射出EUV光。 图表46:EUV光源系统结构图

图表47:EUV光源双脉冲方案

图表48:EUV光产生的过程

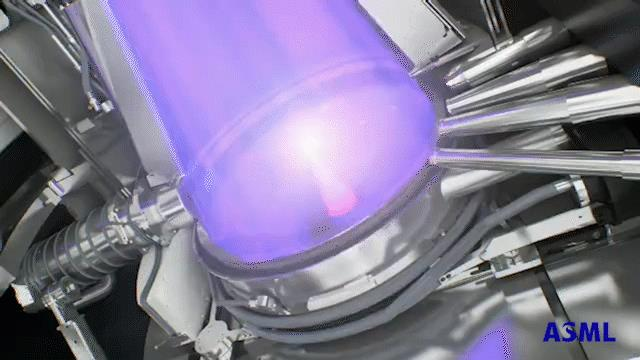

EUV ***技术难点主要是光源功率高:为满足极紫外光刻需求,光源应具有以下性能: (1)光源功率达250W, 且功率波动小;(2)较窄的激光线宽,具有频率噪声和很小的相对强度噪声,减少光学损耗;(3) 较高的系统效率。光源转化率最终要达到250w以上的功率,因此激光器的平均功率要达到20kW。为了让激光束以极大的功率稳定传输,系统非常复杂性。EUV 激光系统由大约 45 万个零件组成,重约 17 吨。从种子光发生器到锡珠有 500 多米的光路,对所有零部件的要求非常苛刻。

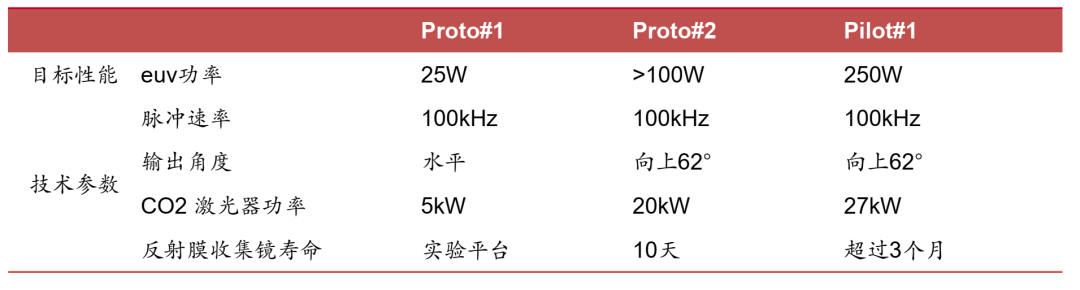

Gigaphoton( EUV光源供应商之一) 激光器功率达27kW:Gigaphoton 成立以来一直为 ASML、 Nikon和Canon提供激光光源。共设计三款EUV光源,分别为Proto#1、Proto#12、Pilot#1, 其中Pilot#1为商业化应用的产品,激光器功率为27kw, 输出功率达到250W。目前EUV光源只有两家公司能够生产:一家是美国Cymer, 另外一家是日本Gigaphoton。 图表49:Gigaphoton 公司 EUV 光源产品参数

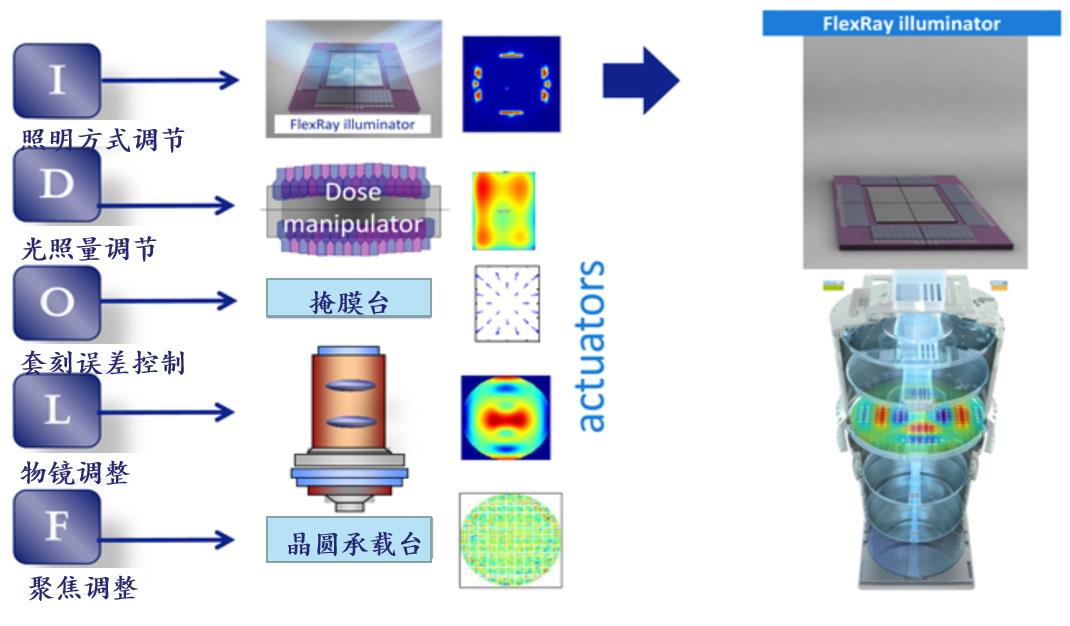

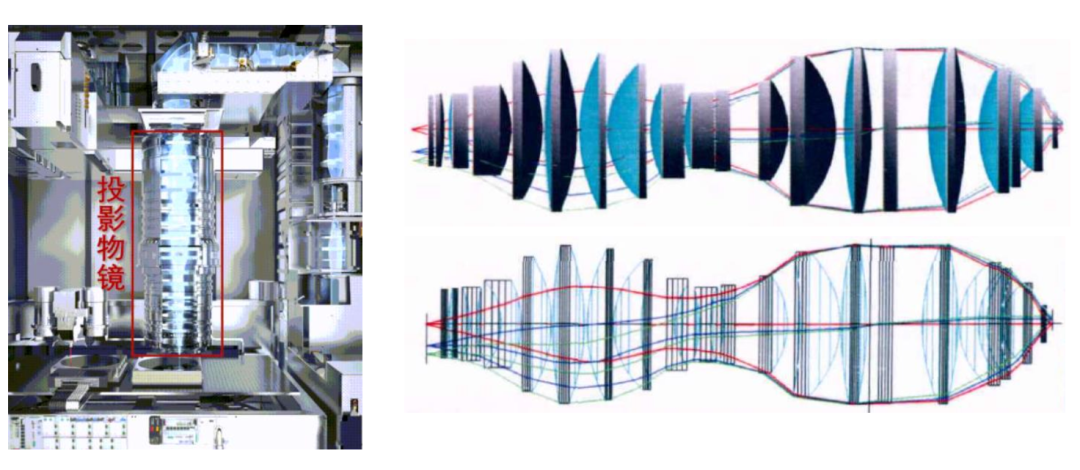

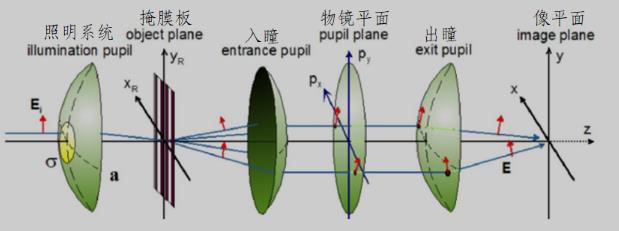

曝光系统:照明系统+投影物镜 曝光系统:曝光系统包含照明系统( 光源加工) 和投影物镜( 高分辨成像) , 是***中最昂贵最复杂的部件之一。物镜的性能决定了***的线宽、 套刻精度, 是***的核心部件, 其技术水平很大程度上代表了***的技术水平。 图表49:***照明与投影物镜系统的工作流程图

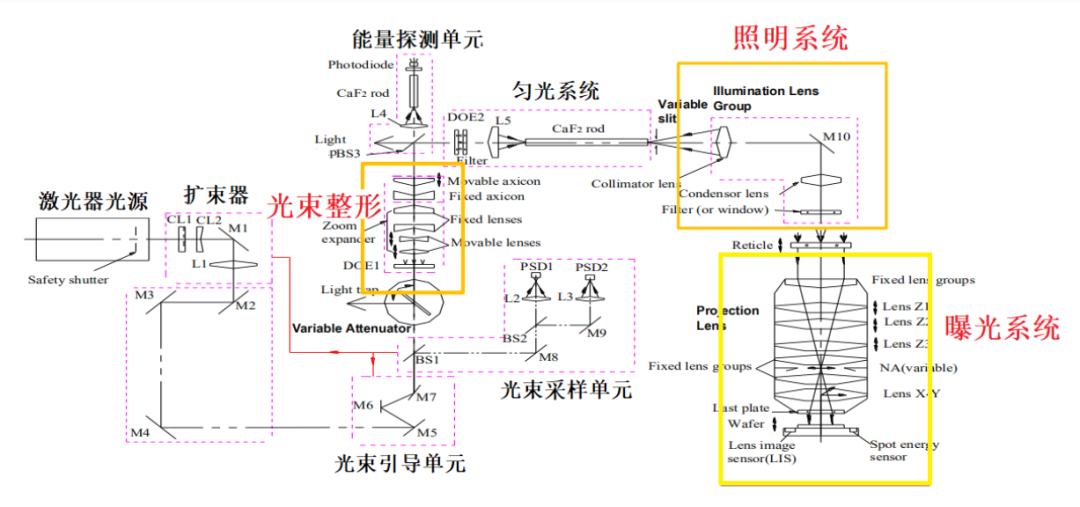

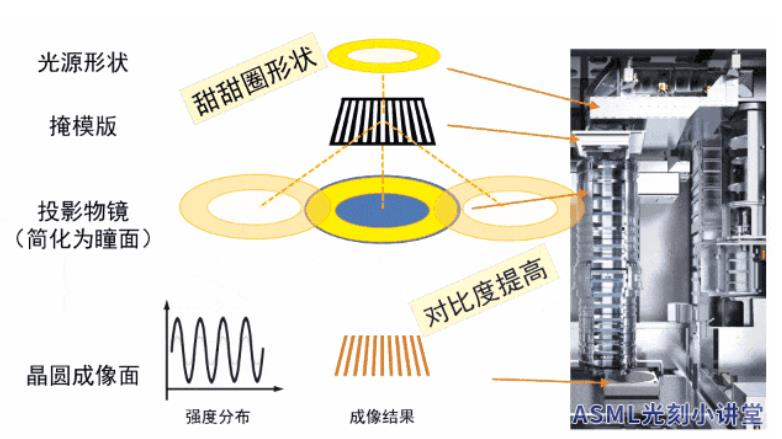

照明系统:光源高质量加工的关键 照明系统为投影物镜成像提供特定光线角谱和强度分布的照明光场。照明系统位于光源与投影物镜之间, 是复杂的非成像光学系统。照明系统的主要功能是为投影物镜成像提供特定光线角谱和强度分布的照明光场。照明系统包括光束处理、光瞳整形、 能量探测、 光场匀化、 中继成像和偏振照明等单元。 图表50:光学系统原理

照明系统组成部件:1)光束处理单元:与光源相连, 主要实现光束扩束、 光束传输、 光束稳定和透过率控制等功能,其中光束稳定由光束监测和光束转向两部分组成。2)光瞳整形单元:***需要针对不同的掩膜结构采用不同的照明模式以增强光刻分辨力,提高成像对比度。光瞳整形单元通过光学元件调制激光束的强度或相位分布,实现多种照明模式。3)光场匀化单元:用于生成特定强度分布的照明光场。引入透射式复眼微透镜阵列, 每个微透镜将扩束准直后的光源分割成多个子光源, 每个子光源经过科勒照明镜组后在掩膜面叠加,从而实现高均匀性的照明光场。4)中继镜:在掩膜面上形成严格的光束强度均匀的照明区域并将中间的平面精确成像在掩膜版平面。 图表51:照明系统结构

照明系统技术难点:为了使光能在晶圆上完美成像,需要进行高质量加工。

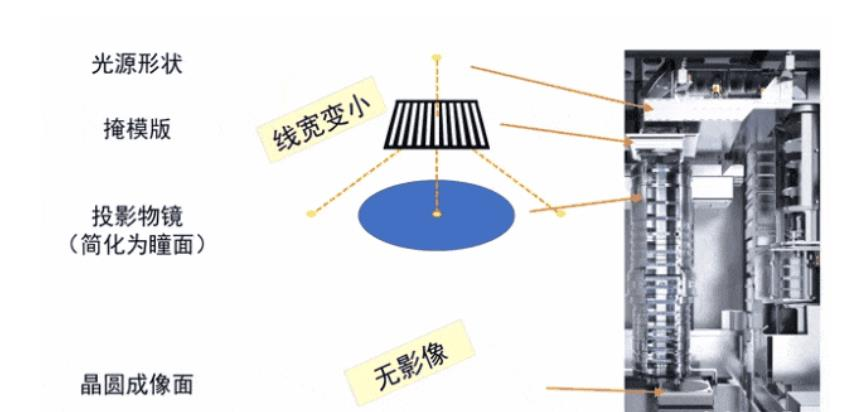

1) 提升光均匀度:光刻要以来回扫描的方式成像, 这束条形光的任何位置能量都需一致。需要通过镜子进行多次反射, 提升光的均匀度。 2)控制扫描条形光的开合:晶圆上曝光单元的所有位置需要接受等量的光,因此扫描的条形光必须是能开合的。 3)调节光形状, 需要用到光瞳整形技术:不同的照明方式,比如圆形、环形、二级、四级光源下,***分辨率不同。例如:光穿过掩膜版上的图案时会产生衍射效应, 线宽越小,衍射角度越大,1阶衍射光超过投影物镜外就无法成像。如果将点光的形状改成环状光或其他形状, 1阶衍射光就可以被收进物镜且图像对比度清晰。 图表52:衍射光无法成像

图表53:环形光成像

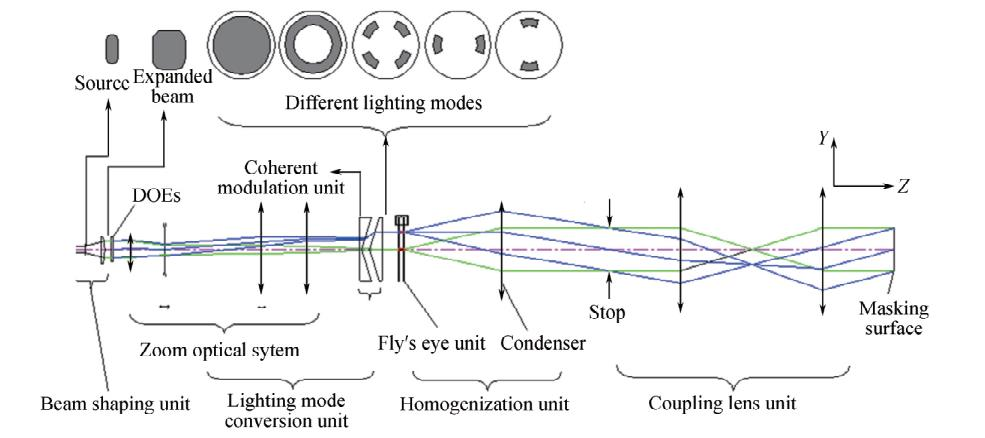

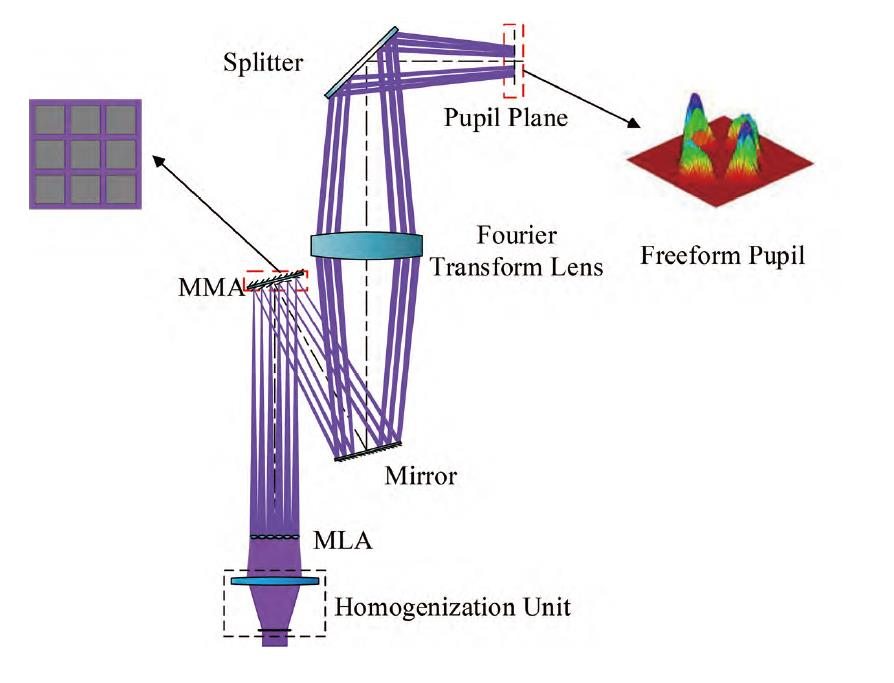

光瞳整形单元是照明系统中技术难度较大的部件, 主要技术有:基于衍射光学元件(DOE) 的光瞳整形技术和基于微反射镜阵列(MMA) 的自由光瞳整形技术。

衍射光学元件(DOE) 的光瞳整形:光瞳整形单元主要包括衍射光学元件、变焦距傅里叶变换镜组、锥形镜组和光瞳补偿器。衍射光学元件用于实现照明光瞳的角向调制, 傅里叶变换镜组、锥形镜组用于照明光瞳的径向调制。缺点:1个衍射光学元件只能实现1种照明模式。

微反射镜阵列(MMA)的自由光瞳整形:主要由能量均衡组件、 光束分割组件、 微反射镜阵列和傅里叶变换镜组组成。核心器件是微反射镜阵列, 由数千个二维转角连续可调的微反射镜组成, 通过调整微反射镜阵列的角位置分布可实现任意照明模式, ASML先进机型中较多使用自由光瞳整形技术。 图表54:基于衍射光学元件的光瞳整形技术

图表55:基于微反射镜阵列的光瞳整形技术

投影物镜系统:精准成像,对线宽起重要作用

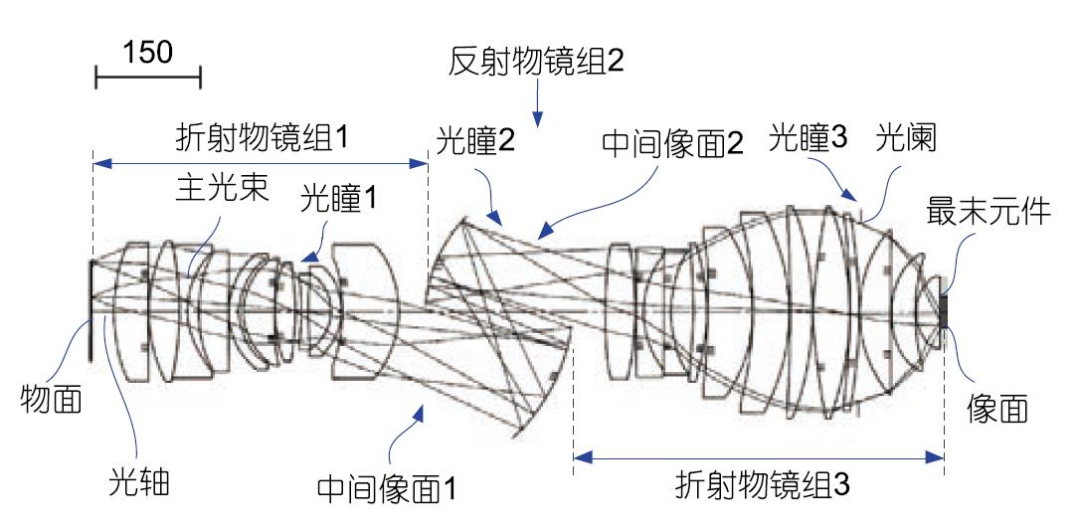

投影物镜是精准成像的关键:投影物镜要将照明模组发射出的1阶衍射光收进物镜内,再把掩膜版上的电路图案缩小,聚焦成像在晶圆上,并且还要补偿光学误差。投影物镜主要由多枚镜片组成。随着分辨率要求不断提高, ***投影物镜结构越来越复杂,对光学材料、光学加工、光学镀膜等要求达到目前工业水平的极限, 是***中技术壁垒最高的零部件之一。

投影物镜的结构型分为折射式和折反式:1) 折射式:光学元件旋转对称并沿着同一个光轴对准, 视场位于光轴中央, 结构简单易于装调;2) 折反式(NA>1.1) :反射镜有着正光焦度和负值场曲, 不依赖传统“腰肚” 结构, 使用较少数量和较小口径的光学元件满足对场曲的校正在一定物镜尺寸限制内实现更大的NA。

物镜特点是直径大、镜片多、镜片可动:1)物镜直径大:ASML DUV***中的先进机种的投影物镜直径大于40厘米,增加投影物镜的直径可以提高数值孔径, 进而提高***分辨率。2)多片透镜组合:ASML DUV***投影物镜的高度超过1米,镜片数量超过15片。和相机一样,单个透镜的光学特性会导致图像失真, 需要组合透镜来修正图像形变。3)可动镜片:用运动着的镜片来消除镜头组装及光刻生产等过程中所产生的各种像差。可动镜片覆盖了垂直修正、倾斜修正和多向修正。 图表56:典型折射式投影物镜示意图

图表57:折反式投影物镜示意图

投影物镜技术难点:像差调节要求高、工艺精密。

1)像差调节要求高:波像差是实际波面与理想波面之间发生的偏离:光在介质中传播的时候,从物点发出的同心光束相当于球面波,球面波经过光学系统的时候,其曲率发生改变。如果是理想的光学系统,它会形成另外一个球面波。但在实际的光学系统,会受到投影物镜自身材料、特性、厚度、粗糙度、环境等因素的影响,经过投影物镜的出射,波面会发生变形。实际波面与理想波面之间发生的偏离就是波像差。波像差直接影响***成像质量、光刻分辨率,因此***的投影物镜系统需要对像差像差进行校正。 图表58:像差示意图

图表59:***成像过程

1) 像差调节要求高:

为了更好的调节像差, 物镜发展趋势为:从“双腰”到“单腰” 、 引入非球面镜片与反射式镜片。

“双腰” 到“单腰” :为了实现场曲的矫正,投影物镜采用的都是“腰肚” 式结构。最初系统的结构依次为正组, 负组,正组,负组,正组,形成“腰肚”,随着非球面数量的增加,双腰结构结构逐渐从“ 1.5腰结构” 变为“单腰结构” ,光学元件数减少。

引入非球面镜片:NA大于0.75时,需引入非球面镜片。

原因:一方面, 如果采用全球面结构形式,光学元件的孔径尺寸及体积随着 NA 的增加急剧增加;另一方面, 物镜投影物镜 NA 增加,分辨率增强,成像质量要求也进一步提高,采用全球面光学系统,设计复杂度随之增加。

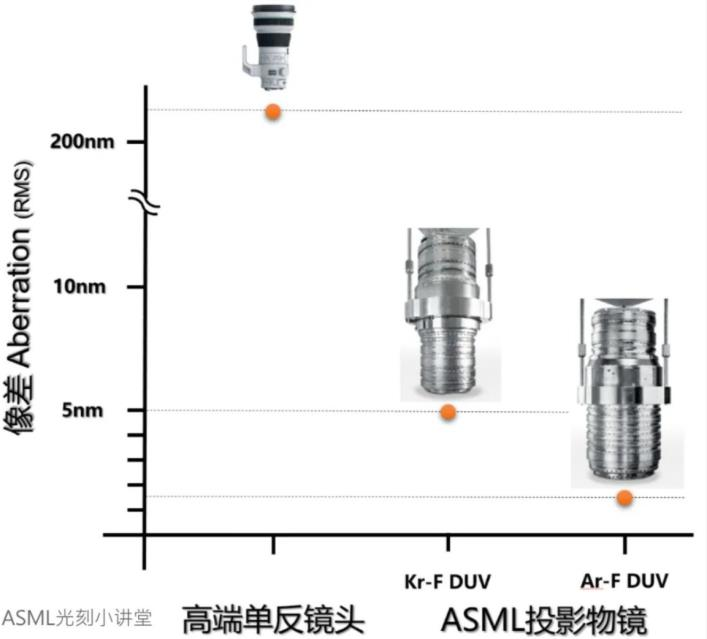

引入反射式镜片:NA 大于1.1时, 需采用折反式投影光刻物镜。加入凹面反射元件。凹面有正的光焦度,对场曲的贡献是负值, 凹面镜能较好的矫正场曲。 ASML DUV高端投影物镜的像差 ≤2nm。高端单反镜头像差最多达到200+nm,而ASML DUV高端投影物镜的像差 ≤2nm,因此***镜片的平整度要求非常高,同时物镜内还需要可动镜片,垂直、倾斜和多向修正镜头组装及生产过程中产生的像差,还要尽量消除光损失产生的热量。

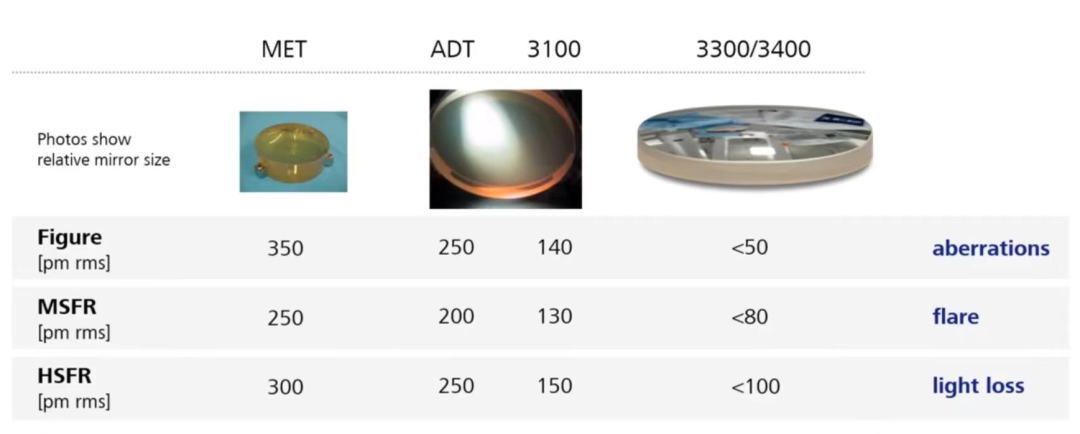

2)工艺精密:***所要求的镜面光洁度非常高,需要采用精度最高的打磨机和最细的镜头磨料,此外还需要顶级的技术工人。在光学镜头的生产工序中,仅CCOS的抛光就有小磨头抛光、应力盘抛光、磁流变抛光、离子束抛光等超精密抛光高难度工序。蔡司生产的最新一代EUV***反射镜最大直径1.2米,面形精度峰谷值0.12纳米, 表面粗糙度20皮米(0.02纳米),达到了原子级别的平坦。 图表60:投影物镜与高端单反镜头像素差

图表61:蔡司物镜参数

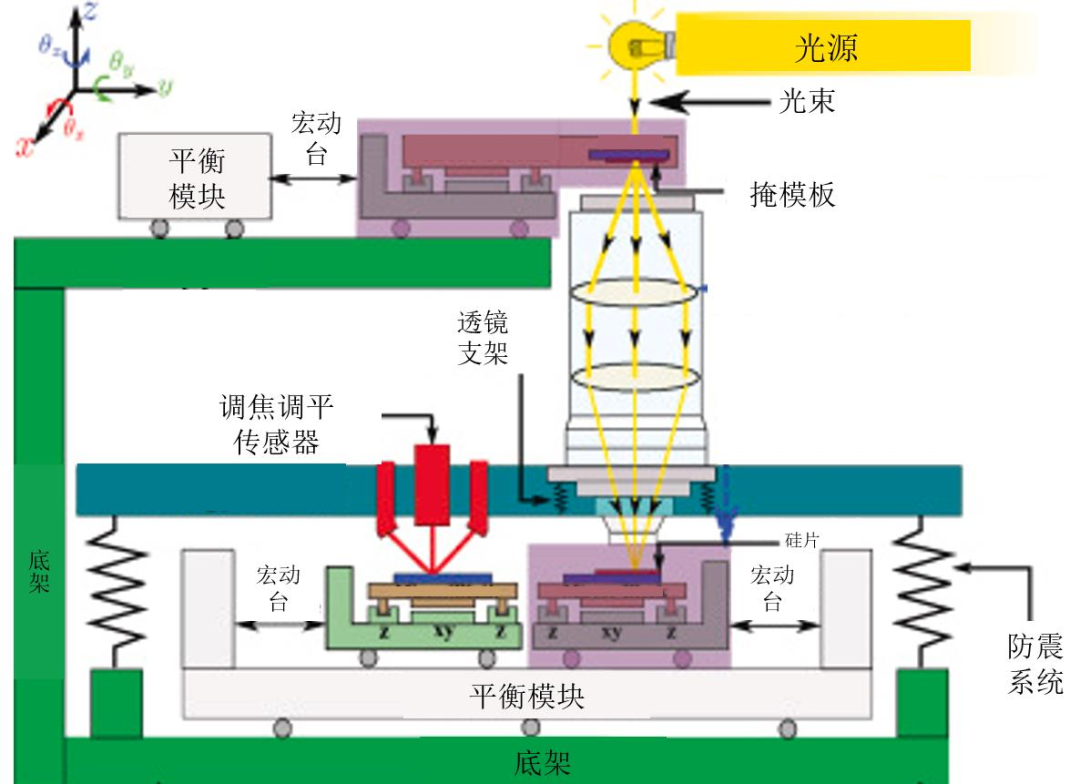

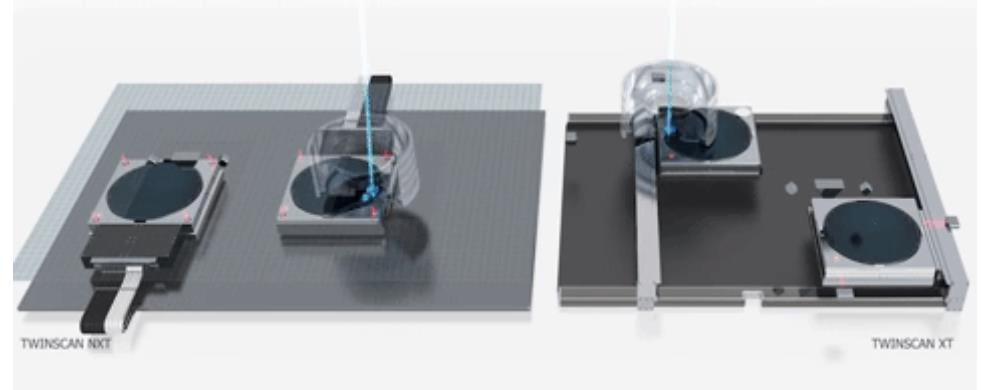

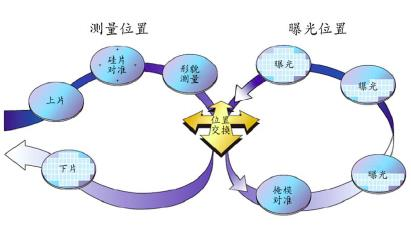

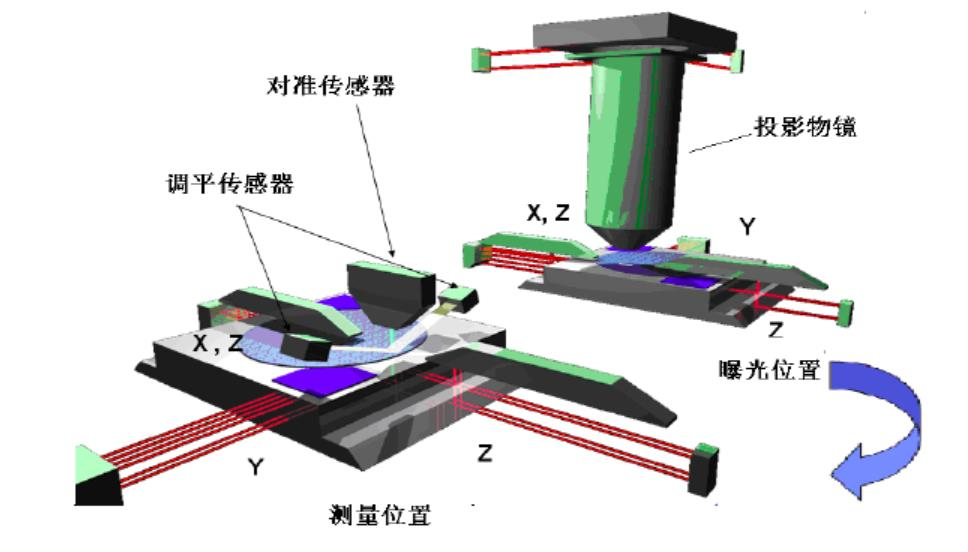

双工作台系统:精确对准+***产能的关键 ***双工作台由两个工件台组成, 两个工件台同时独立工作,负责完成步进运动、曝光扫描、对准扫描、上下硅片等功能。

双工作台工作流程:工作台分为1号和2号,1)2号工件台处于物镜下方,对晶圆进行调平调焦、曝光、刻片等操作,与此同时1号台进行待刻晶圆的上片下片;2)当2号台刻片完成,工件台系统进行换台,1号工件台换到物镜下方进行刻片,2号台进行上片下片, 如此循环往复实现***的高效生产。特点:双工作台较原先的单工作台效率提高了35%,精度提高10%,有效提高了***的产能。 图表62:双工作台

图表63:双工作台系统结构及换台过程

双工作台技术难点:需要速度快、对准精度高、运动稳定。

1)速度快:目前最先进的DUV***,晶圆的光刻生产速度为300片/h,1个影像单元的曝光成像约0.1秒, 实现这个成像速度,晶圆平台需以高达7g的加速度高速移动。7g的加速度意味着从0加速到100km/h只要约0.4秒,F1赛车需要2.5秒。 2)精确对准:面临的难点有巨大偏移——芯片制造需一层层向上叠加,每次重叠的误差称为套刻精度,要求是1-2nm。晶圆从传送模组到晶圆平台上,会产生机械误差,一般是数千纳米的偏移。高低差——投影物镜太大, 对焦点上下可接受的影像范围小于100nm。而晶圆表面高低不平,累加晶圆平台的高低差,晶圆表面不同位置的光阻高度可相差500-1000nm。因此每次曝光前,须针对每片晶圆做精密量测,截取到晶圆每一个区块纳米等级的微小误差,在曝光阶段实时校正。

3)运动稳定:稳定运动——利用balance mass吸收平衡晶圆平台所施加于机座的反作用力,使整座机台完全静止。稳定定位——晶圆要在完成量测后,要在极短的曝光时间内完美定位,ASML***可达到精度为0.06纳米的传感器确认精准定位。稳定运作——晶圆平台为减少磨损采用悬浮的移动方式,达成极高速的运动和持久稳定的运作。 图表64:TWINSCAN双工件台结构示意图

图表65:晶圆平台

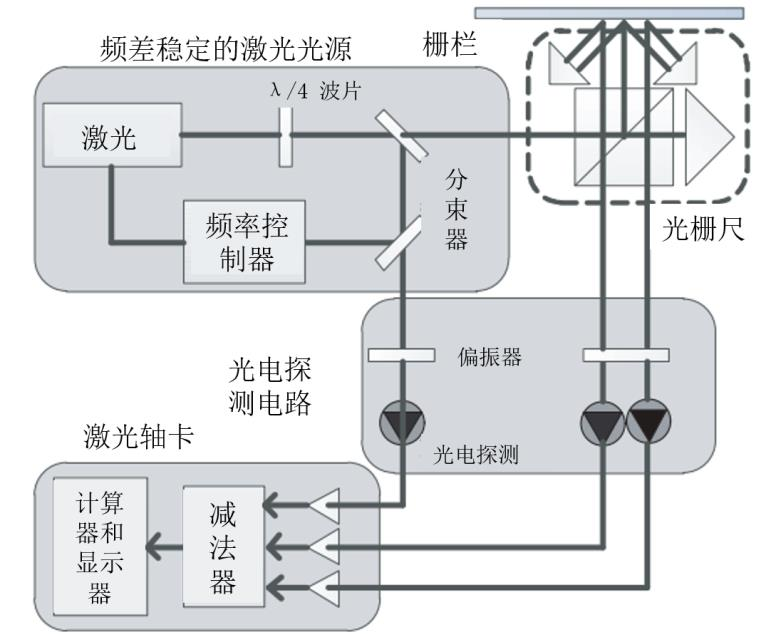

为了确保工件台稳定定位、精确对准。需要用到光栅尺、 TIS传感器等。 光栅尺用于工作台的定位。位移测量传感器有激光干涉仪和光栅尺,由于激光干涉仪对环境敏感性较高,目前高端机型较多使用光栅尺。原理:激光光源输出频差稳定的线偏振方向相互垂直的双频激光,一束作为参考差频信号由光电探测电路接收,另一束传输至光栅尺,光栅尺基于光栅多普勒效应和光学干涉原理实现位移测量。

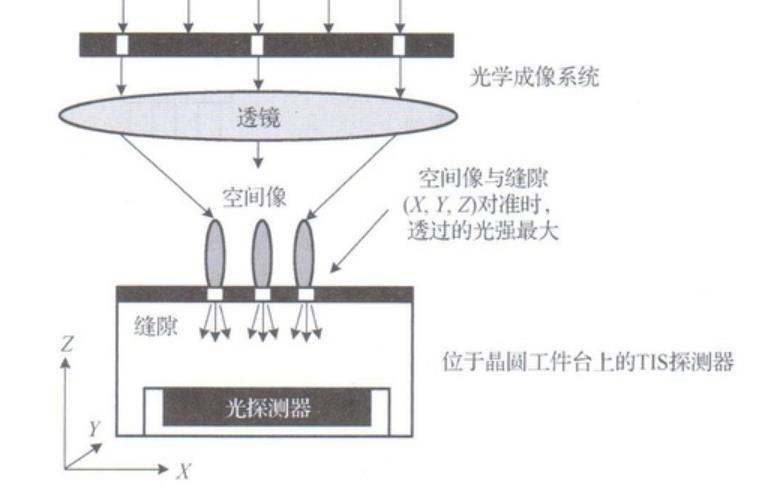

TIS系统用于掩膜工作台与晶圆工作台之间的对准。TIS系统包括①设置在掩膜工作台上的TIS标识(透光的密集线条);②晶圆工作台上的TIS传感器。TIS标识通过光学成像透镜系统,投射在晶圆工作台。晶圆工作台上的TIS传感器测出TIS标识像强度的空间分布,从而计算出掩膜工作台上TIS标识相对于晶圆工作台的位置。TIS系统还可以进一步确定投影透镜系统的像差和成像系统的畸变。 图表66:光栅尺测量系统示意图

图表67:TIS对准系统示意图

编辑:黄飞

-

半导体工艺流程图2017-01-14 5293

-

圆柱电池生产工艺流程图2009-11-06 11291

-

锂聚合物电池工艺流程图2009-11-04 1187

-

饲料生产工艺流程图2009-03-30 12141

-

pcb工艺流程图2008-12-28 7705

-

制冷站工艺流程图2008-06-28 2439

全部0条评论

快来发表一下你的评论吧 !