使用VCS观察Verilog二维数组仿真值的方法

电子说

描述

FIR设计过程中,不可避免使用到reg/wire的二维数组;在仿真的过程中,这些二维数组却带来不少麻烦,因为根据之前的内容,我们根本看不到这些二维数组的值。

而且,Verilog的端口定义是不支持二维数组这样的定义,所以也无法把数组传到顶层观察。

而实现过程中,这些二维数组却是流水线操作中的一部分,如果不知道它们的值,找BUG的过程肯定会十分艰难。

好在搜集各方资料后,经过一番实践,总算是得出了如何观察这些二维数组的值的方法。

首先,在testbench里面修改一下:

原来的版本:

initial begin$fsdbDumpfile("tb.fsdb");$fsdbDumpvars;end

第一个语句是产生一个fsdb文件,文件名为tb.fsdb,第二句是保存所有变量的波形。这里是为了产生fsdb文件,这样Verdi才能看到根据fsdb文件显示波形

修改后的版本:

initial begin$fsdbDumpfile("tb.fsdb");$fsdbDumpvars;$fsdbDumpMDA();end

第三行加了$fsdbDumpMDA(),这样就可以Dump所有的Memeory值,不管什么信号都可以保存到Memory。

VCS编译命令使用参数如下:

vcs \\*.v -LDFLAGS -Wl,--no-as-needed -timescale=1ns/1ps \\-fsdb -full64 -R +vc +v2k -sverilog -debug_all

仿真结束后,想使用Verdi查看二维数组的值,启动Verdi。

命令行如下:

verdi -nologo \\+v2k -sverilog *.v -ssf tb.fsdb &

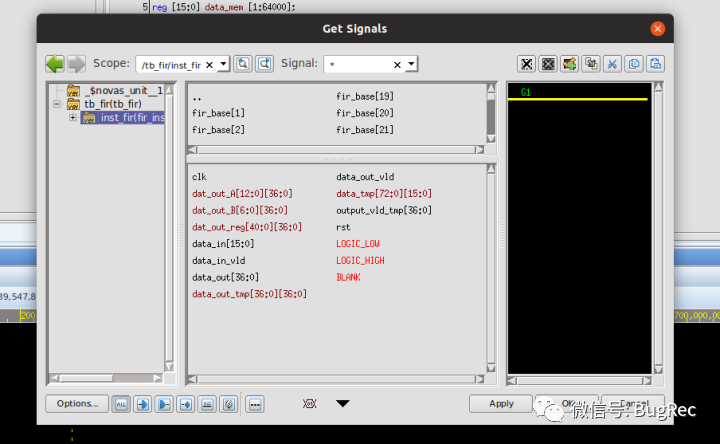

可以在Verdi添加信号时看到二维数组,如下图:

Verdi查看可以看到二维数组

添加之后:

可以从图中看到,很不直观,不能直接看出有什么问题。

换个思路,按照下图操作,选择Memory里的Memory/MDA工具

按照序号操作

按照图中1,2的顺序,然后按照下图选择想查看的信号

点击后选择想观察的信号

显示信号结果

这里需要说明,查看二维数组内部存储的值,可以使用框1里面的键,左右可以控制仿真时间,信号的值会跟随仿真时间改变而改变。框1的时间跨度可以更改。

默认显示的信号都是十六进制,如果想改变进制显示,在2的位置右键可以改变进制显示,并选择有符号或无符号显示。

地址数据也是十六进制显示,可以在3的位置右键改变为十进制显示。

有了这些工具的帮助,便可以从出错的结果一步步往上查,追查BUG的效率提高不少。

总结,操作顺序:

- Testbench加入$fsdbDumpMDA();

- 使用Verdi的Memory/MDA工具查看

-

二维数组介绍2025-11-25 151

-

将一维数组转为二维python2023-11-23 6538

-

python怎么创建二维数组2023-11-21 5282

-

C语言—二维数组介绍2023-09-11 1761

-

Python将二维数组输出为图片2023-01-11 2338

-

二维数组与数组指针以及指针数组2022-08-16 3883

-

Verilog中的二维数组说明2020-09-28 32040

-

请问Verilog怎么实现二维数组输出?2019-05-23 9277

-

C语言程序设计教程之二维数组如何应用二维数组的资料概述2018-10-26 1676

-

二维数组重新排序2017-12-12 950

-

c语言二维数组定义及其规则详解2017-11-16 22521

-

Labview之自动索引功能(二维数组--一维数组)2016-04-19 3479

全部0条评论

快来发表一下你的评论吧 !