SiC MOSFET学习笔记:各家SiC厂商的MOSFET结构

模拟技术

描述

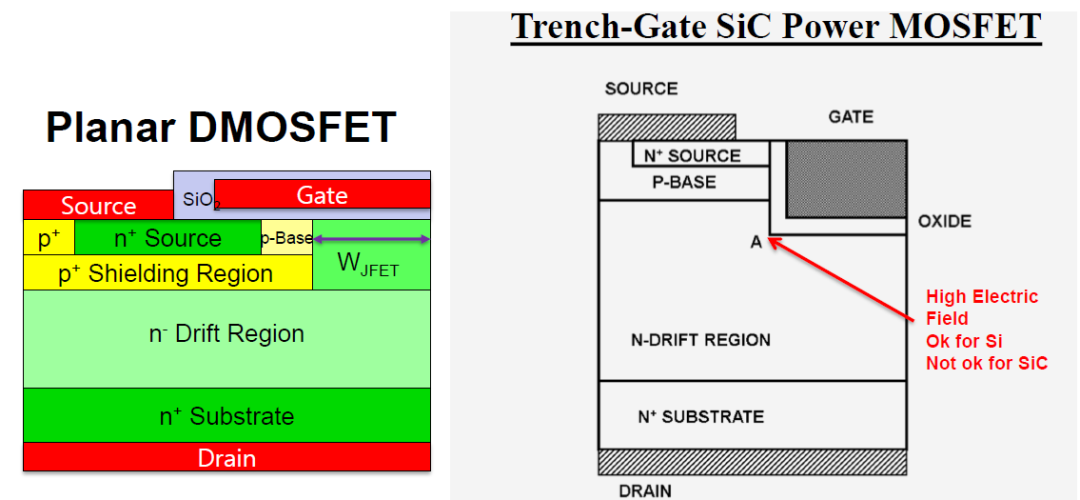

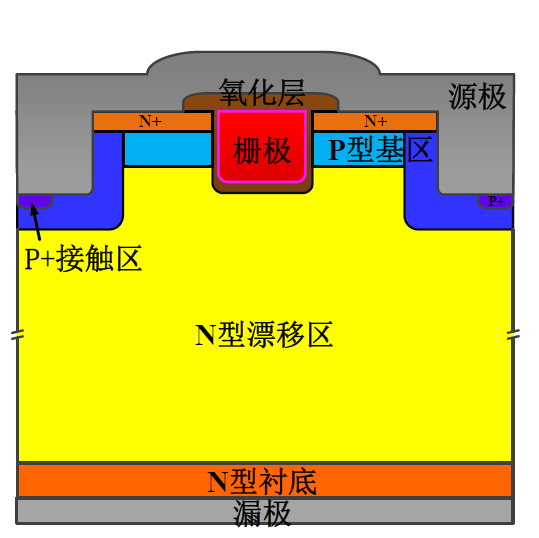

当前量产主流SiC MOSFET芯片元胞结构有两大类,是按照栅极沟道的形状来区分的,平面型和沟槽型。

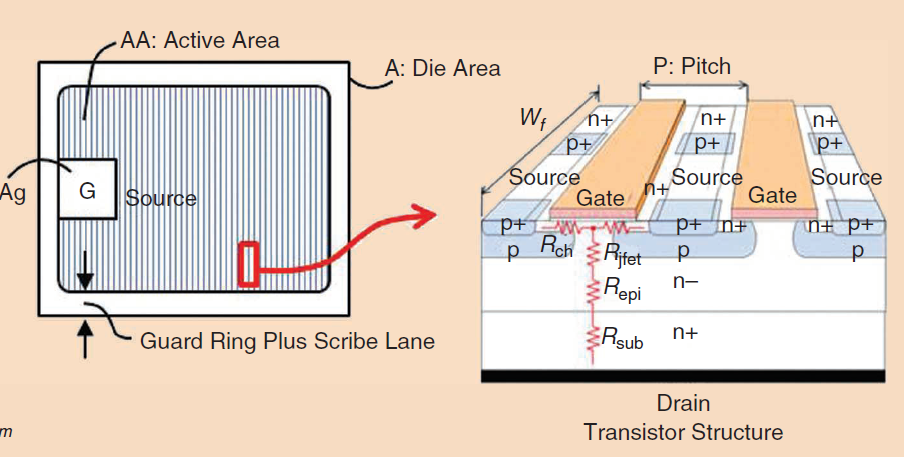

如上图,左边是一颗典型的平面SiC MOSFET芯片(宏观图)其中G区是栅极焊盘(gate pad),也就是引出栅极引线的地方,起控制作用。

AA是有源区(active area),其中AA的正面是源级区(source),键合源级引线过大电流;

背面是漏极区(drain),右图黑色部分代表背面金属(back metal),一般是钛镍银(TiNiAg)或者铝硅铜(AlSiCu)或者镍钯金(NiPdAu),背面金属焊接到衬板上,电流方向是衬板到芯片背面再到芯片正面再从源级引线出来。

可以看到左边的图中,在有源区AA中有许多条状单元,每个单元大小形状都一模一样,这样的最小功能单元叫元胞,芯片的功能就是由这亿万个元胞来完成的,元胞与元胞之间的中心距离为pitch。

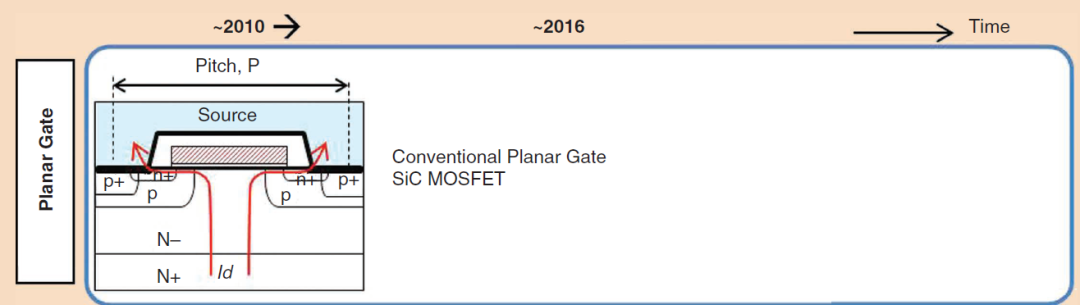

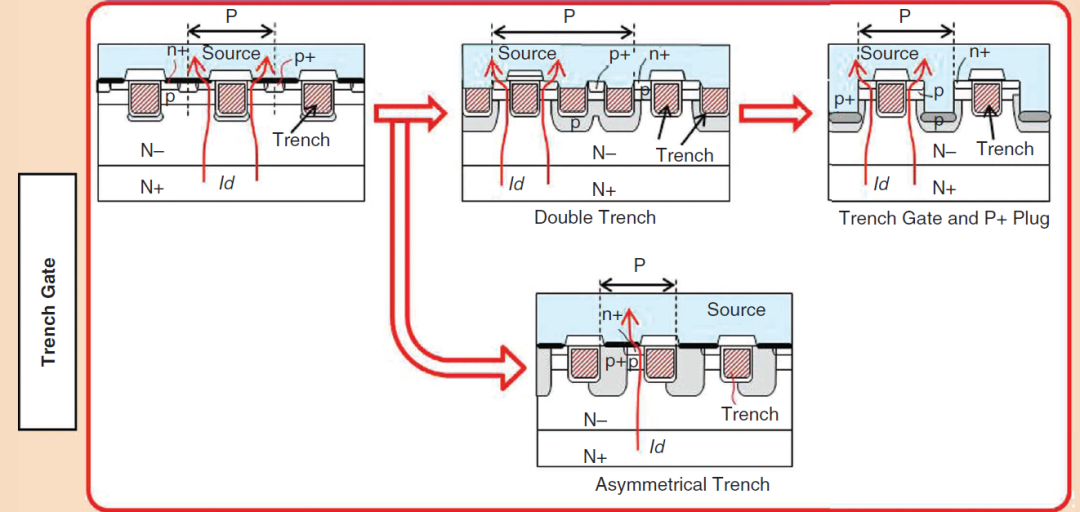

SiC MOSFET经过几代的发展,目前已经出现从平面栅到沟槽栅的各个版本:

其中平面栅(planar gate)是最早出现的,由于其结构简单,fab工艺难度小,因此其研发难度相对较低,但是由于平面栅的沟道电阻较大,因此在效率方面相比沟槽栅较弱。

相比之下稳定的沟槽栅的出现稍晚,直到2016年,才有稳定的量产方案出来,其中最具有代表性的是日本Rohm的双沟槽结构(Double Trench)和英飞凌的半包沟槽结构(Asymmetrical Trench)

由于沟槽栅结构相比平面栅结构消除了大部分的JFET效应,因此其沟道电阻较小,通态阻抗相比平面栅结构优势明显。

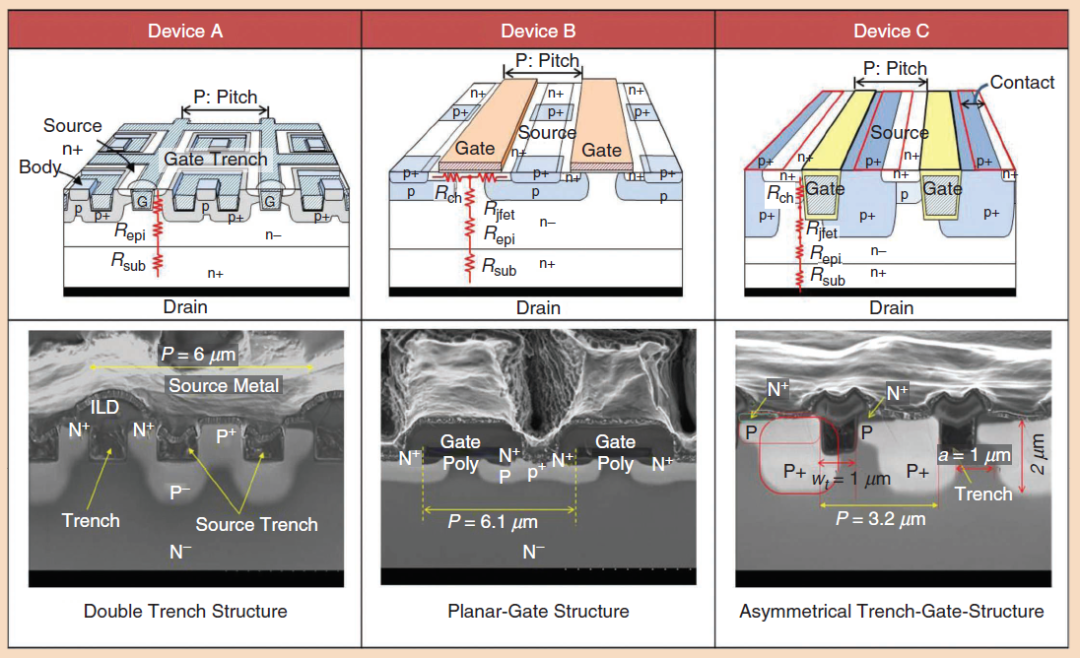

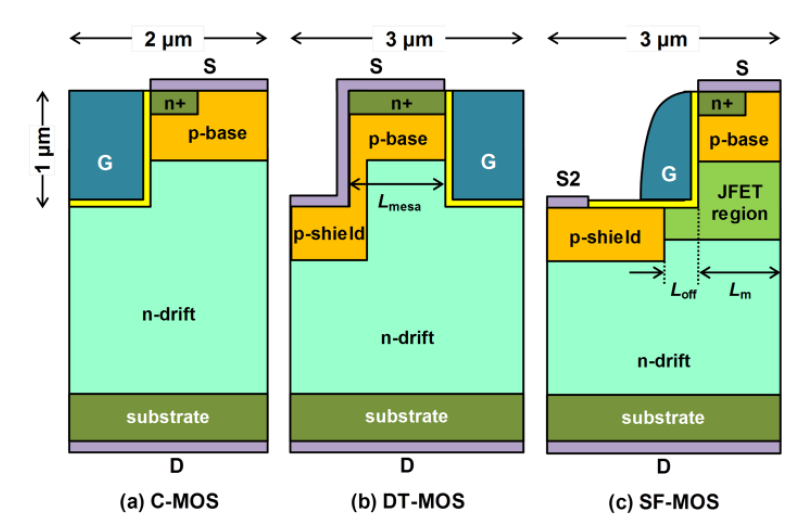

上图是三家典型的厂商器件结构,其中A家我猜是Rohm的双沟槽栅结构,B我猜是Cree的平面栅结构,C不用猜,肯定是英飞凌的非对称半包沟槽栅结构。

由上文可知,平面栅性能肯定是不如沟槽的,这个从各家产品的Rdson就看得出来,典型的1200V 5*5mm芯片英飞凌大概能做到15mΩ以下,Rohm能做到13mΩ,Cree和ST由于是平面栅,即使工艺能力很强,也只能做到17mΩ。

但是沟槽结构也带来一个问题,就是制造工艺难度大,特别是沟槽底部拐角处,电场强度大,电应力集中,容易产生可靠性问题。高槽角电场在Si材料可能风险不大,但是SiC材料就容易出问题。

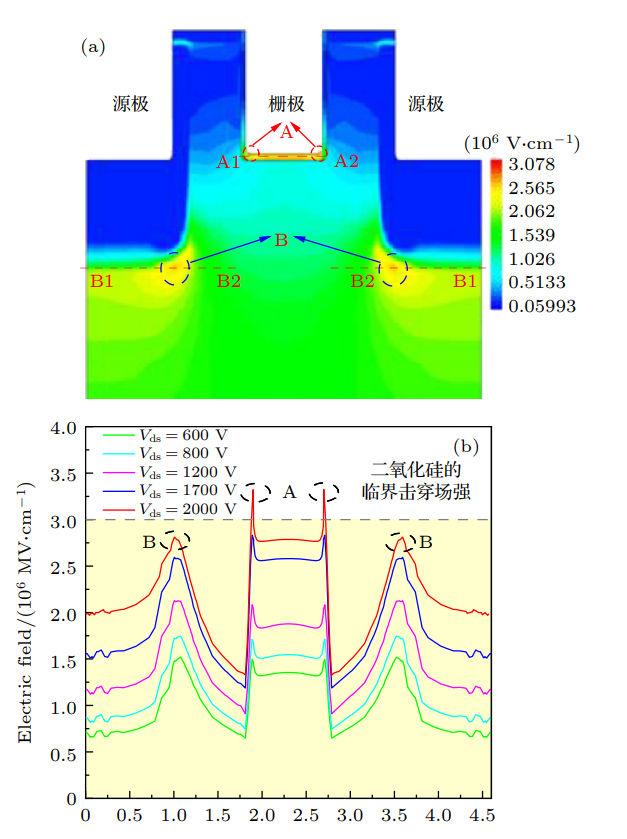

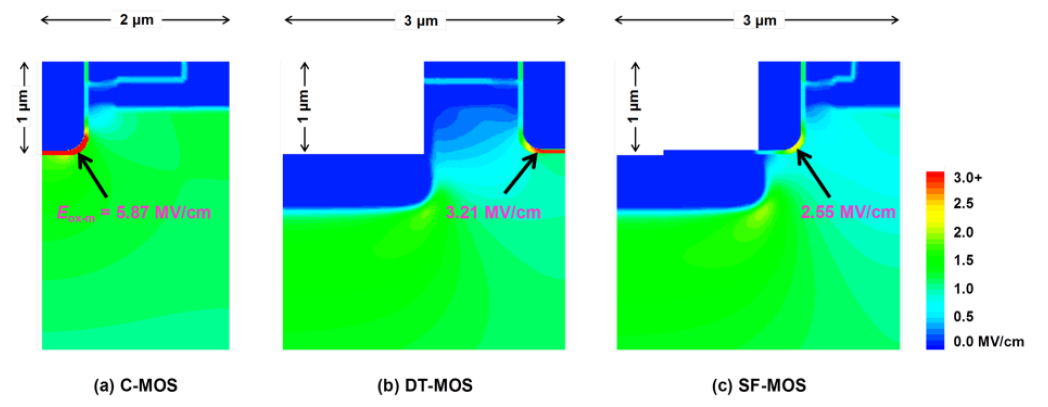

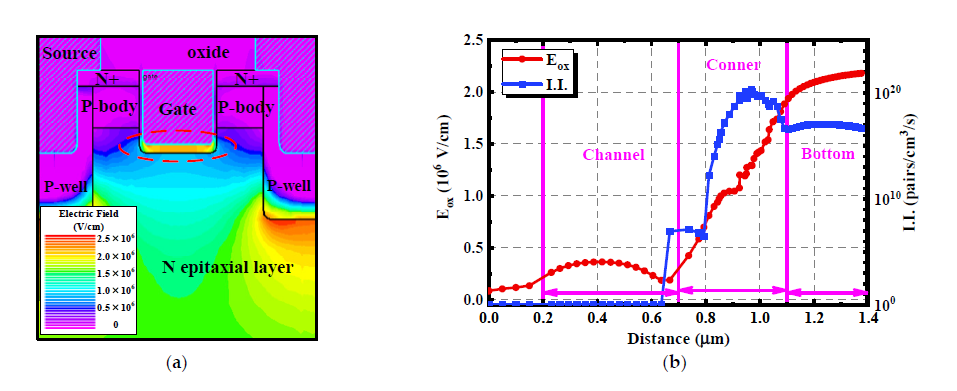

这张图就可以很清晰地看到电场的分布情况,我们知道,电势是场强对距离的积分,同时我们还知道,P-N结会形成耗尽层,并在反偏情况下向外拓展,这就使得电场强度的分布不均匀,尤其是在拐角处。

通过仿真分析可以看出,栅极沟槽拐角处和源级沟槽的拐角处电场强度是非常大的,如果这个场强超过材料本身的临界击穿场强,就会造成击穿,器件失效。

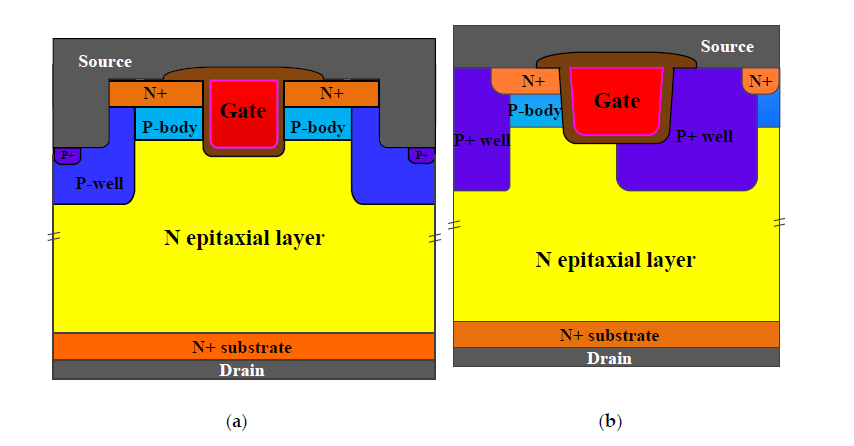

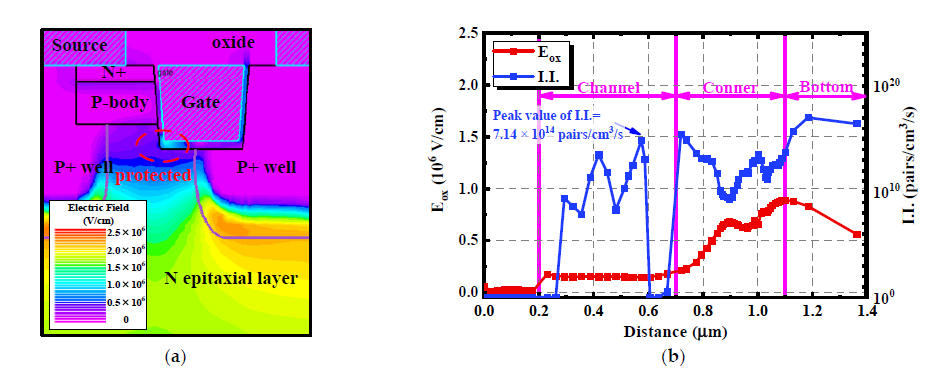

如何解决沟槽栅拐角电场集中的问题?目前常见的方案是添加底部P型掩蔽层(P Shield)进行保护,也叫BPW(bottom P well)

如图,a是常规的MOS(conventional MOS)结构不带P掩蔽层,

b是Rohm的双沟槽(Double trech)结构形成的源级P掩蔽层

c是定制掩蔽栅(shielded fin)结构,特意在栅极下方形成P掩蔽层

来源:重庆大学蒋华平老师

可以看到,不加任何掩蔽层(保护层)的常规结构a,其沟槽拐角处的电场强度最高,达到了5.87MV/cm。

而b的双沟槽结构通过源级沟槽形成的P掩蔽层,通过改变耗尽层形状,改变了电场方向,缓解了沟槽拐角处的电场集中,场强降到了3.21MV/cm

c的定制化掩蔽栅(shield fin)结构和英飞凌的半包沟槽类似,直接在拐角处添加一个P掩蔽层,对栅极沟槽进行保护,场强降到了2.55MV/cm

最后欣赏下芯片设计美学之 Rohm双沟槽 VS 英飞凌半包沟槽:

来源:东南大学Zhaoxiang Wei老师

审核编辑:汤梓红

-

SiC MOSFET的器件演变与技术优势2023-02-27 1586

-

SiC MOSFET的结构及特性2023-02-16 5920

-

SiC-MOSFET器件结构和特征2023-02-07 1617

-

SIC MOSFET2021-04-02 2682

-

【罗姆SiC-MOSFET 试用体验连载】SiC MOSFET元器件性能研究2020-04-24 2172

-

浅析SiC-MOSFET2019-09-17 6454

-

SiC功率器件SiC-MOSFET的特点2019-05-07 5733

-

SiC-MOSFET有什么优点2019-04-09 4750

-

搭载SiC-MOSFET和SiC-SBD的功率模块2019-03-12 3462

-

沟槽结构SiC-MOSFET与实际产品2018-12-05 4890

-

SiC-MOSFET与Si-MOSFET的区别2018-11-30 11093

-

SiC-MOSFET的应用实例2018-11-27 6105

-

为何使用 SiC MOSFET2017-12-18 6097

全部0条评论

快来发表一下你的评论吧 !