如何用单PMOS设计分立式负载开关?

模拟技术

描述

★★★ SCD-3---分立式PMOS负载开关 ★★★

引言:上节讲到了NMOS用作负载开关,结论是NMOS更适合做低边开关,但在实际使用过程中,高边开关的使用场景大大多于低边场景,可以这么说,一个板级系统,80%都使用的高边开关而不是低边。所以本节就分析PMOS用作高边负载开关天生的优势以及设计方法。

€1.负载开关的类型

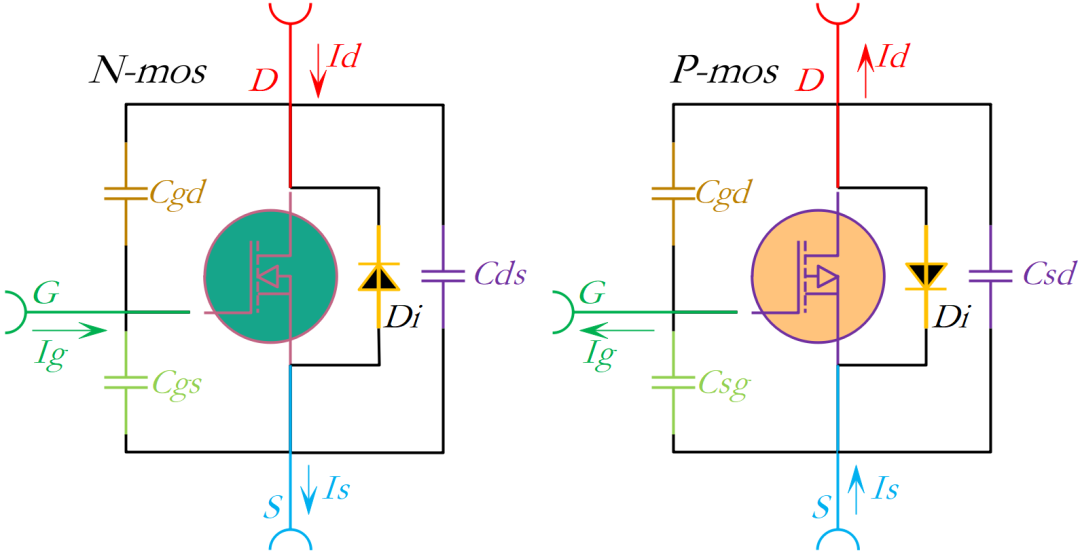

图3-1:NMOS和PMOS寄生模型

在深入研究关键参数之前,我们先来看看不同类型的负载开关。高压侧负载开关将负载与电源连接或断开,由外部启用信号控制开关将高压侧电源电流切换到负载。而低压侧开关将负载与地连接或断开,从而从负载吸收电流。

负载开关可以容易地用MOSFET实现,MOSFET将电流从电源传递到负载,并通过控制信号接通或断开。将控制信号提供给MOSFET的栅极驱动电路以接通或断开MOSFET。

€2.P沟道高侧负载开关

使用P沟道MOSFET,通过将输入电压连接到MOSFET源极,将负载连接到MOSFET漏极,可以实现高侧负载开关,见 图3-2, 将栅极拉低将使电流流入负载Rload。

图3-2:增强型P-ch MOS高边负载开关

€3.P沟道高侧负载开关

如果使用PMOS设计低边开关,那么导通时S极就几乎是GND电平,在需要PMOS关断的状态下,G极电位可以是0电平甚至是正电平,但是需要PMOS导通时,G极电位就必须是负电平,这样的设计更加复杂,所以不会使用PMOS做低边开关。

€4.关键参数

负载开关的关键参数是连接电压输入和电压输出引脚之间的MOSFET的导通电阻RDSon、MOS承受的最大电流IDmax以及电路能够承受的最大电压VDSmax。导通电阻越低,MOS管的功耗越低,从输入到输出的电压降越低。

虽然RDSon、IDmax和VDSmax是MOSFET的参数,但负载开关的最大压降和最大功耗可以通过以下公式计算,给定电流I:

现在的MOSFET通常具有几十mΩ的导通电阻值,因此如果负载开关具有50mΩ的接通电阻并控制200mA的负载,MOSFET在接通时仅消耗2mW,并且具有10mV的输入到输出电压降。即使峰值电流为1A,也只会导致50mV的电压降和50mW的峰值功耗。

由于负载开关电路在电源接通时是动态的,因此设计时需要满足低泄漏电流,即源极和漏极之间的泄漏电流应尽可能接近零,这个参数同样可以在datasheet中找到。

**** €5. 设计示例

*设计背景:*请用PMOS设计一个高边开关,输入电压为24V,通路电流最大为10A,控制侧为MCU,控制电平为3.3V。

*设计分析:*VGSTH以Vin为参照,G极需要施加接近或等于或高于24V的控制电平。

*设计选型:*所选NMOS需要满足VDSS>24V,IDSS>10A,Rdson和漏电流尽量小,驱动电平阈值VGSTH<3.3V。这里我们选择LRC的LP73035DT1WG,相关参数如下:

图3-3:LP73035DT1WG最大额定参数

图3-4:LP73035DT1WG正常工作参数

从选型结果来看,LP73035DT1WG完全满足我们的要求,ID远大于10A,开启阈值(-1V~-2.5V)和Rdson(8mΩ)非常小,实际使用热损耗非常低。

*设计结果:*图3-5是设计的结果,当三极管导通时,24V经过R1和R2分压,R2一般特别小甚至没有,那么24V就全落在R1上,此时G极电平就近似等于Vin=24V,VGS=0V>-1V,PMOS关闭,当三极管不导通时,PMOS的S极和G极之间电位差近似等于Vin,VGS=-24V<-2.5V,PMOS打开。需要注意的是规格书中VGS的极限值是±25V,-24V其实比较接近,有一定风险,可以选VGS更大一些的PMOS型号。

图3-5:PMOS高边开关驱动设计

另外,三极管我们都选择过驱动方式,所以R3值选的比较小,使基极电流Ib比较大,不用担心导通时干路电流比较大,因为R1=1MΩ已经将电流限制的非常小了。

-

分立式整流器的整流原理2024-10-11 2472

-

如何使用分立式电流检测优化 PoE 系统2024-09-09 527

-

取代分立式保护并优化PLC系统保护2024-08-29 745

-

集成式与分立式开漏电平转换2024-08-28 471

-

建立FETching分立式放大器的提示2023-11-23 459

-

如何用单NMOS设计分立式负载开关?2023-06-07 2925

-

分立式 LED 驱动器-AN107392023-02-09 628

-

如何进行分立式设计?2022-11-23 673

-

PowerLab 笔记:如何进行分立式设计2022-11-07 968

-

基于IGBT的分立式三相逆变器的TIDA 00472设计2022-09-06 1091

-

分立式逆变器的挑战2019-05-13 2126

-

支持多种汽车应用的微控制器分立式电源设计2018-12-28 1693

-

集成与分立式低电压电机驱动解决方案的主要差异2018-12-07 2761

-

电源变换器集成式和分立式的作用特点2018-08-02 4520

全部0条评论

快来发表一下你的评论吧 !