UVM中的uvm_do宏简析

描述

uvm_do宏及其变体提供了创建、随机化和发送transaction items或者sequence的方法。

`uvm_do

`uvm_do宏将uvm_sequence或uvm_sequence_item类型的变量作为参数。使用factory创建一个对象并赋值给指定的变量。

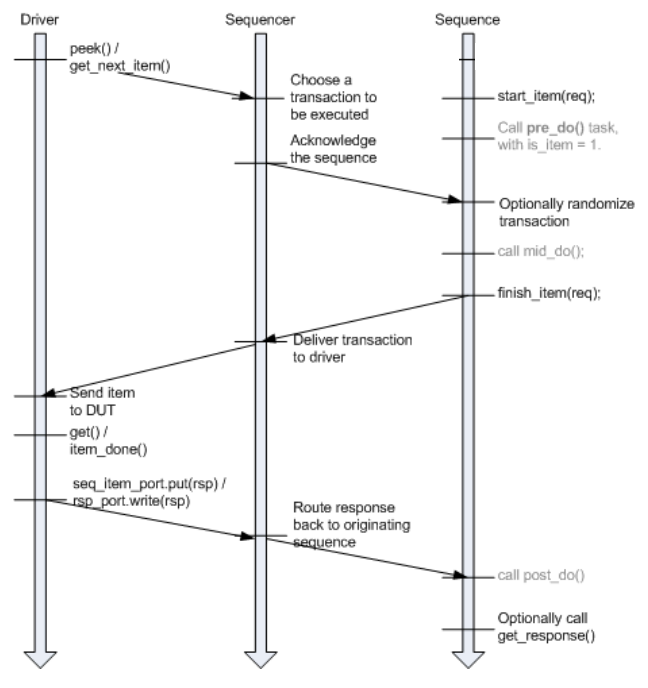

当driver从sequencer中请求一个uvm_sequence_item时,该uvm_sequence_item被随机化并提供给driver。

class simple_seq_do extends uvm_sequence #(simple_item); ... // Constructor and UVM automation macros virtual task body(); `uvm_do(req) endtask : body endclass : simple_seq_do

上面的例子中,simple_seq_do的body使用uvm_do宏,发送了一个类型为simple_item的数据项。

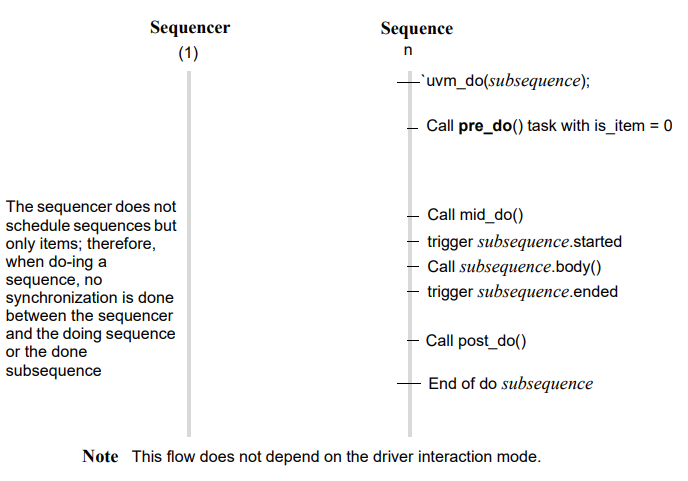

类似地,下面的例子声明了一个sequence(simple_seq_sub_seqs),使用`uvm_do来执行前面定义的simple_seq_do类型的sequence。

class simple_seq_sub_seqs extends uvm_sequence #(simple_item); ... // Constructor and UVM automation macros simple_seq_do seq_do; virtual task body(); `uvm_do(seq_do) endtask : body endclass : simple_seq_sub_seqs

`uvm_do_with

`uvm_do_with宏与`uvm_do类似。

第一个参数是从uvm_sequence_item派生出来的变量,包括uvm_sequence_item或者uvm_sequence 。

第 二 个 参 数 可 以 是 任 何 有 效 的inline constraints。

在下面的例子中,sequence产生两个数据项,对addr和data的值有特定的约束。

class simple_seq_do_with extends uvm_sequence #(simple_item);

... // Constructor and UVM automation macros

virtual task body();

`uvm_do_with(req, { req.addr == 16'h0120; req.data == 16'h0444; } )

`uvm_do_with(req, { req.addr == 16'h0124; req.data == 16'h0666; } )

endtask : body

endclass : simple_seq_do_with

如果约束条件只是用来将发送数据设置为特定的值,可以用用户定义的任务来代替宏。

class simple_seq_do_with extends uvm_sequence #(simple_item);

task do_rw(int addr, int data);

item= simple_item::create("item",,get_full_name());

item.addr.rand_mode(0);

item.data.rand_mode(0);

item.addr = addr;

item.data = data;

start_item(item);

randomize(item);

finish_item(item);

endtask

virtual task body();

repeat (num_trans)

do_rw($urandom(),$urandom());

endtask

...

endclass : simple_seq_do_with

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

我的第一个UVM代码——Hello world2023-11-03 613

-

UVM设计中的sequence启动方式有哪几种呢?2023-08-17 7680

-

一文详解UVM设计模式2023-08-06 4985

-

如何用Verdi查看UVM环境中的变量?2023-06-25 3207

-

UVM中uvm_config_db机制背后的大功臣2023-06-20 2456

-

UVM学习笔记(一)2023-05-26 2514

-

UVM中seq.start()和default_sequence执行顺序2023-04-04 3653

-

UVM中的utility宏2023-03-30 1815

-

谈谈UVM中的uvm_info打印2023-03-17 2562

-

什么是uvm?uvm的特点有哪些呢2022-02-14 1895

-

数字IC验证之“搭建一个可以运行的uvm测试平台”(5)连载中...2021-01-26 1576

-

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...2021-01-21 4410

-

IC验证"一个简单的UVM验证平台"是如何搭建的(六)2020-12-04 2819

-

IC验证之UVM常用宏汇总分析(四)2020-12-02 4573

全部0条评论

快来发表一下你的评论吧 !