如何降低SiC/SiO₂界面缺陷

模拟技术

描述

目前,许多企业在SiC MOSFET的批量化制造生产方面遇到了难题,其中如何降低SiC/SiO₂界面缺陷是最令人头疼的问题。

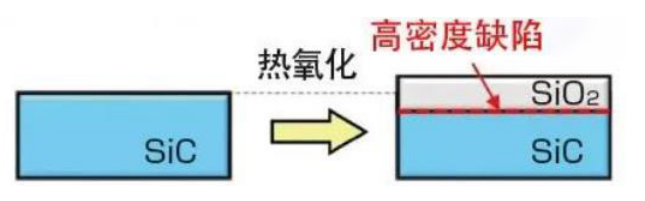

通常,为了形成SiO₂氧化膜,制造SiC MOSFET时通常会用到热氧化工艺,而过高的温度会导致“残留碳”,从而会引发SiC/SiO₂界面缺陷(比Si/SiO₂多100倍),继而导致沟道迁移率降低,甚至影响器件长期可靠性。

因此,业界正在探索各种技术来形成高质量SiO₂氧化膜,目的是不产生或减少残留碳。

近日,韩国企业EQ TechPlus宣布,他们开发了一种下一代氧化膜沉积设备,用于大规模生产SiC功率半导体,与采用传统高温热氧化设备相比,该设备可以将SiC界面碳含量降低约50%。

据EQ TechPlus介绍,他们的设备的优点是可以在较低低温下沉积氧化膜(500-750℃),而现有的其他设备通常需要1200-1300℃的高温。

为此,该设备一方面可以减少用电量,另一方面还可以将残留碳以一氧化碳和二氧化碳等气体的形式排出,最大限度地减少由碳引起的界面缺陷。

据“行家说三代半”了解,EQ TechPlus采取了一种独特的方法来解决碳化硅SiO₂氧化膜沉积难题。

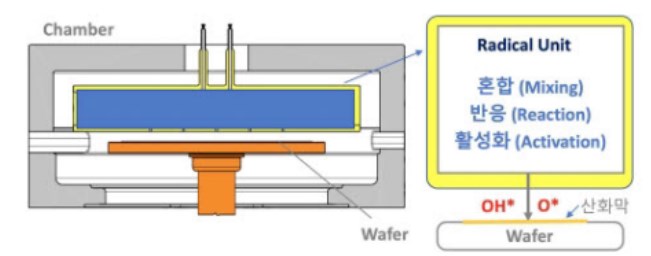

EQ TechPlus设备示意图

EQ TechPlus采用的是一种混合模块技术,结合了现有等离子体和热处理设备的优点。他们的非等离子体热处理不产生离子,因此不会出现离子降解或对氧化膜的损害,可以更好地形成均匀而稳定的氧化膜,还可以很容易地加装到现有的单室设备上进行氧化处理。

除了碳化硅外,该公司的自由基氧化和原子层沉积(ALD)技术可以应用于硅基D-RAM、NAND闪存和系统半导体,以及氮化镓基功率半导体等化合物半导体工艺。

EQ TechPlus自由基氧化工艺的核心装置概念

该公司首席执行官Kim Yong-won说,"我们最近在与韩国功率半导体公司进行了MOSCAP(金属氧化物半导体结构电容器)检测测量和效果评估,结果显示,我们的设备减少了界面缺陷,并改善薄膜性能。

除了MOSCAP测试外,他们还与其他功率半导体公司进行了MOSFET的性能验证,这项评估预计将在明年上半年结束。

据介绍,该公司将于今年9月份获得SEMI(半导体设备和材料协会)质量认证,并开始批量生产该设备。该公司计划将其位于京畿道的安城工厂的规模扩大一倍以上,以全面生产下一代氧化物薄膜沉积设备。

Kim Yong-won透露,"去年,我们的300毫米晶圆和硅半导体的氧化膜沉积业务业务获得了56.4亿韩元(约3100万人民币)的销售额,随着新设备的供应,我们今年目标将实现100亿韩元(约5600万人民币),预计2028年年销售额达到3000亿韩元(16.66亿人民币)。"

审核编辑:刘清

-

sio2_sio2是什么意思2011-12-13 22281

-

SiC外延层的缺陷控制研究2024-01-08 4262

-

罗姆成功实现SiC-SBD与SiC-MOSFET的一体化封装2019-03-18 3042

-

SiC-SBD大幅降低开关损耗2019-03-27 3263

-

如何降低汽车用PCB缺陷率2021-01-28 2036

-

SiC MOSFET FIT率和栅极氧化物可靠性的关系2022-07-12 13838

-

表面氢化降低SiC/金属接触间界面态密度的机理2009-05-07 1962

-

降低 SiC 电阻之路2022-07-29 2450

-

如何消除SiC MOSFET——栅极电路设计中的错误及其对稳健性的影响2022-08-04 2242

-

5.2.3 扩展缺陷对SiC器件性能的影响∈《碳化硅技术基本原理——生长、表征、器件和应用》2022-01-06 1415

-

浅析SiC MOS新技术:沟道电阻可降85%2023-10-11 4971

-

揭示界面导电网络对锂离子电池SiO基负极快充性能影响的基本机理2023-12-12 1975

-

4H-SiC缺陷概述2023-12-28 5177

-

一文详解SiC的晶体缺陷2024-11-14 3490

-

有效抑制SiC外延片掉落物缺陷生成的方法2025-02-10 401

全部0条评论

快来发表一下你的评论吧 !