集成电路的可靠性判断

描述

集成电路可拿性是指.在规定的条件下和规定的时问内,集成电路完成规定功能的能力。可通过可靠度、失效率、平均无故障工作时间、平均失效时间等来评价集成电路的可靠性。可靠性包含耐久性、可维修性和设计可靠性三大要素

集成电路可靠度的计算公式为 R(t)=1-F(t)

式中,R(t)是可靠度函数,为t时刻集成电路正常工作的概率;F(t)是累积失效分布函数,即随机选定的集成电路在t时刻失效的概率。

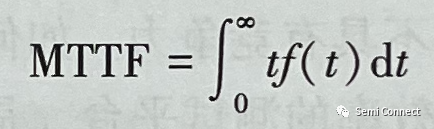

可靠性具有综合性、时间性和统计性的特征。为了量化可靠性这一概念,一般用乎均失效时间 (Mean Time to Failure, MTTF),即第一次失效的平均时间,来表征集成电路的寿命,即

式中,f(t)为寿命分布模型,是0到无穷大的时间范围内的概率密度函数。

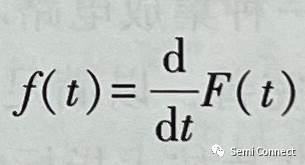

F(t)与f(t)的数学关系为

封装可靠性是集成电路可靠性研究中的重要方面。封装可靠性研究主要包括封装设计、封装工艺、封装材料等方面的改进、优化、优选,以及检测方法、试验方法、应用研究等,其目的是为了保证集成电路的可靠性。在新的封装结构、封装工艺和封装材料对可靠性的影响尚不明晰的情况下,需发展新的可靠性理论,研究新的可靠性机制,应用先进的失效分析手段,对电路的可靠性进行分析、模拟、评估和改进,以实现对产品可靠性寿命的准确预测。对于集成了多种功能的封装体,在开发新产品或改进产品的过程中,需进行封装可靠性试验.完成可靠性监测统计,确定试验监测的潜在失效机理。

封装缺陷和失效是影响封装可靠性的主要原因。在机械、热 化学或电气等的作用下,集成电路性能降低;当产品的性能参数和特征超出可接受的范围时,认为其发生失效。封装缺陷会加速封装失效和集成电路功能的失效,而失效导致的结果通常是无法预料的。封装缺陷在制造和组装过程中随机发生,可能发生在其中的任何阶段,包括芯片钝化、芯片黏结、引线键合、引脚成型等。可靠性研究的主要对象是缺陷和失效发生的位置、类型和潜在来源。由于封装体易受各种缺陷和失效影响,因此必须通过试验和仿 真分析确定失效的主要因素(常使用物理模型、数值参数法和试差法等方法进行失效预测),并通过加速试验验证鉴别器件的失效周期。在生产过程中,可通过控制工艺参数、改进封装材料和优化封装参数设计来降低封装的失效率。

对封装的可靠性评估主要在集成电路封装的认证过程中完成。认证过程包括虚拟认证、产品认证和量产认证。其中,虚拟认证是基于失效物理模型(即基于失效机理和失效时间预计,用于失效物理可 靠性预测的数字/分析模型)的预计寿命来进行的,产品认证包含制造样品的物理试验和可靠性估计的加速试验。随着失效分析技术的发展,可靠性评价从基于外场数据失效率评估,演变到考虑封装特性和负载应力的基于失效物理模型的预计。对于特定载荷条件下产生的特定失效机理,可靠性由确定失效部位的失效时间 (Time to Failure,TTF) 来确定。对于失效部位的TTF 决定的可靠性,可通过失效部位、应力输人和失效模式进行评估和报告。电气电 子工程师学会 IEEE 1413.1-2002 标准给出了电子系统或设备的可靠性预计流程框架,其中包含可靠性预计报告必须涵盖的内容。

责任编辑:彭菁

-

集成电路可靠性介绍2025-12-04 1036

-

集成电路前段工艺的可靠性研究2025-03-18 2242

-

半导体集成电路的可靠性评价2025-03-04 2112

-

等离子体蚀刻工艺对集成电路可靠性的影响2025-03-01 2001

-

GaN功率集成电路的可靠性系统方法2023-06-19 834

-

集成电路封装可靠性试验的分类与作用2023-06-16 2636

-

集成电路封装可靠性设计2023-06-15 1961

-

#硬声创作季 #集成电路 集成电路版图设计-9.12项目设计实例及技巧-芯片的可靠性1-闩锁效应水管工 2022-10-17

-

集成电路封装测试与可靠性2021-04-09 2421

-

集成电路为高可靠性电源提供增强的保护和改进的安全功能2021-03-21 901

-

基于集成电路的高可靠性电源设计2019-07-25 2816

-

集成电路在高可靠性电源的应用2019-06-11 1509

-

集成电路可靠性检查的最佳实践方案2018-02-02 3040

-

超深亚微米集成电路可靠性技术2010-04-27 982

全部0条评论

快来发表一下你的评论吧 !