高效DC/DC转换器从15.3V背板提供两个3A输出

描述

3.3V 直流母线在宽带网络系统中广受欢迎,用于各种较低电压,为 DSP、ASIC 和 FPGA 供电。这些较低的电压范围为1V至2.5V,通常需要高负载电流。为了保持高转换效率,降压转换器的功率MOSFET导通损耗必须降至最低。问题在于,3.3V总线还频繁使用亚逻辑电平MOSFET。这种MOSFET具有相对较高的RDS(ON),将转换器的满载效率限制在 85% 左右。更有效的解决方案是使用逻辑电平MOSFET,其R值非常低DS(ON)但需要一个 5V 电源。LTC1876 通过将一个 1.2MHz 升压型稳压器 (其从一个 5.3V 输入产生一个 3V 偏置电源)与两个提供低电压输出的降压型控制器相结合,允许使用逻辑电平 MOSFET。通过将所有三个稳压器集成到单个 IC 中,LTC1876 实现了小型且成本低廉的高效电源。

设计示例

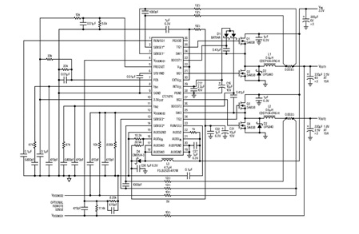

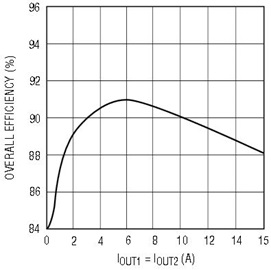

图1所示为采用2.5V输入提供15.1V/8A和15.3V/3A的设计。因为 LTC1876 为 MOSFET 栅极驱动提供了一个 5V 偏置,所以 RDS(ON)MOSFET Si4838 (典型值为 2.4mΩ) 可用于实现高效率。图2显示,在很宽的负载范围内,总效率高于90%。

图1.LTC1876 设计可在 3A 和 3A 时将 2.5V 转换至 15.1V,在 8A 时转换 15.<>V。

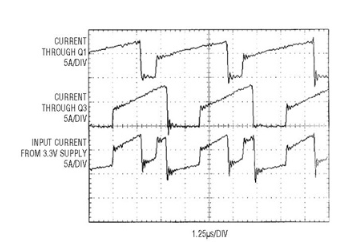

图2还显示,该设计的轻载效率超过84%。这是 LTC1876 突发模式操作的一个直接优势。两个降压通道的异相运行进一步提高了效率。第一通道的顶部MOSFET与第二通道的MOSFET异相180°,从而最大限度地减少了通过输入电容的RMS电流。这大大降低了与输入电容ESR相关的功率损耗。图3显示了此操作的详细电流波形。®

图2.设计效率高,如图1所示。

图3.每个开关稳压器的峰值电流为5A,但输入端的总纹波仍然仅为5A,使C最小化在要求。

结论

LTC1876 采用三种技术,从一个低输入电压高效地为低电压 DSP、ASIC 和 FPGA 供电。第一种技术使用内部升压稳压器为MOSFET栅极驱动提供单独的5V电压。其次,其突发模式操作可在轻负载下实现高效率。最后是异相技术,可最大限度地减少输入RMS损耗并降低输入噪声。完整的稳压器电路保持小巧且价格低廉,因为所有三个开关稳压器(一个升压稳压器和两个降压控制器)都集成在单个IC中。对于提供单独 5V 或输入电源大于 5V 的系统,内部升压稳压器可用于提供开关电流高达 1A 的第三个升压输出。

审核编辑:郭婷

-

SGM61232:28V、3A降压DC/DC转换器的深度解析与应用设计2026-03-19 307

-

探索MAX17509:全能型同步降压DC - DC转换器2026-03-06 488

-

深度剖析LT3477:3A DC/DC转换器的卓越性能与应用实践2026-02-03 426

-

4.5V至28V输入、3A 输出、同步降压DC-DC转换器TPS54335-2A数据表2024-04-15 525

-

4.5V至28V输入、3A 输出、同步 降压 DC-DC转换器TPS5433xA数据表2024-04-10 457

-

DC-DC降压-升压转换器12V/4A的资料分享2022-09-05 2562

-

一个从5V到4V的DC-DC转换器2022-07-07 2871

-

一种高效率的同步降压DC-DC变换器3A输出电流2021-11-17 1455

-

1.5V升3V200MA升压 DC/DC 转换器2021-11-08 912

-

DN278高效DC/DC转换器从3.3V背板提供两个15A输出2021-04-19 825

-

高效DC/DC转换器从3.3V背板提供两个15A输出2019-05-22 1077

-

3A降压DC-DC转换器PAM23202019-03-07 2550

-

使用DC / DC转换器为ADC供电2018-07-24 10207

-

Maxim推出3A输出、同步DC-DC转换器2009-12-21 805

全部0条评论

快来发表一下你的评论吧 !