我的第二个UVM代码—连接interface

电子说

1.4w人已加入

描述

写testbench最最核心的部分就是发激励,今天用一个简单的示例来介绍如何在uvm里给RTL发激励。

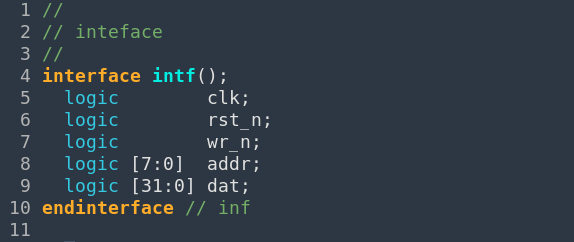

第一步,先来定义interface,如下。

interface是sv的一个关键字,级别等同于module,所以与module是并列的,一般单独写一个文件。

第二步,在testbench里实例化interface,并连接interface与RTL。

既然interface与module同级,实例化时就不能忘记括号。由于大部分信息不需要引到interface端口上,所以看上起来有点不太像模块例化。

第三步,把interface实例化对象传递到uvm。

在run_test()之前,通过uvm里的函数uvm_config_db::set()函数把interface存储到指定的存储路径。

第四步,在uvm里读取interface,并存储到virtual interface里。

从名字上看,config_db是一种存储配置信息的数据库(类似全局变量,可以想象成一个关联数组),要正确存储和读取数据,需要类型和存储路径同时正确。v_intf有点像是一个指针,把读取的数据存到这个指针对应的存储空间里。

第五步,驱动v_intf的信号。

先初始化所有的信号。由于virtual interface指向了前面实例化的interface,给virtual interface赋值,等同于给真实的interface的信号赋值。

随机发一些激励,这部分与纯sv的写法没有差别。

仿真结果

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

华为深耕海外版图 将在日本设立第二个研发中心2016-11-26 1145

-

邵贝贝书中第二个例子的问题2013-08-08 3546

-

如何使用ESP32并添加第二个无线电模块?2023-04-12 706

-

如何为SPIFFS使用第二个SPI闪存芯片?2023-05-30 675

-

电脑第二个硬盘怎么装2019-03-12 40039

-

谷歌发布AndroidQ的第二个测试版 继续对折叠屏适应2019-04-04 2783

-

苹果macOS Catalina 10.15.1第二个Beta今天发布2019-10-18 3716

-

鸿蒙没有走别人的路 鸿蒙也不是第二个安卓2020-09-19 3048

-

Zoom营收增幅可能连续第二个季度超过300%2020-11-30 2056

-

ASM宣布在新加坡开设第二个车间2022-03-30 2727

-

开发ATtiny微处理器编程器的第二个版本2022-07-25 714

-

两个电阻串联是否影响第二个的电压电流2023-09-01 4901

-

vlookup怎么把第二个重复值显示2023-12-03 6078

-

如何加装第二个路由器2024-10-18 4995

-

DIY 流体模拟吊坠(二):第二个、第三个、更多的吊坠......2025-09-17 2476

全部0条评论

快来发表一下你的评论吧 !