如何应对艰巨的耐辐射电源电子系统设计

描述

太空中的电子系统暴露在大量危险之中。除此之外,如果没有地球保护磁场使粒子偏转,没有地球大气层吸收太阳及宇宙射线,系统将暴露在更大强度的波辐射及粒子辐射中。半导体器件特别容易受到粒子辐射的影响,这可能会导致组件或系统故障。

但即使是无源组件可能也会出现放气等问题。此外,散热也更具挑战性,因为对流散热在太空中不管用,所以设计人员只能通过将热量传导至表面后辐射散掉。

本文将探讨这些问题,具体涉及航天电源系统的设计。这里的重点甚至可进一步聚焦到那些“新太空”应用,它们需要“耐辐射”组件及电路,而非更稳健的“防辐射”器件与电路。耐辐射要求降低了组件或电路承受反射宇宙辐射的能力,例如,组件总电离剂量 (TID) 以更低额定值为单位。然而,作为辐射稳健性程度降低的交换,组件成本也有望降低。

虽然半导体器件的选择是开发耐辐射电源系统的关键,但它只是可部署在组件和电路层面的众多设计策略中的一个。本文将讨论软开关在耐辐射电源系统中的基本战略及多种优势。

粒子辐射及其它危害的影响

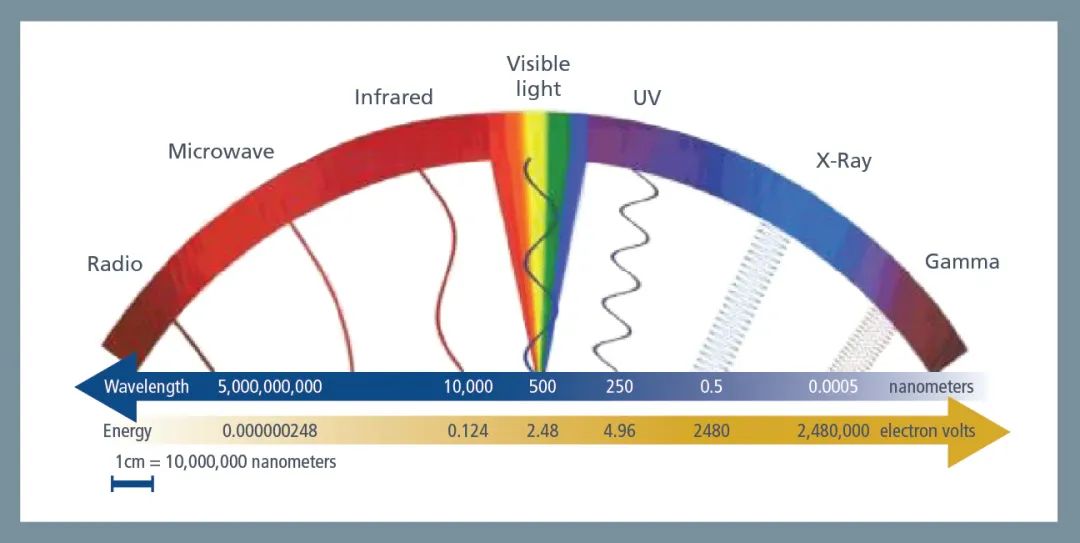

就我们的目的而言,波辐射包括射线和电磁波。关于波辐射的直觉是由人类感官所能探知到的事物引导的,即用我们的眼睛所感受到的可见光、我们感觉有热度的红外光,以及在紫外线灼伤我们的皮肤时我们所感受到的紫外线。

一般来说,波辐射的属性与光的属性相似,包括反射、吸收、折射和传播。然而,宇宙(波)辐射的波长可延伸到可见光光谱的上方和下方。能见度以下的辐射包括微波和射频。能见度以上的辐射包括紫外线、X 射线和伽马射线。在图 1 中,请注意波长和相关能量,这是测量辐射暴露的关键参数。

波辐射和粒子辐射并不是完全分开的两件事,但它们对电子系统的影响是不同的。单个粒子的质量很小,但可加速到很高的速度。此外,它们还可以携带电荷,当负电荷电子从原子轨道剥离时,通常为正电荷。

通过粒子辐射,我们可以看到物理损坏,特别是对半导体晶体晶格的损坏,这种损坏是永久和/或累积性的。在电子被拖入损耗区,使非导电区导电的地方,会出现暂时性的破坏。正离子取代晶体基质中的掺杂原子时,也会出现永久性损坏,有时会使半导体在错误的时间或地方导电,这也会通过电路故障造成永久性损坏。

太空危险重重。大部分辐射损坏都是日积月累的,所以任务时间长短是一个因素。当电子设备离开地球体系时,辐射强度会提升,所以轨道或深空暴露也是影响因素。

太空真空中的另一个影响因素是,我们用于在地面散热的有效对流不起作用。传导的作用是传播热能,但多余的热量最终必须辐射到寒冷的太空中。一个复杂的因素是,暴露在阳光下的表面,温度会变得非常高,大约为 250˚F (120˚C),而阴影覆盖的表面则非常冷,大约为 -238˚F (-150˚C)。卫星系统的散热设计很复杂。

图 1:辐射光谱(插图由哈佛大学提供)[1]。

构建坚固耐辐射电源电子器件的策略

即使在当前快节奏的新太空商业环境中,发射更换报废卫星的成本也非常高昂,因此谨慎设计尤为重要。我们真的希望获得我们力所能及的最高可靠性。

怎么实现?

答案不止一个,创建坚固的航空电子系统的解决方案是多方面的。

根据耐辐射性选择组件。一些业界一流的半导体工艺节点提高了耐辐射性。双极性半导体可根据其位移损坏等级进行选择。可以选择本来就耐辐射的宽带隙 (GaN) FET。有些部件根本不适合在太空环境中使用,如某些环氧树脂和铝电解质容器,它们会在真空中释放气体。

为了说明批次之间的差异,可以对一个批次进行抽样测试,看看其辐射性能。如果通过测试,本次生产的器件即可放心使用。

物理冗余。可执行多个系统实例。一个发生故障,可以设计让另一个系统来接管。在一些系统中,有三个系统并行运行。如果其中一个与另外两个不一致,其输出即可忽略。有时提供有四个冗余系统,如果一个系统出现故障,可换用一个备用系统。

功率 MOSFET 可降额,因此可以考虑不可避免的 VGS 阈值降级,该器件在工作年限之后仍能正常工作。

屏蔽可用于保护敏感电子器件,但如果粒子能量足够高,屏蔽的级联粒子会使问题增加。

如果故障可恢复,可以添加电路来监控性能,断开并重启出问题的系统。

无论设计策略和电源拓扑如何,航天电子系统都必须进行环境及辐射性能分析、仿真和测试。

耐辐射设计要求限制了组件的选择。监控器、安全保护机制、电源断开及复位电路的性能的增加不能导致最终解决方案的效率、尺寸和重量超出要求。

拓扑选择和开关模式的影响

通过选择合适的电源系统架构来平衡设计折中很重要。拓扑和开关模式,如软开关(相对于硬开关电源转换器),可以使系统对振荡等寄生效应不那么敏感,振荡会增加开关组件上的电压应力。

拓扑选择是新太空设计中的重要实例,开关模式会影响电源转换执行的所有重要规范,其中包括功率密度、效率、瞬态响应、输出纹波、电磁干扰 (EMI) 发射与成本等。

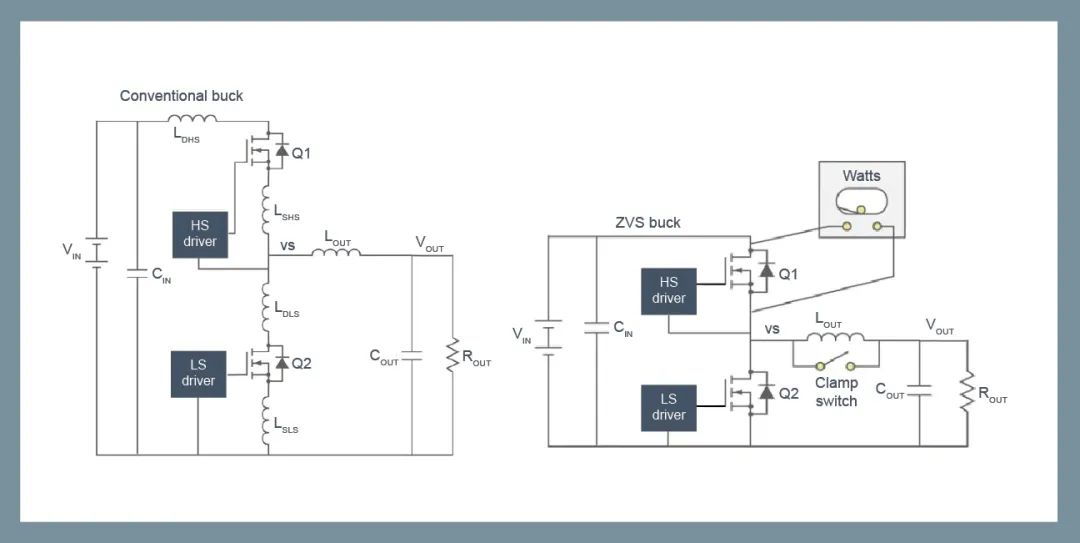

主要开关损耗项可归因为供电链高端 MOSFET 通过栅极充电要求及漏 - 源电容的导通行为。开关损耗随开关频率的增加而增加,从而可限制开关频率。体内二极管导通损耗将进一步降低硬开关转换器的电源转换效率。虽然 GaN FET 没有物理体内二极管,但确实有几伏特的反向传导模式钳位,因此很难管理 GaN 死区传导期。

在同步硬开关降压拓扑中,高侧 MOSFET 在其电压最大(见图 2a)并在接通部分工作周期过程中传导最大电流时接通。因此,高侧开关的功耗在开关切换过程中达到最大值。输入电压越大,功耗越高,因此在相同的转换器中,高电压比应用的转换器(例如,28V 至 3.3V)的效率往往比在要求较低转换比(例如,5V 至 2.5V)的电路中的低。

图 2:辐射光谱(插图由哈佛大学提供)[2]。

软开关的优势

替代方案(软开关)将大幅降低这些开关损耗。软开关技术需要的控制电路更复杂,因为开关时序必须与开关波形协调。

软开关的一个实例是零电压开关 (ZVS) 技术,可提高一系列电源拓扑间的转换效率。顾名思义,当开关的电压为零或接近零时,ZVS 会高侧 MOSFET上实现(见图 2b)。这在高侧 MOSFET 导通间隔期间打破了功耗与电压转换比之间的联系。

支持 ZVS 技术的钳位开关的工作允许转换器在高低侧开关都关闭时,在输出电感器中存储少量能量。转换器可使用这种在其它方面浪费的能量为高侧 MOSFET 的寄生电容放电,并为同步 MOSFET 的寄生电容充电。

将 MOSFET 的寄生电容从开关的导通行为中去除,可降低 MOS FET 针对 CGD 进行选择的敏感性,因此,设计人员可将工作重心从导通电阻与栅极电容等传统品质因数转向导通电阻。

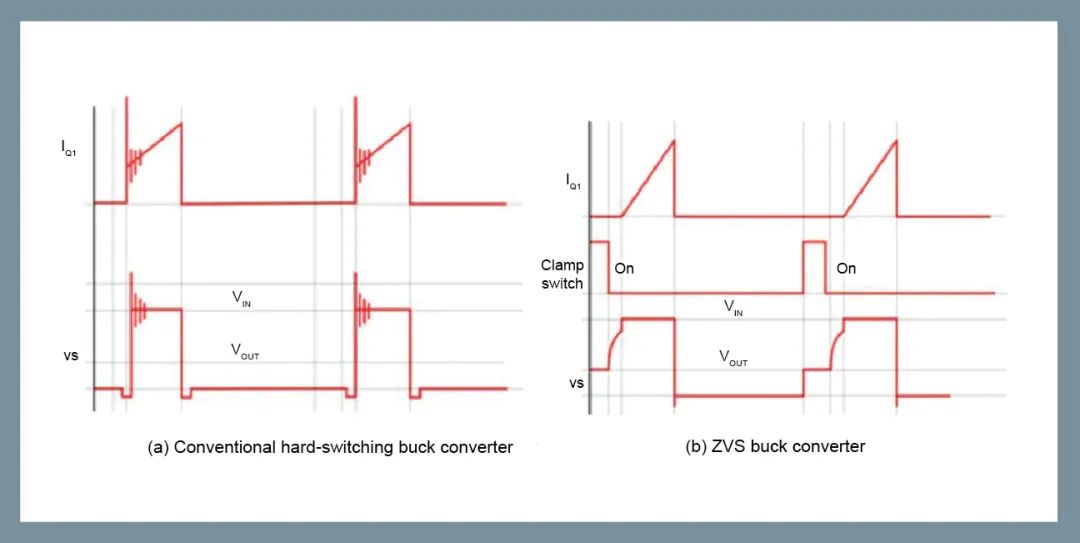

这种在接通过程中驱动高侧 MOS FET 的方法可避免刺激开关寄生电感和电容,这些电感和电容易产生谐振,在硬开关拓扑中诱导大型电压尖峰和振荡(见图 3a)。通过消除尖峰并防止振荡(见图 3b),ZVS 不仅可消除功耗项,而且还可消除 EMI 发射源。

此外,从开关行为中消除电压尖峰可让设计人员选择 RDSON 较低的较低电压 MOSFET,从而提高效率。

图 3:硬开关与软开关波形(插图由《电子设计》提供)[2]。

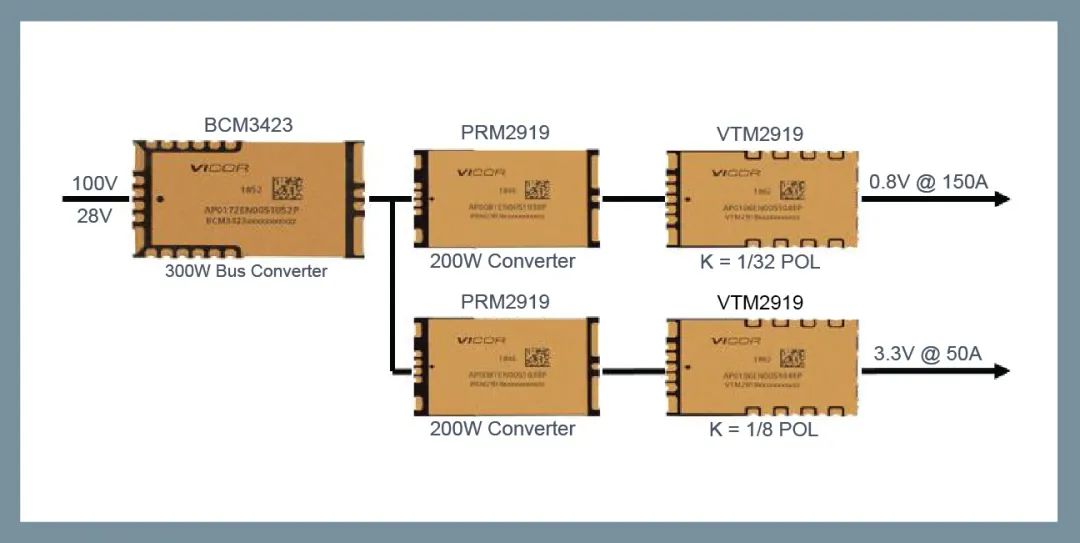

软开关的功能非常广泛。例如,Vicor 在其耐辐射电源模块解决方案中使用软开关技术,为专门用于 MEO 和 LEO 卫星应用的高性能通信 ASIC 供电(见图 4)。系统模块使用 ZVS 升降压拓扑为 BCM 和 VTM 的 PRM 与 ZVS 及 ZCS 正弦振幅转换器 (SAC) 提供支持。

VTM 尺寸小,可以尽可能靠近 ASIC 布置。在应对现代 ASIC、FPGA、CPU 和 GPU 消耗的大电流时,优化配电网络 (PDN) 至关重要。Vicor 模块将软开关解决方案、耐辐射有源组件和符合汽车标准的无源组件进行了完美结合。

为缓解单事件功能中断 (SEFI) 问题,所有耐辐射模块都包括并联运行的完全冗余供电链。如果一个供电链因单个事件而出现故障,其保护电路将强制断电复位。在复位间隔期间,冗余供电链将承担全部负载,而且复位后,两个供电链将再次并联运行。

图 4:高功率谐振(ZVS 和 ZCS)拓扑模块。

在众多因素中,拓扑和开关模式的选择是设计新太空电源转换器时的重要因素。

但本质内容是:耐辐射电子系统很难设计。

Salah Ben Doua

Vicor 首席应用工程师

Salah Ben Doua,首席应用工程师,在电源设计领域拥有 30 年的丰富经验,为 Vicor 客户提供支持已有 20 余载,主要为包括航空航天与国防、工业、铁路、照明与通信在内的众多领域的 DC-DC 和 AC-DC 电源系统开发提供专业技术及咨询。Salah 毕业于图卢兹国家理工学院 (the National Polytechnic Institute of Toulouse),获电源转换专业博士学位。

Ken Coffman

高级现场应用工程师

Ken Coffman,高级现场应用工程师,被指派到 Vicor 新太空计划工作。他住在亚利桑那州凤凰城。

本文最初由 How to power 发表

以上为中译

审核编辑:汤梓红

-

采用增强型航天塑料的 耐辐射电源电压监控器TL7700-SEP数据表2024-04-01 417

-

车身电子系统的控制电源设计2023-11-13 483

-

电子系统中电源如何搞定EMI电磁干扰2023-03-24 1509

-

Microchip推出面向低地球轨道空间应用的耐辐射电源管理器件2023-01-29 861

-

Microchip推出面向近地轨道空间应用的耐辐射电源管理器件2023-01-18 1965

-

天线的发展及其对电子系统的影响是什么?2021-05-27 1826

-

电源 IC 应用在汽车电子系统有什么样的要求?2021-03-06 1865

-

汽车电子系统面临的状况2020-06-24 3300

-

电源设计实用教程——电子系统的电源电路设计2019-09-24 5258

-

汽车电子系统苛刻挑战谁来应对2019-05-13 1851

-

【下载】《电子系统专题设计与制作》2018-04-16 16473

-

电子系统仿真与MATLAB2016-05-04 5300

-

基于DSP的磁控溅射电源的设计与实现(资料下载)2016-01-05 3627

-

现代电子系统中电源技术的发展和应用2009-12-15 1351

全部0条评论

快来发表一下你的评论吧 !