认识一下只有driver的验证平台

电子说

描述

对于一个验证平台而言,最重要的角色是激励的产生,最开始,driver是集合了数据的产生、发送于一体这么一个重要的角色(后面到进入真正UVM会将功能分离)。对于整个验证平台而言,产生激励,将激励送到DUT,收集DUT产生的数据,进行对比,这是最基本的功能。后面一系列的UVM机制,都只是为了能够更好的实现这个基本功能。

这里也强调一点,学习UVM,我个人觉得最重要的是搞清楚,what,where,how。你应该产生什么样的激励数据(what),你的激励是在哪里产生(where),能各个组件之间是怎么连接,数据怎么发送,怎么收集,怎么对比,这就是how的问题。数据在哪里对比,这又是where的问题。能够从数据产生的源头,一路追,追到数据在各个组件里头的流转。就像你找到了一条小溪的源头,你能够沿着这条小溪,一路追下去,直到你明白这条小溪会流经那些村庄,目的地是哪里。

学过verilog的应该知道,verilog里面进行验证,只有两个部分,一个是DUT,一个是tb,这两个组件,组成了最最基本的验证平台,其中,它包含了激励部分,以及代码部分。在UVM中,最基本的验证平台也是由这两部分组成,但是多了一个top_tb.sv的组件。下面,先认识一下这个简单的平台,从代码进行剖析,代码全部来自张强老师的《UVM》实战的源码,张强老师如果觉得我侵权了,请联系我。

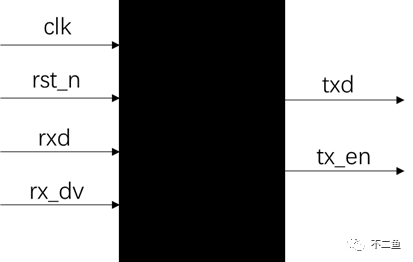

module dut(clk,

rst_n,

rxd,

rx_dv,

txd,

tx_en);

input clk;

input rst_n;

input[7:0] rxd;

input rx_dv;

output [7:0] txd;

output tx_en;

reg[7:0] txd;

reg tx_en;

always @(posedge clk) begin

if(!rst_n) begin

txd <= 8'b0;

tx_en <= 1'b0;

end

else begin

txd <= rxd;

tx_en <= rx_dv;

end

end

endmodule

这个dut确实是很简单。当复位也就是rst_n=0时,将输出数据(txd)和使能(tx_en)都设置为0,否则,将输入给输出。

看到这个DUT,如果让你自己写一个Tb.v,你会怎么写呢?不妨自己写一个,然后再对照下面这个。其实思路也很简答,就是产生相应的数据给四根输入信号,经过dut,看输出的数据。产生时钟给clk,产生复位信号给rst_n,产生数据给rxd,产生使能信号给rx_dv。下面我们来看看driver和tb。

`ifndef MY_DRIVER__SV

`define MY_DRIVER__SV

//这个`ifndef和`define其实就是相当于一个判断条件,便于调用

class my_driver extends uvm_driver;

function new(string name = "my_driver", uvm_component parent = null);

super.new(name, parent);

endfunction

extern virtual task main_phase(uvm_phase phase);

endclass

//这里出现了extern,你翻翻SV的书就知道,只是因为把代码全部写在这个类里面显得臃肿

//所以,在这里用extern留下了一个索引,具体的内容放到class外面

task my_driver::main_phase(uvm_phase phase);//::作用域符号,这个写法就是个规则,记住就行

top_tb.rxd <= 8'b0;

top_tb.rx_dv <= 1'b0;

//这两句相当于初始化

while(!top_tb.rst_n)//这里其实是等待复位结束,否则一直在这里循环

@(posedge top_tb.clk);

for(int i = 0; i < 256; i++)begin// 复位结束之后开始for循环,产生256个数据

@(posedge top_tb.clk);

top_tb.rxd <= $urandom_range(0, 255);//产生随机数,赋值给rxd

top_tb.rx_dv <= 1'b1;

`uvm_info("my_driver", "data is drived", UVM_LOW)

end

@(posedge top_tb.clk);//赋值结束以后,等待时钟上升沿,将rx_dv,重新归零

top_tb.rx_dv <= 1'b0;

endtask

`endif

`timescale 1ns/1ps //时钟精度

`include "uvm_macros.svh"//导入uvm的库文件,才能识别定义的宏变量

import uvm_pkg::*; // 导入uvm的包

`include "my_driver.sv"

module top_tb;

reg clk;

reg rst_n;

reg[7:0] rxd;

reg rx_dv;

wire[7:0] txd;

wire tx_en;

dut my_dut(.clk(clk),

.rst_n(rst_n),

.rxd(rxd),

.rx_dv(rx_dv),

.txd(txd),

.tx_en(tx_en));

//这是信号的例化,相当于把这个文件中的信号,和DUT的输入信号连接起来

initial begin

my_driver drv;//指定一个类的指针,你可以理解为用drv代替了driver.

drv = new("drv", null);//实例化一个driver,不实例化的driver相当于一张图纸

drv.main_phase(null);

$finish();

end

initial begin

clk = 0;

forever begin // forever,永远发生,你还能想到其他方法吗?

#100 clk = ~clk; //这是产生时钟的地方,#是延迟,意思是每隔100个时钟单位,clk进行翻转

end

end

initial begin

rst_n = 1'b0;

#1000; //复位持续了1000个时钟单位

rst_n = 1'b1;

end

endmodule

用vcs进行仿真

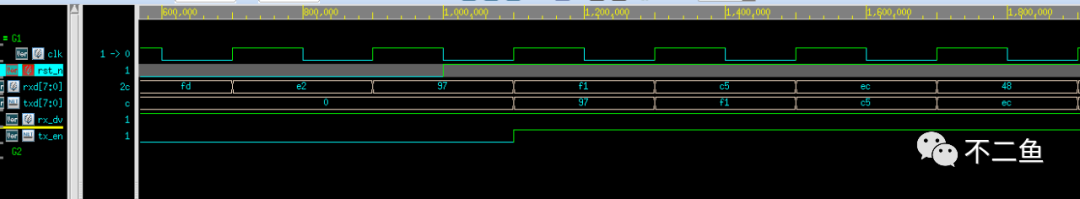

看一下波形:

从波形图中,我们怎么看呢? 看复位 ,是不是在1000个时间单位以前在复位; 看采样 ,复位之后的时钟上升沿是否开始采样,采的样是不是复位之后的有效数据, 看数据 ,数据个数,对照输入输出的数据是否一致;我们就基本可以判定,DUT的功能有没有实现。

-

认识一下NI SWITCH模块的组成和特点2024-03-22 3410

-

认识一下几个常用的门级电路2023-10-09 3492

-

简单认识一下EMC中共模和差模的区别2023-06-08 11219

-

带你认识一下铝电解电容2023-05-16 8903

-

认识一下并列刷写(Parallel Flash)2022-11-15 6083

-

认识一下丙烷传感器2022-09-07 3039

-

认识一下甲醛传感器2022-08-23 2899

-

简单地认识一下D/A和A/D2022-02-24 1549

-

先来认识一下正激的基本原理2021-12-31 3272

-

认识一下针对单片机几个基本概念2021-11-22 1105

-

IC验证"UVM验证平台加入factory机制"(六)2020-12-08 2690

-

IC验证"一个简单的UVM验证平台"是如何搭建的(六)2020-12-04 2819

-

带你重新认识了一下真正的PID2020-10-10 4068

-

认识一下这款名叫“CAN总线存储器”的神器2018-05-20 9059

全部0条评论

快来发表一下你的评论吧 !