如何才能设计一个良好的PDN系统呢?

电子说

描述

电源完整性分析的重要性前面已经介绍过了,可以说良好的PDN设计不仅能为电源传输提供低阻抗的通路、保障电源设计满足各项指标要求,而且良好的PDN也为信号的传输提供了一个良好的平台。那么如何才能设计一个良好的PDN呢?

对于一个板级设计来说,只需考虑板级的PDN设计就足够了。芯片手册会给出芯片对电源的要求通常数字电源+/-5%,模拟电源会有更高的要求1%或者10mV等。一些芯片厂家还会给出PDN阻抗的target,板级的PI工程师只需要按这个要求进行设计就可以了。

但作为芯片公司,就要考虑整个PDN系统的设计。下面就介绍一些PDN设计的系统考虑。

01

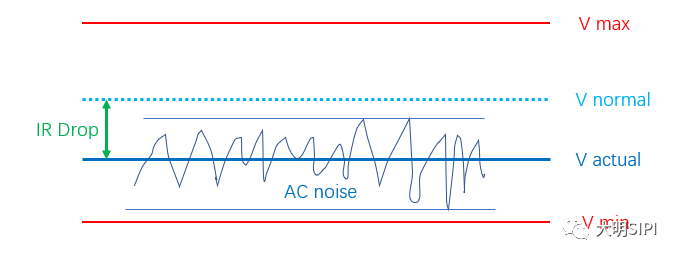

首先,芯片能够稳定工作就需要电源稳定在一定的范围内。如何保证电源的稳定呢?下图红色所示的两条红线(V max、V min)是芯片要求的电源波动范围;浅蓝虚线(V normal)是电源供电的典型电压值;深蓝实线(V actual)是实际为芯片提供的DC电压。

大家可以看出,我这里给的示意图V max和Vmin并不是相对于V normal对称的。是的,通常芯片(Die)上定义的电源波动的范围一般都是向下波动的范围比较宽,如-10%~7%,也就是会把V normal定义得比V max和V min的均值要高一些。这是因为要考虑IR Drop的影响。

V normal到V actual的落差就是PDN上产生的IR Drop,正是由于IR Drop的存在压缩了AC nosie的budget。

因此,要设计PDN就必须为AC noise和IR drop划分budget。

02

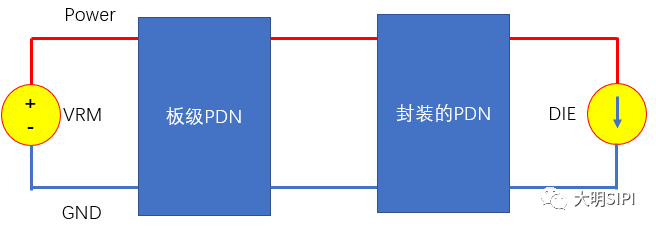

单纯的划分AC和DC的budget显然是不够的,还要从系统级考虑PDN的组成。下图所示是一个简单的系统级PDN示意图。

一个PDN系统从大的方面来说主要包含以下四个部分:

(1)VRM(Voltage Regulator Module):为系统提供电源供应。VRM并不能提供理想的DC电源,其输出也会有一定的电压波动。

(2)板级PDN:由VRM到芯片封装管脚的电源地平面、各种滤波电容以及电源地的布线和过孔等。

(3)封装PDN:由die bump到BGA ball的电源地平面、布线和过孔等。

(4)芯片(DIE):需要VRM向其提供稳定的电源供应。

芯片对电源的需求是明确的,那么如何让VRM提供的电源能够经过板级PDN、封装PDN之后到达芯片的电源能够满足要求呢?这就需要VRM、板级、封装每一级的PDN划分budget。

比如,芯片的电源需求是-10%~7%,可以给VRM和板级分配+/-5%,给封装PDN分配-5%~2%。

然后具体到板级和封装设计还要根据实际情况给AC noise和DC Drop分配budget。

03

除了考虑单一电源自身的设计,还要考虑其它电源噪声以及其它噪声的隔离。比如,在一些高密设计或者成本要求比较高的设计中,通常会存在不同电源平面相邻层铺铜、地平面不完整等非理想的设计,还有一些模拟、PLL等比较敏感的电源距离大噪声的数字电源、时钟信号等噪声源比较近的情况。此时很可能会存在噪声的相互耦合,此时就需要对电源和噪声源进行干扰分析并采取一些隔离措施。

-

用CPU的引脚控制TAS5711的PDN引脚的电平高低,拉低PDN引脚后TAS5711输出没声的原因?2024-11-05 647

-

PDN 元件对阻抗的影响2024-07-13 2162

-

搞定电源完整性,不如先研究PDN!2024-06-12 2333

-

怎样去设计一种PDN电源分配网络呢2021-12-31 1811

-

PDN设计的目的2021-11-11 1551

-

PDN设计2021-11-06 685

-

模拟射频前端部分怎么弄才能搭建一个完整的标签系统呢?2021-06-25 1556

-

PDN 电源分配网络设计步骤 PDN layout步骤2021-06-22 2462

-

如何才能让PCB设计进行良好接地?2021-04-21 1570

-

如何通过PDN指南来设计电路板的供电网络2020-12-25 3420

-

哪些方法可以改善PDN对电源系统性能?2020-10-28 3014

-

PCB制造:PDN设计指南2020-10-13 4173

-

【送书福利】不懂PDN谈何电源完整性?请收下这本PDN设计指导硬核书2019-08-15 14666

全部0条评论

快来发表一下你的评论吧 !