数字IC验证之UVM概述

EDA/IC设计

描述

覆盖驱动验证

UVM提供了实现 覆盖驱动验证(coverage-driven verification ,CDV) 的框架。 CDV结合了自动测试向量生成,自检查和覆盖率收集,显著地缩短了用于验证设计时间。

CDV流程与传统的定向测试流程不同。CDV从验证目标开始,创建一个生成测试向量的测试平台并将其发送给DUT。将覆盖率监视器添加到测试平台中以测量验证进度并确定未验证的功能。添加Checker以识别错误的DUT行为。

仿真在实现覆盖模型和测试平台之后启动。

可以在测试平台的基础结构上,添加约束以尽快达到验证目标。

CDV环境支持定向和随机约束测试。在编写耗时的定向测试去验证复杂的场景之前,先让随机约束测试完成大部分工作。

基于抽象层次的测试平台( 不依赖于实现细节 ),更具可读性和可重用性。

测试平台和环境

UVM测试平台由称为 验证组件 (verification components)的可重用验证环境组成。

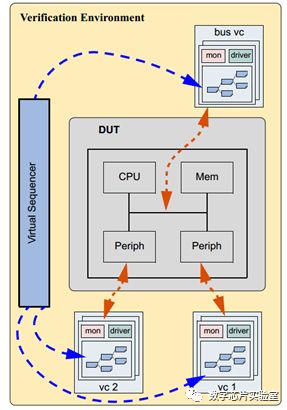

下图显示了具有三个接口验证组件的验证环境示例。

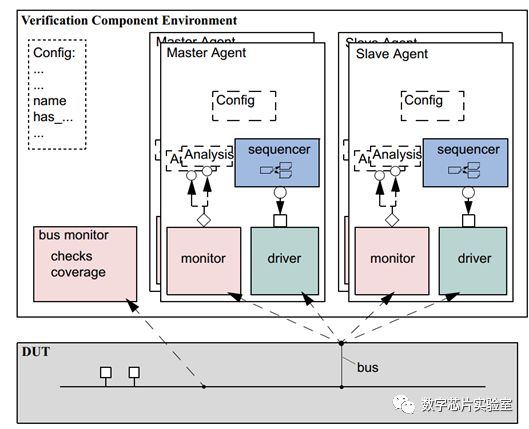

验证组件

数据(Transaction): 数据表示被测设计(DUT)的输入。在测试平台中,使用SystemVerilog随机约束数据,以创建大量有意义的数据和最大化覆盖率。

** Driver (BFM)** :Driver模拟DUT的逻辑。Driver反复接收数据并将其驱动到DUT。例如,控制读/写信号,地址总线和数据总线。

Sequencer: sequencer是一种激励发生器,用于提供给Driver数据。在sequencer中向数据项添加约束,用于控制随机值的分布。

Monitor: Monitor对DUT信号进行采样但不驱动DUT。 Monitor收集覆盖率信息,检查DUT输出是否满足协议规范。Monitor收集事务(数据)。Monitor从总线中提取信号信息并翻译成可供其他组件使用的事务。一般还会在Monitor****中打印跟踪信息。

Agent: Sequencers, drivers, and monitors可以独立重用,但这需要了解每个实体的名称,配置和连接。 为了减少验证工程师的工作量和知识需求,UVM建议验证环境开发人员创建更多抽象容器agent。 agent封装了driver,sequencer, and monitor,可以驱动和监视DUT。

agent应该是可配置的,以便它们可以是active或者passive。 Active agents驱动事务。 Passive agents仅监控DUT。

Environment: Environment是top-level的验证组件。它包含一个或多个agents,以及其他组件。

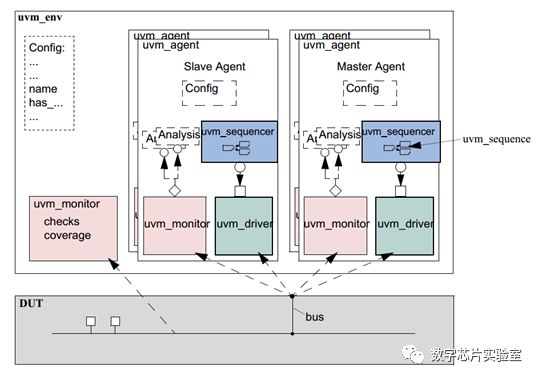

UVM可以提供了验证流程和测试平台基础架构,用户只需要用特定于IP的组件替换一些现有的组件。

UVM类库提供了许多验证所需的功能,下图中的每个组件都是派生自相应的UVM类库的组件。

使用这些基类增加了代码的可读性,因为每个组件的角色都是由其父类预先确定的。

-

ASIC芯片设计之UVM验证2022-11-30 2395

-

数字IC验证之“搭建一个可以运行的uvm测试平台”(5)连载中...2021-01-26 1559

-

数字IC验证之“构成uvm测试平台的主要组件”(4)连载中...2021-01-22 4624

-

数字IC验证之“UVM”基本概述、芯片验证和验证计划(1)连载中...2021-01-21 5222

-

IC验证“UVM验证平台加入objection机制和virtual interface机制“(七)2020-12-09 3674

-

IC验证"UVM验证平台加入factory机制"(六)2020-12-08 2667

-

数字IC设计与数字IC验证哪个好?2020-12-04 2977

-

IC验证"UVM验证平台"组成(三)2020-12-02 2782

-

IC验证"为什么要学习UVM呢"2020-12-01 2733

-

基于UVM的验证平台设计研究2017-01-07 988

全部0条评论

快来发表一下你的评论吧 !