半导体图案化工艺流程之刻蚀(一)

描述

图案化工艺包括曝光(Exposure)、显影(Develope)、刻蚀(Etching)和离子注入等流程。其中,刻蚀工艺是光刻(Photo)工艺的下一步,用于去除光刻胶(Photo Resist,PR)未覆盖的底部区域,仅留下所需的图案。这一工艺流程旨在将掩模(Mask)图案固定到涂有光刻胶的晶圆上(曝光→显影)并将光刻胶图案转印回光刻胶下方膜层。随着电路的关键尺寸(Critical Dimension, CD)小型化(2D视角),刻蚀工艺从湿法刻蚀转为干法刻蚀,因此所需的设备和工艺更加复杂。由于积极采用3D单元堆叠方法,刻蚀工艺的核心性能指数出现波动,从而刻蚀工艺与光刻工艺成为半导体制造的重要工艺流程之一。

1.沉积和刻蚀技术的发展趋势

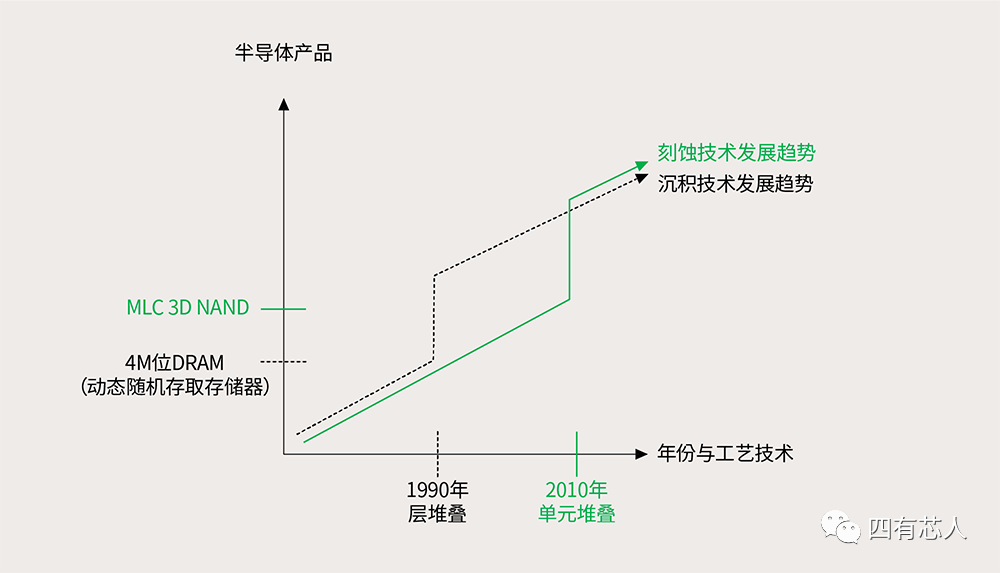

图1. 沉积和刻蚀技术发展趋势

在晶圆上形成“层(Layer)”的过程称为沉积(化学气相沉积(CVD)、原子层沉积(ALD)和物理气相沉积(PVD)),在所形成的“层“上绘制电路图案的过程称为曝光。刻蚀是沉积和曝光工艺之后在晶圆上根据图案刻化的过程。光刻工艺的作用类似于画一张草图,真正使晶圆发生明显变化的是沉积和刻蚀工艺。

自从半导体出现以来,刻蚀和沉积技术都有了显著发展。而沉积技术最引人注目的创新是从沟槽法(Trench)转向堆叠法(Stack),这与20世纪90年代初装置容量从1兆位(Mb)DRAM发展成4兆位(Mb)DRAM相契合。刻蚀技术的一个关键节点是在2010年代初,当时3D NAND闪存单元堆叠层数超过了24层。随着堆叠层数增加到128层、256层和512层,刻蚀工艺已成为技术难度最大的工艺之一。

2.刻蚀方法的变化

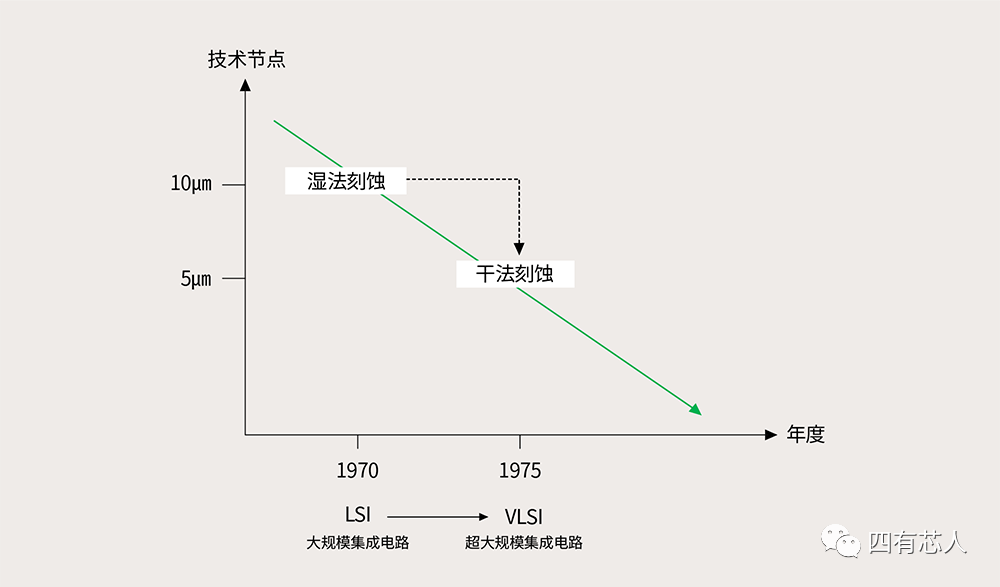

图2. 小型化(2D)与刻蚀方法的发展

在2D(平面结构)半导体小型化和3D(空间结构)半导体堆叠技术的发展过程中,刻蚀工艺也在不断发展变化。在20世纪70年代,2D半导体为主流,电路关键尺寸(CD)从100微米(㎛)迅速下降到10微米(㎛),甚至更低。在此期间,半导体制造流程中的大部分重点工艺技术已经成熟,同时刻蚀技术已经从湿法刻蚀过渡到干法刻蚀。对于层切割技术,最先采用的是化学湿法,这是一种相对简单的技术。由于从20世纪70年代早期开始,化学湿法难以满足5微米(㎛)关键尺寸的要求,从而开发出利用等离子体的干法。发展到今天,刻蚀工艺大多采用干法,而湿法刻蚀技术后来发展应用于清洁过程。

3.湿法刻蚀和干法刻蚀的优缺点

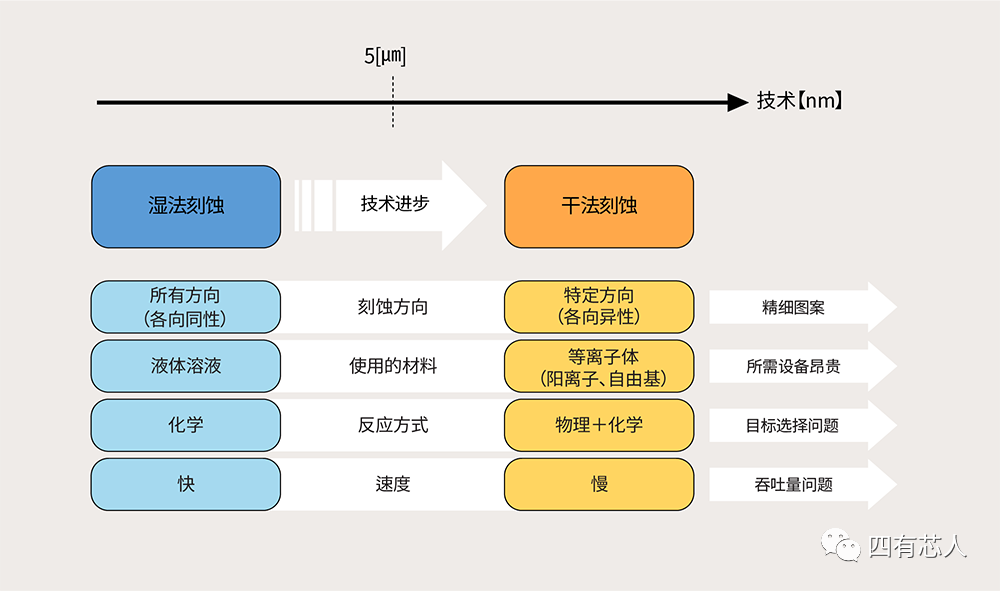

图3. 湿法刻蚀和干法刻蚀的优缺点

湿法刻蚀因为使用液体速度更快,每分钟去除的深度更大,但不会形成类似于直方的结构。湿法刻蚀会均匀地刻蚀所有方向,从而导致横向方向上的损耗,而对于CD小型化应该避免这种现象。相反,干法刻蚀可以在某一特定方向上进行切割,使得实现理想中纳米(nm)级的超精细图案轮廓。

此外,湿法刻蚀会产生环境污染,因为使用过的液体溶液需在此工艺完成后进行丢弃处理。相比之下,采用干法刻蚀时,排放管线中会布置洗涤器,这能够在向大气中排放废气之前经过中和过程,从而减少对环境的影响。

然而,由于晶圆上方数多层复杂地缠绕在一起,所以在采用干法刻蚀过程中很难瞄准某一特定的层(膜)。在针对某一特定层进行刻蚀时,采用湿法刻蚀会更容易进行,因为它采用化学反应进行刻蚀。而在进行选择性刻蚀时使用干法并不容易,因为需要结合物理和化学技术。

4.刻蚀工艺流程及相关问题

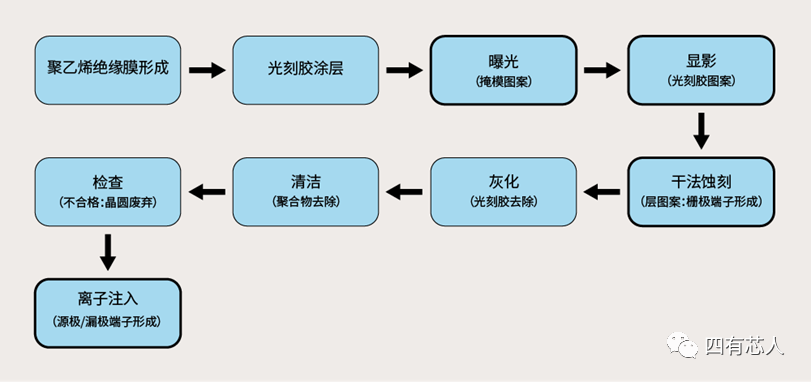

图4. 刻蚀相关工艺流程

刻蚀工艺流程始于形成薄膜,在其上施加光刻胶,并进行曝光、显影、刻蚀、灰化、清洁、检查和离子注入等步骤,以形成三个TR端子,这是半导体制造的核心工艺。如果在显影过程中不能顺利切割光刻胶,则剩余的光刻胶会妨碍刻蚀。如果在刻蚀过程中未能对目标层进行充分刻蚀,则不能按计划注入离子,因为杂质会妨碍离子注入。如果干法刻蚀后未能彻底清除残留的聚合物,也会产生同样的后果。如果由于时间控制失败,等离子体的离子气体量太大或薄膜刻蚀过度,会对下层薄膜造成物理性损伤。

因此,在干刻蚀工艺中精准控制终点(EOP:End of Point)至关重要。彻底检查刻蚀条件以及灰化和清洁过程也非常重要。如果晶圆刻蚀不均匀,则晶圆可能遭到退货,而且刻蚀不足比过度刻蚀更为致命。

由于刻蚀工艺涉及的步骤非常复杂,我打算将其分为两部分进行阐述。在这一部分中,我们阐述了刻蚀技术的历史和发展方向。在下一部分中,我们将对等离子体和刻蚀之间的关系、RIE、刻蚀方法、纵横比以及刻蚀速度进行详细阐述。

-

简述半导体超纯水设备工艺流程及标准参考分析2013-08-12 7137

-

【新加坡】知名半导体晶圆代工厂招聘资深刻蚀工艺工程师和刻蚀设备主管!2017-04-29 5412

-

振奋!中微半导体国产5纳米刻蚀机助力中国芯2017-10-09 16867

-

半导体光刻蚀工艺2021-02-05 7119

-

关于黑孔化工艺流程和工艺说明,看完你就懂了2021-04-23 3507

-

化工工艺流程图阀门程序设计2009-02-14 3441

-

半导体材料的工艺流程2010-03-04 2961

-

半导体工艺流程图2017-01-14 5372

-

半导体知识 芯片制造工艺流程讲解2019-01-26 41640

-

泛林集团自维护设备创半导体行业工艺流程生产率新纪录2019-05-15 1604

-

功率半导体分立器件工艺流程2023-02-24 6442

-

半导体图案化工艺流程之刻蚀简析2023-04-28 4247

-

半导体行业芯片封装与测试的工艺流程2023-05-29 4226

-

半导体前端工艺:刻蚀——有选择性地刻蚀材料,以创建所需图形2023-06-15 3500

-

半导体芯片封装工艺流程,芯片定制封装技术2023-06-26 3561

全部0条评论

快来发表一下你的评论吧 !