补齐重要版图,国产EDA厂商实现全流程数字芯片前端验证!芯华章发布硬件仿真器,EDA2.0战略更进一步

补齐重要版图,国产EDA厂商实现全流程数字芯片前端验证!芯华章发布硬件仿真器,EDA2.0战略更进一步

描述

硬件仿真器被称之为EDA工具皇冠上的明珠,其地位十分重要。近日,国内EDA厂商芯华章正式发布硬件仿真系统桦敏HuaEmu E1,是国内首台可满足150亿门以上芯片应用系统的验证容量的产品。至此,芯华章搭建完整的全流程数字前端验证EDA工具平台。

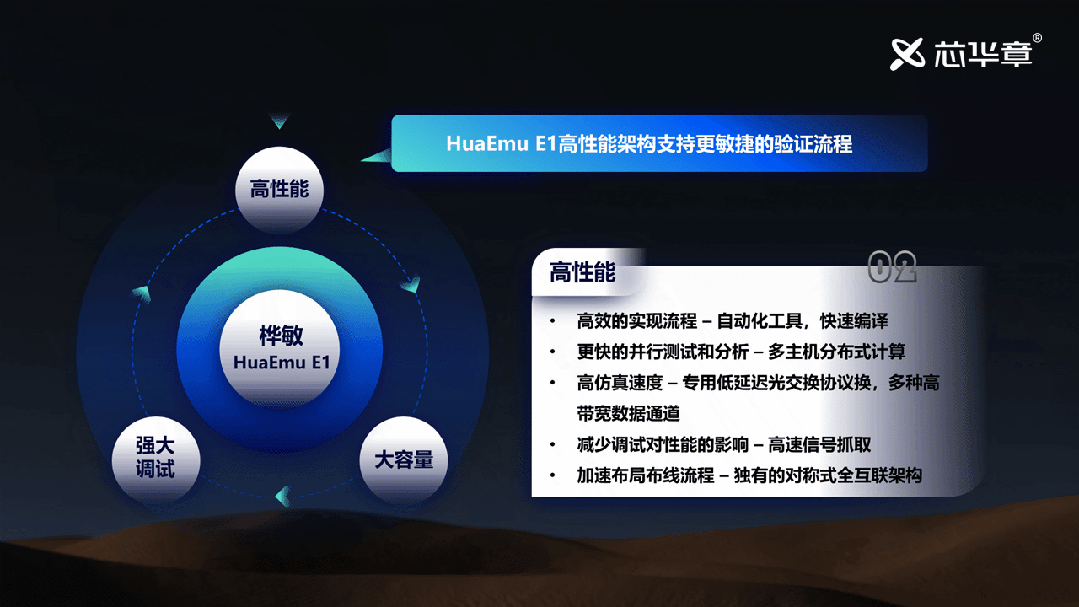

HuaEmu E1三大核心优势

桦敏HuaEmu E1基于自主研发,实现多项国内验证技术突破,具备大规模可扩展验证容量、自动化实现工具、全流程智能编译、高速运行性能以及强大的调试能力,从而极大助力软硬件协同开发,提升系统级创新效率,赋能高性能计算、GPU、人工智能、智能驾驶、无线通信等各种应用领域的开发。在发布会上,芯华章研发副总裁颜体俨博士对桦敏HuaEmu E1的特性做了详细解读。

大容量

桦敏HuaEmu E1支持超过150亿门级的容量,支持目前世界上最高阶、最复杂的芯片。既能够对单一芯片验证,又能够进行几个芯片的系统级验证。另外,在验证芯片时,客户可以利用E1的容量将周边的环境直接在E1中实现,譬如可以用E1来提供足够的存储容量。

验证同一个芯片时,一个芯片设计团队会有很多位的芯片验证工程师,需要同时执行许多的芯片测试,或者验证芯片中不同的模块。E1可以同时支持最高128个用户使用不同的资源,资源的颗粒度可以以2,000万门为单位。基于relocation的能力,不同的使用者可以快速的切换,不需要重新编译,直接移转,这种高效率的使用,也可以支持以后芯华章EDA 2.0云原生的系统。

高性能

以Emulation的执行速度来看,如果一个客户只用到8000门的容量,E1最高的执行速度可以达到10兆赫。如果客户用从8,000万门到3.2亿门,E1最高可以跑到5兆赫,如果超过3.2亿门,E1最高可以跑到一兆赫。

E1内部有快速低延迟的连接,从前端到后端有非常高效的编译流程,E1中对称的互联结构,也使得后端的partition能够更快速的完成。

调试能力

芯片验证过程最花时间的通常是定位问题并解决之,那么强大的调试能力对硬件仿真显得非常重要。

E1能够让使用者读取或看到波形,同时可以看到RTL SystemVerilog的里面所有的讯号,它可以取出无限深度的波形,还具有精准的触发功能。

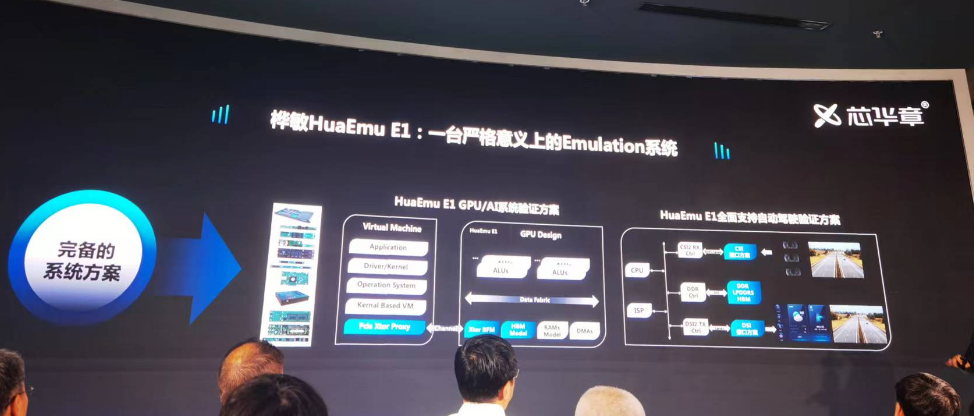

E1能够支持各种验证的方法。E1连接到物理上的真实场景,比如一个GPU用在电玩上时,可以把E1直接连到遥感,另一边连到高清电视。当芯片的RTL完成之后,即使还没有做综合布局布线,就可以马上开始玩游戏。

又以虚拟主机混合仿真为例,验证手机上的APP或者PC的 device driver能否与芯片共同工作,需要依赖虚拟主机的功能,它可以模拟各种操作系统,测试软件在不同操作系统下如何跟芯片共同工作。当芯片验证的过程中,可以把一些资料写在存储上,当验证完以后,把这个资料与标准的预设数据相比较。既可以读取任何信号,也可以调配数值和验证环境,模拟各种状况。此外,如果物理模型不方便建构,同时有C++模型所制造的虚拟仿真环境,E1能够提供高速与主机互联的通道来进行验证。

对于有波形产生的功能,颜体俨谈到波形产生要满足几个条件,第一个全信号可见,第二个要有足够的深度、足够长的波形时间。第三个要高效运行,不把执行速度减低太多。第四个要减低资源的消耗。E1有很多功能,经过灵活的搭配使用,可以满足以上各种的要求,并且随着触发的功能共同使用,可以在运行之间随时换挡,先高速运行到某一种条件之下,再慢下来捕捉更多的波形信号,接着再全速前进。

E1还能够提供远程控制功能,E1的风扇散热可以根据温度的高低自动调节转速,自动监测电压温度等等环境。

进一步来说,桦敏HuaEmu E1由研发团队从头设计,与芯华章其他的验证产品比如GalaxSim、GalaxFV、Fusion Debug使用相容的数据库,产生的波形使用统一的标准,通过Fusion Debug可以观看波形,并分析E1跑出来的结果。

芯华章首席技术官傅勇认为:“HuaEmu E1的发布,标志芯华章彻底搭建了完整的全流程数字验证平台,能够支持超大容量芯片设计完成系统级验证,并有能力进行深度调试。基于芯华章智V验证平台提供的统一底层框架、统一覆盖率数据库和调试系统,我们围绕HuaEmu E1的大容量、高性能与强大调试能力,针对系统应用创新,如智能网联汽车、高性能计算中心、大算力芯片和系统的软硬件开发等,打造了丰富、高效的定制化系统级敏捷验证技术解决方案,可以帮助用户大大提高验证效率,降低研发成本的同时,极大提高产品的创新效率。”

目前,HuaEmu E1已交付多家国内头部芯片设计和系统级用户使用,获得实际项目部署。

不断完善验证产品线,助力国产EDA发展

芯华章资深产品和业务规划总监杨晔表示,E1产品的发布意味着芯华章已经正式进入硬件仿真器市场,硬件仿真器要做成芯华章一个拳头产品,能获得用户的认可,并继续扩张产品方案,逐步地去对标产品线更加完整的国际大厂。

面对当前全球半导体的发展形势,芯华章首席市场战略官谢仲辉表示,尽管全球半导体发展受到多重因素的影响,但哪怕是Synopsys、Cadence等公司在过去多年芯片产业的起起伏伏中,仍然保持着比较好的业绩。毕竟越是低迷不景气的时候,越需要创造新的产品刺激增长。算力芯片就是当前关注度最高的领域之一。

杨晔补充道,以GPU来看,英伟达主流GPU已经达到100多亿门的规模,就必须要有高性能的硬件仿真器。并且主机与GPU放在一个系统里去仿真就需要验证方案的支持。这不仅是一台硬件,而是仿真客户的整个系统。因此,算力芯片的设计更加需要硬件仿真器的助力。

EDA技术发展也在与时俱进,芯华章提出EDA2.0时代降低EDA工具使用门槛,让芯片设计更普惠。对此,谢仲辉谈到,芯华章研究院正在做一些课题,例如将人工智能导入形式验证,用大语言模型或直接用母语转成systemverilog 语言驱动EDA工具,又或者利用AI以数据而不只是看波形来进行调试,还有EDA支持原生云以此灵活提供新的业务模式等等。

据了解,芯华章主要布局在数字前端验证,目前也有部分的工具已经涉及到后端,逐渐拓展产品线,形成更强的系统能力。对于国产EDA企业间的合作也秉持开放态度,谢仲辉表示芯华章主要做数字验证,团队规模在500多人,华大九天也有六七百人的规模,国内EDA企业在各自领域做专做深,再以接口开放标准做融合,流程打通,能发挥国产EDA企业的合力。关于国产FPGA的合作,谢仲辉也表示大容量高性能FPGA有助EDA硬件性能更优,最终赋能编译器和软件。我们也非常关心国产FPGA的进度,积极推动合作。

-

打通系统到后端,芯华章发布首款自研数字全流程等价性验证工具2023-09-19 607

-

国内原型验证市占第一,思尔芯发布硬件仿真系统,提速数字EDA全流程2023-03-23 2261

-

解码国产EDA数字仿真器系列之一 | 从零到一 如何构建一款先进的数字仿真器2023-03-21 1386

-

国产EDA的又一创新,IC前端数字验证的融合之路2022-12-15 1549

-

芯华章研究院携手曦智科技 联合打造芯片验证黑科技2022-11-30 1512

-

后摩尔时代的EDA和芯片设计未来发展趋势2022-08-26 1871

-

芯华章发布四款拥有自主知识产权的数字验证EDA产品2021-12-22 2915

-

【转载】更进一步的了解Keil Flash的下载算法2021-11-26 839

-

如何让计算机视觉更进一步接近人类视觉?2021-06-01 1717

-

芯华章将推出支持国产计算机架构的国产验证EDA工具2020-11-05 971

-

芯华章打造面向未来的EDA产品和系统,进一步提升集成电路设计效率2020-10-01 883

-

芯华章:为中国芯片产业链补齐EDA短板2020-09-24 1016

-

什么是EDA软件?为什么说EDA软件非常重要?2020-09-23 83281

-

关于EDA辅助设计的那些事2020-06-14 2617

全部0条评论

快来发表一下你的评论吧 !