Vivado HLS能否取代HDL开发

描述

大多数FPGA程序员认为,高级工具总是发出更大的比特流,作为提高生产率的 "代价"。但是这总是真的吗?

在本文中,我们展示了一个真实的例子,我们使用传统的RTL/Verilog工具创建了一个普通的网络函数(RSS),然后在相同的硬件上使用高级合成工具(HLS)来实现相同的功能。

我们发现,令人惊讶的是:HLS方法实际上使用了更少的FPGA门和内存。这好像和我们习惯的思维不太一致啊…

通过使用Vivado(Xilinx)或Intel(Quartus)工具,FPGA开发的HLS方法是只抽象出可以在C/C++环境中轻松表达的应用程序的部分。

要想在HLS取得成功,重要的是要认识到项目中哪些部分或模块适合在HLS中实现。基本准则可以概括如下(可能描述不太清楚准确):

目标用途一般是以高级语言开始定义的IP块。一个数学算法会很有效,或者像我们的RSS块那样,一些网络协议处理。

另一类用途是定义不明确的块,因此可能需要多轮的实现。这里最大的好处是允许HLS工具自动对产生的本地FPGA代码进行流水线处理,通常比快速手工编码流水线的阶段要少。另外,当需要修改手工编码的流水线时,一个并行路径上的延迟变化会对所有的东西产生连锁反应。使用HLS工具自动进行第二次流水线,从头开始,消除了这种头痛的问题。

最后,HLS流程使不同FPGA品牌之间的代码移植变得更加容易。这是因为HLS会自动生成适当数量的流水线阶段--这是你在使用Verilog或VHDL时需要手动指定的。

目前HLS的局限性很明显,它的范围限于IP块。应用团队仍然需要其他组件的RTL。还应该注意的是,对于最简单的代码或主要由预先优化的组件组成的大型设计来说,HLS是一个不太理想的选择。

1. 用于做对比的应用,FPGA上的联网RSS

什么是RSS?RSS是 "接收方扩展 "的意思。它是一种散列算法,用于在多个CPU上有效分配网络数据包。RSS是现代以太网卡的一项功能,一般实现微软定义的特定托普利茨哈希。

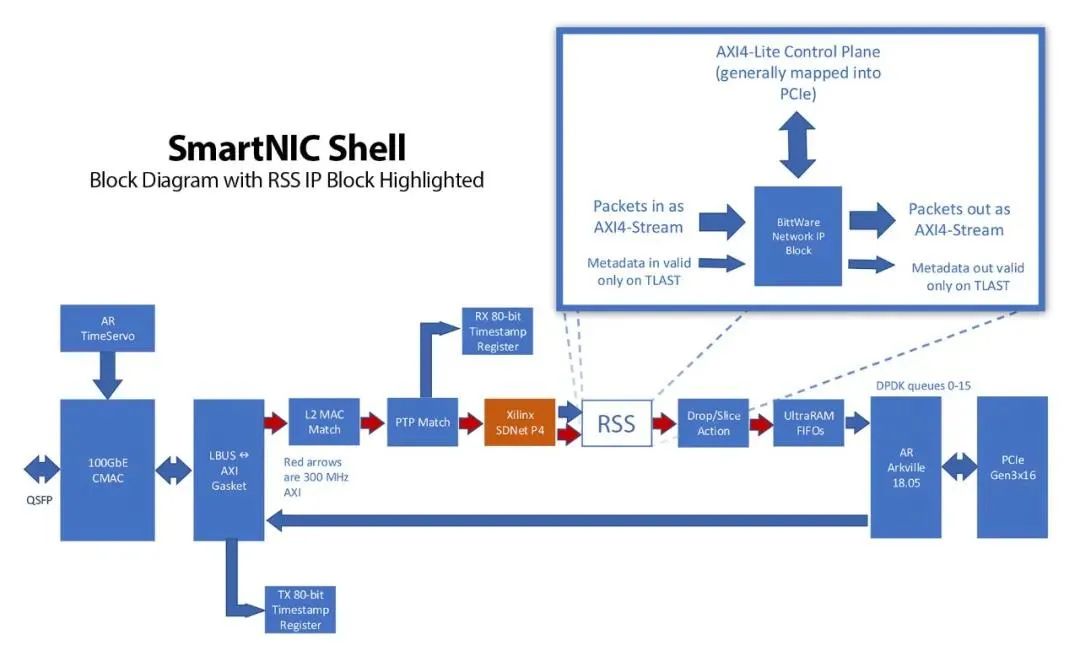

SmartNIC Shell框架的实施实例框图。这里的RSS块被替换成了HLS实现。

2. 用RTL和HLS实现RSS的结果对比

我们评估的假设如下:本地FPGA编码总是导致最小的资源使用。然而,BittWare的一位工程师对这一决定提出了质疑,并在HLS中重新实现了RSS,以测试这一方法。他是对的,现在BittWare已经用HLS代码取代了我们SmartNIC Shell中的RSS模块和解析器模块。

两种实现方式的最大区别是Verilog/RTL版本使用了FIFO,而HLS C++版本没有使用。我们很惊讶地看到,通过转移到HLS,资源的使用量实际上下降了——这与我们预想的差异较大。

开发时间呢?粗略地说,我们看到原生RTL版本的时间线为一个月,而HLS代码在一周内完成。

3. 总结

“今天的高层FPGA开发工具被设计用来减少上市时间和对硬件工程师的依赖。然而,使用这些工具总是带来应用性能的妥协——无论是速度还是硅资源”。然而这种假设是错误的。

我们发现使用HLS为BittWare的SmartNIC Shell开发IP块,将开发时间从大约一个月缩短到一周。我们还发现,它实际上使用了更少的门电路来实现。

审核编辑:汤梓红

-

通过vivado HLS设计一个FIR低通滤波器2026-01-20 532

-

将VIVADO HLS设计移植到CATAPULT HLS平台2023-09-13 813

-

Vivado HLS设计流的相关资料分享2021-11-11 1129

-

探索Vivado HLS设计流,Vivado HLS高层次综合设计2020-12-21 4628

-

极客对Xilinx Vivado HLS工具使用经验和心得2019-07-30 5670

-

关于Vivado HLS错误理解2019-07-29 6310

-

请问如何只下载Vivado HLS 2015.22018-12-27 5567

-

如何使用Tcl命令语言让Vivado HLS运作2018-11-20 3824

-

基于Vivado HLS的计算机视觉开发2018-11-10 1859

-

介绍使用Vivado HLS时的几个误区2018-01-10 20761

-

用Vivado-HLS实现低latency 除法器2017-12-04 1827

-

Hackaday读者有话说:Vivado HLS使用经验分享2017-02-08 900

全部0条评论

快来发表一下你的评论吧 !