向右滑动即可找到与GaN/SiC开关完美匹配的隔离式栅极驱动器

描述

我听说氮化镓(GaN)和碳化硅(SiC)可以在不久的将来取代MOSFET和IGBT功率开关。它们更小更快的事实听起来很棒,但与往常一样,我怀疑没有免费的午餐。在开始考虑在设计中使用GaN和SiC之前,我是否需要注意任何陷阱?

你没听错。随着能源效率变得越来越重要,GaN和SiC晶体管比当前的大功率开关技术更小、更快,看起来完全有望成为人们关注的焦点。但是,这不是一个直接的交换。选择使用它们将对栅极驱动器电路的选择产生影响,我现在将通过几个示例进行解释:

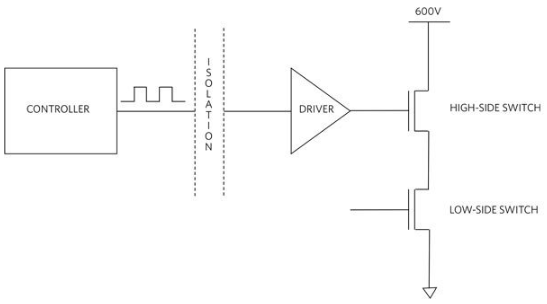

图1所示电路显示了一个电路,其中低压微控制器与高压域(包括输出开关及其栅极驱动器)电气隔离(出于安全原因)。更快的开关速度意味着更快的开关瞬变。例如,GaN功率系统的开关时间通常为5ns(比传统的MOSFET系统快一个数量级)。假设典型的600V高压轨,这会导致(600V/5ns)= 120kV/μs的开关瞬态。

图1.典型的隔离式电源转换器电路。

快速噪声瞬变会破坏隔离栅上的数据传输,或者更糟糕的是,会导致毛刺,从而触发两个功率FET同时导通,从而触发危险的电气短路。为了防止这种情况的发生,对于使用典型120V高压轨的设计,快速开关技术需要至少600kV/μs的栅极驱动器共模瞬变抗扰度(CMTI)。CMTI定义为施加在两个隔离电路之间的共模电压的最大容许上升或下降速率。单位通常为千伏/微秒。高CMTI意味着当隔离栅被高压共模信号击中时,隔离栅两侧的信号电平保持不变(在数据手册限制范围内)。

传播延迟匹配

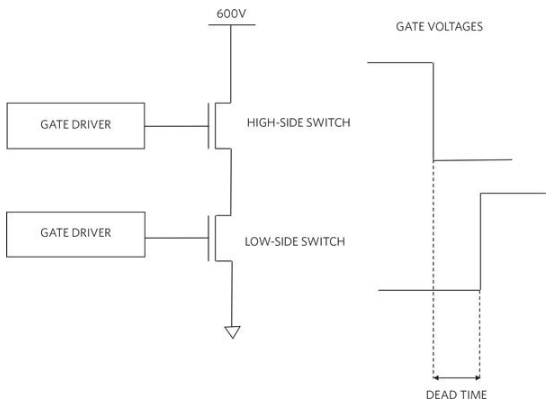

您需要注意的第二件事与开关的开/关时序有关。在图2所示电路中,在任何情况下都不应两个开关同时“导通”,因为这会导致短路类型(通常称为直通)情况。

图2.半桥推挽电路。

为了防止这种情况发生,设计必须允许少量的“死区时间”,其中两个开关都处于“关断状态”。然而,GaN开关即使在反向偏置时也能继续传导一些电流。这会降低效率,因为在此期间并非所有功率都传输到负载。因此,在留下足够安全的“死区时间”和由此导致的效率降低之间需要权衡。要达成最佳解决方案,需要了解各个栅极驱动器器件之间传播延迟的可变性,称为器件间(或具有多个通道的器件的通道间)传播延迟匹配或偏斜。在设计此类电路时,具有尽可能低传播延迟偏斜的栅极驱动器是最佳选择,因为它有助于最大限度地减少死区时间,同时确保永远不会发生“直通”情况。

两全其美

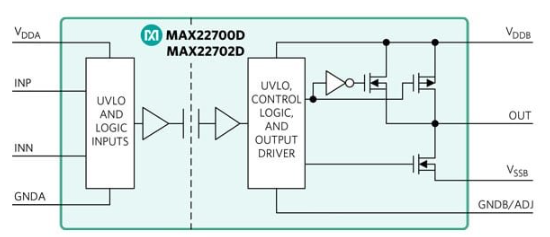

您会很高兴地知道,有一系列隔离式栅极驱动器IC可以解决这两个问题。图3所示为MAX22700D/MAX22702D的功能框图。它们具有 300kV/μs 的最高可用 CMTI 水平。传播延迟偏斜在室温下仅为2ns(最大值),在-5°C至+40°C工作温度范围内为125ns(最大值),有助于最大限度地减少设计中的死区时间,从而提高效率。

图3.MAX22700D/MAX22702D高CMTI隔离栅极驱动器。

这些器件的其他优点包括精密欠压锁定(UVLO),可确保多个器件并联驱动开关在相同的启动电压下工作。在设置SiC晶体管的VGS时,这一点很重要。栅极驱动器公共引脚提供输出选项:GNDB (MAX22700)、米勒箝位 (MAX22701) 和可调 UVLO (MAX22702)。此外,还提供差分(D版本)或单端(E版本)输入版本。隔离栅的耐压额定值为 3kVRMS,持续 60 秒,可提供稳健的性能。这些 IC 可以驱动具有不同输出栅极驱动电路和 B 侧电源电压的 SiC 或 GaN FET。

审核编辑:郭婷

-

SiLM5350SABCA-DG 30V, 10A单通道隔离栅极驱动器2025-11-15 609

-

使用隔离式 IGBT 和 SiC 栅极驱动器的 HEV/EV 牵引逆变器设计指南2024-09-11 386

-

隔离式栅极驱动器的演变(IGBT/SiC/GaN)2023-12-18 940

-

保姆级攻略 | 使用隔离式栅极驱动器的设计指南(一)2023-02-05 1880

-

使用隔离式栅极驱动器的实用设计指南2022-11-14 666

-

使用隔离式IGBT和SiC栅极驱动器的HEV/EV牵引逆变器设计指南2022-11-02 16692

-

ADI隔离栅极驱动器和WOLFSPEED SiC MOSFET2021-05-27 1254

-

隔离式栅极驱动器的揭秘2018-11-01 2594

-

SiC/GaN功率开关有什么优势2018-10-30 3499

-

新型功率开关技术和隔离式栅极驱动器的趋势和格局2018-10-24 2155

-

驱动新一代SiC/GaN功率转换器的IC生态系统2018-10-22 2677

-

实现隔离式半桥栅极驱动器的设计基础2018-10-16 2911

-

实现隔离式半桥栅极驱动器的设计途径2018-09-26 1798

全部0条评论

快来发表一下你的评论吧 !