有没有办法像debug RTL代码一样将UVM中变量拉到波形上看呢?

电子说

描述

我们常用的debug UVM的方法是通过打印log实现。有没有办法像 debug RTL代码一样将 UVM 中变量拉到波形上看呢?答案是有的,下面让我们看看是怎么做到的。

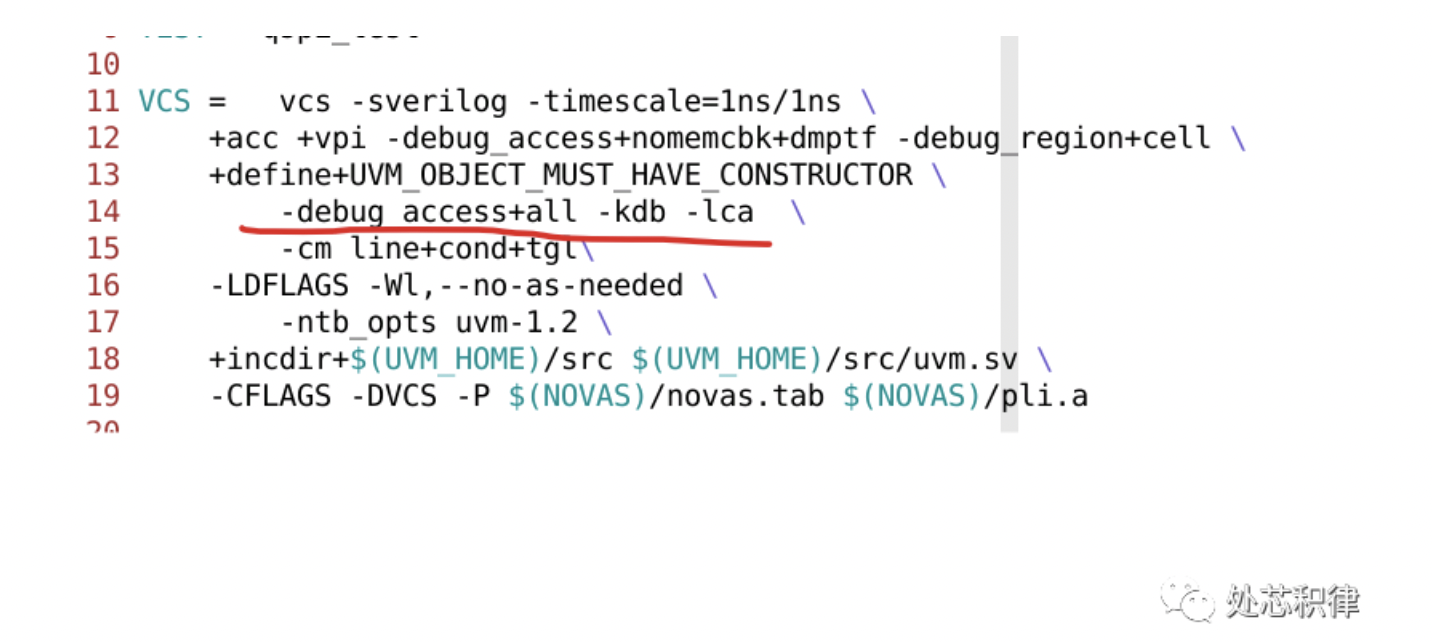

第一步在UVM compile 的选项里面加入 -debug_access+all

第二步在 simulation 选项中加入下面三个选项

-gui=verdi

** +UVM_VERDI_TRACE="UVM_AWARE+RAL+HIER+COMPWAVE"**

+UVM_TR_RECORD

这里 -gui=verdi是启动verdi 和vcs联合仿真。+UVM_VERDI_TRACE 这里是记录 UVM中 register,component 的波形。+UVM_TR_RECORD记录 transaction的信息。

我们 编译完之后,然后开始跑仿真。跑仿真的时候会跳出下面verdi的界面。

接下来点击绿色的箭头就可以跑仿真

跑完仿真之后,我们点击Verdi 里面 UVM这个地方,会出现UVM的环境。

下面我们看下 uvm component里面的信息,通过指定一个 component 然后右击 add to waveform 就可以看 component的信息。

Sequence里面的信息怎么看呢?下面点击sequence view 就可以看 sequnce的信息。

我们要看sequence里面的一个变量变化,可以这么做。

先将一个object或者一个sequence 添加到watch中。

从这个watch中的object或者sequence里面选择一个变量到 waveform上。重跑simulation,就可以看到对应添加变量的值值。

下面是我们在波形上看到sequence里面变量的信息

看register model里面的值也是类似的做法,找到 register view,然后找到 register model 添加 register 到 waveform里面。

重跑simulation,就可以看到register值。

用verdi debug UVM总体感觉比较麻烦,个人还是喜欢打印log的方式debug。

-

IGBT驱动波形负压关断时有上升尖峰,请问有没有办法可以抑制?2024-04-03 29737

-

有没有办法将“/”ext4 分区移动到我的 NVMe 中?2026-03-20 51

-

STC单片机,有没有办法做U盘烧录程序?2015-10-18 5687

-

旧一体机改造成普通主机,请问有没有办法把它改成普通主板一样vga视频输出?2018-08-04 8956

-

有没有办法让全局变量产生警告?2019-08-01 1102

-

有没有办法在运行时查看变量?2019-10-09 2430

-

TouchGFX示波器有没有办法一次刷新多个数据点呢2022-12-20 535

-

有没有办法实现一个像通配符的ButtonWithLabel小部件呢?2023-01-04 658

-

有没有办法使用HAL库来读取地址中指定的变量?2023-01-05 540

-

有没有办法动态改变FTM上的pwm频率?2023-03-21 639

-

求助,有没有办法从配置工具添加#include 或外部引用到“生成的代码”?2023-04-06 621

-

AT+HTTPCLIENT有没有办法打断命令?2023-04-24 755

-

有没有办法保护ESP中的代码?2023-05-08 530

-

如何用Verdi查看UVM环境中的变量?2023-06-25 3157

全部0条评论

快来发表一下你的评论吧 !