功率MOSFET的UIS雪崩损坏模式

模拟技术

描述

功率MOSFET的UIS雪崩损坏有三种模式:热损坏、寄生三极管导通损坏和VGS尖峰误触发导通损坏。

1、热损坏

功率MOSFET在功率脉冲的作用下进入UIS雪崩的工作状态,VDS电压增加,体到epi-结的电场也增加,当场强增加到临界值时(硅中大约为3*e5V/cm),产生载流子的雪崩倍增,导致电流突然急剧增加。雪崩倍增并不是一个损坏的过程,在这个过程中,由于功耗增加导致硅片的结温升高,当结温升高到硅片特性允许的临界值,失效将发生。

传统的平面工艺的功率MOSFET,由于单元密度小、工艺简单,单元的一致性好,沟道产生的热量可以在单元之间的空间很好的传导,在大多数情况下,硅片不同区域的温度差异小,雪崩过程产生的损坏,就完全由硅片整体的热击穿所决定。

功率MOSFET边沿在生产切割过程中可能有应力损伤产生大的漏电流,导致击穿电压和长期稳定性下降,雪崩能力变差,在结构上可以通过在边缘加场板或场环来提高。

2、寄生三极管导通损坏

功率MOSFET在UIS雪崩过程中,电压增加时,体到epi-结的电场也增加,当场强增加到临界值时(硅中大约为3*e5V/cm),产生载流子的雪崩倍增,导致电流突然急剧增加,同时热产生的载流子在外延区形成,产生热点。

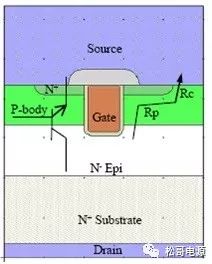

功率MOSFET内部的结构具有一个寄生的三极管,电流流过的通路包括空穴电流流过的路径IH(IH=ID),就有可能产生高的电流密度,当VBE=IH*(Rp+Rc)>0.7V时,基级电流IB增加和三级管的放大作用促使局部的寄生三极管导通。其中,Rp为源极下体的夹挤电阻,Rc为连接电阻。

图1:沟漕MOSFET单元结构:寄生NPN和寄生基极电阻Rp及Rc

此状态发生后,栅极不再能够关断MOSFET的电流。由于局部的不一致性,那些弱的单元,寄生的三极管导通后,NPN管有负的温度系数,在高温大电流的条件下导通,会导致温度越高的单元分担越多的电流,这样在弱的单元,产生电流熔丝效应,从而导致失控发生。

即便是短的低能量的高压脉冲,只有高于临界的电流密度时才发生失效。高的Rp值和Rc值降低了UIS能力,新一代功率MOSFET结构中,如高压超结SJ以及低中压屏蔽栅SGT工艺,采用高电流密度单元结构,三极管放大倍数非常高,虽然Rp值并不大,但是Rp和Rc都会随着温度的增加而增加,射-基的开启电压VBE随着温度增加而减小,UIS能力随温度增加而降低。

同时,新一代的结构工艺复杂,增加了单元性能的不一致性;单元密度大,相互间加热,容易导致发热和温升的局部集中,从而影响UIS雪崩能力。

另外,体内二极管反向恢复期间,漏极的电压快速的上升会使寄生的双极型晶体管导通,漏极电压快速上升,然而少数载流子重组导致发射结正偏,使晶体管导通,器件损坏。以后在二极管的内容中再来讨论。

电感值降低时,电流上升快,功率MOSFET管雪崩产生的热量,由于内部热容的延迟效应,不能及时的耗散出去,更容易导致局部的单元过热而损坏,因此雪崩能量下降。

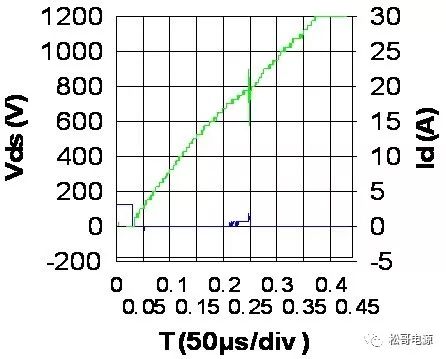

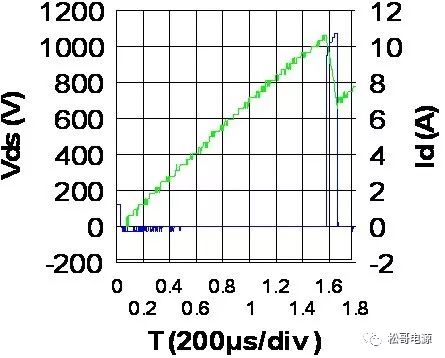

(a) 寄生三极管导通形成损坏

(b) 热损坏

图2:UIS雪崩损坏模式(VDD=150V,L=1mH,起始温度25C)

3、VGS尖峰误触发导通损坏

功率MOSFET在UIS雪崩过程中硅片的温度升高,VGS的阈值急剧降低,同时在雪崩过程中,VDS的电压耦合到G极,在G、S上产生的电压VGS高于的阈值,MOSFET误触发而开通,导致瞬态的大电流流过硅片局部区域,产生电流熔丝效应,从而损坏功率MOSFET,在这个过程中,通常也会叠加寄生三极管导通的损坏机理。

在实际应用中,UIS雪崩较少以这种方式发生失效。

4、雪崩损坏

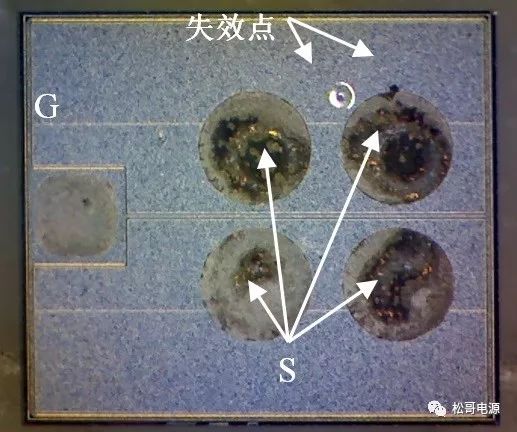

图3示出了UIS雪崩损坏的测试波形和失效图。

(a) 测试波形,L=100uH

(b) 失效图

图3:UIS雪崩损坏波形和失效图

5、什么应用条件要考虑雪崩能量?

在实际的应用中,雪崩的损坏大多是因为多个极端边界条件共同的作用,例如:高温下,系统输出短路及过载测试,输入过电压测试以及动态的老化测试中。过压损坏通常直接理解为雪崩失效损坏,因为雪崩的过程伴随着过压的现象,只有那些在MOSFET的D和S极产生较大的电压尖峰应用,就要考虑器件的雪崩能量。

电压尖峰产生的能量主要由电感和电流所决定,对于反激应用,MOSFET关断时会产生较大的电压尖峰:VIN+输出反射电压+漏感,正常的情况下,有箝位电路,功率器件都会降额,从而留有足够的电压余量,不会出现问题。

但是,在一些极端条件下,测试输出短路启动或工作中短路,然后短路保护起作用,系统关断,然后重起,如此反复,输出短路时,初级电感可能会饱和,产生较大的电流,箝位电路工作有可能不正常工作,漏感产生较大尖峰,器件就会有雪崩损坏的可能,因此在这样的应用条件下,就要考虑器件的雪崩能量。

一些电机负载由于是感性负载,而且启动和堵转过程中产生极大的冲击电流,因此这样的应用也要考虑器件的雪崩能量。

-

功率MOSFET器件的单脉冲雪崩能量参数解读2026-01-20 5159

-

MOSFET雪崩击穿图解 MOSFET避免雪崩失效的方法2024-02-25 7791

-

功率MOSFET雪崩特性分析2023-12-04 2263

-

功率MOSFET的雪崩强度限值2023-05-15 3688

-

看懂MOSFET数据表:UIS/雪崩额定值2023-04-17 2879

-

看懂MOSFET数据表—UIS/雪崩额定值2022-11-18 796

-

看懂MOSFET数据表,第1部分—UIS/雪崩额定值2022-11-03 812

-

UIS测试了解一下?2019-08-29 9085

-

MOSFET数据表之UIS/雪崩额定值2018-09-05 2690

-

功率MOSFET重复雪崩电流及重复雪崩能量2017-09-22 8056

-

看懂MOSFET数据表,UIS/雪崩额定值(一)2015-11-19 5395

-

开关电源中功率MOSFET管损坏模式及分析2013-09-26 1349

-

MOSFET的UIS及雪崩能量解析2010-04-26 9098

-

功率MOSFET雪崩击穿问题分析2009-07-06 6752

全部0条评论

快来发表一下你的评论吧 !