TSV硅转接基板的工艺结构特点及可靠性分析

制造/封装

描述

硅通孔(Through Si Vias,TSV)硅转接基板技术作为先进封装的一种工艺方式,是实现千级IO芯片高密度组装的有效途径,近年来在系统集成领域得到快速应用。TSV硅转接基板的细线条和与芯片相近的热导率可以解决陶瓷基板和芯片之间线宽和热导率不匹配的问题。随着硅基板技术的推广,其可靠性评价是应用前急需解决的问题。目前并没有关于TSV硅转接基板的可靠性评价要求的国内相关标准。从TSV硅转接基板的结构出发,借鉴国军标相关标准,形成了针对硅转接基板的可靠性评价方法,并进行了工程验证。验证结果表明通过有针对性的评价方法,可以反映出TSV硅转接基板的质量特性,实现可靠性评价。

随着三维集成技术的发展,如何将不同材料、结构、工艺、功能的芯片器件实现一体化、多功能集成化是未来系统集成发展的重点。基于TSV、再布线(RDL)、微凸点(Micro Bump)、倒装焊(FC)等关键工艺的硅转接基板集成技术是将处理器、存储器等多种芯片集成到同一个基板上,可提供高密度引脚的再分布。与陶瓷基板、有机基板等类型基板相比,硅基板与硅基芯片之间具有更好的热匹配和更细的导线间距,可实现大规模IO芯片的二维或三维集成。TSV硅转接基板作为中介层,实现芯片与芯片、芯片与基板之间的三维互连,降低了信号延迟与损耗,极大地减小了系统体积,减轻了系统质量。

TSV硅转接基板作为一种高密度集成技术,适合在多功能芯片集成、三维封装等领域应用。但是TSV硅转接基板作为一种基板,在产品应用前需要进行必要的可靠性评价,以满足产品的质量需求。目前的国家标准,诸如GJB2438B-2017《混合集成电路通用规范》、GJB548B-2005《微电子器件试验方法和程序》等总规范中,都没有明确这一类硅转接基板的可靠性评价方法。所以为了满足应用需求,本文以TSV硅转接基板为研究对象,参照GJB2438B-2017标准中基板质量控制的相关要求,开展TSV硅转接基板可靠性评价方法研究。

1 TSV硅转接基板工艺结构及特点

随着芯片I/O数急剧增加,IC芯片的引脚数动辄上千,而传统的陶瓷基板上引线键合芯片扇出的集成度低,不能满足多引脚(>1 000个)芯片的扇出要求。因此,TSV硅转接基板作为中间插入层来弥合基板和集成电路IC间的技术鸿沟。

硅作为基板材料,具有热导率高(85~135 Wm-1K-1)、成本低、化学性质稳定和不透水性好、机械性能理想、一致性良好的特点,且其可控性、与IC芯片的热膨胀匹配良好(Si热膨胀系数2.8×10-6/℃),几乎可作为所有半导体器件和集成电路基板材料。

硅晶圆上布线工艺成熟,精细线条控制能力强。硅基板再布线层采用无机介质做金属间绝缘层时,线宽和线距可做到5 μm甚至1 μm以下;采用有机介质做金属间绝缘层时,线宽和线距通常在5~30 μm范围之内。因此,完全能满足高密引脚IC布线要求。

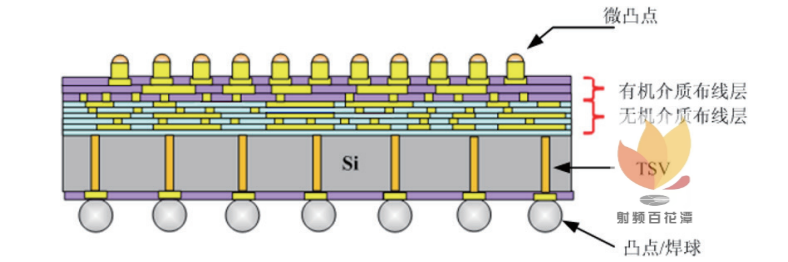

TSV硅转接基板按照结构可以分为凸点扇出型、键合扇出型和混合型。凸点扇出型可以实现千级IO倒装芯片的扇出,实际应用最多,其结构如图1所示。键合型用于键合芯片转倒装焊。混合型多用于多种芯片集成,既有倒装焊芯片二次扇出的要求,也有键合芯片组装的要求,这种转接板尺寸较大。

三种结构的基板制作工艺相近,仅布线层上方有所区别。以常用凸点扇出型硅转接基板为例,硅转接基板的实施从硅晶圆开始,先进行TSV通孔、然后是无机介质多层布线和有机介质多层布线、正面微凸点、背面减薄露头和背面凸点的制作。这种制作方式融合了化学机械抛光、干法刻蚀与湿法腐蚀等多种工艺,可实现厚度达到30~50 μm的超薄硅片。从图1中可以看出,采用TSV通孔和介质布线技术,在Si片上实现了芯片的再布线和上下凸点,实现了微凸点到焊球的二次扇出。

图1 凸点扇出型TSV硅转接基板

2 TSV硅转接基板评价方法研究

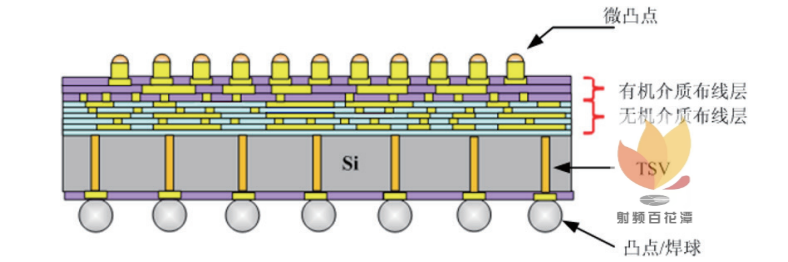

TSV硅转接基板采用的工艺与芯片制造工艺相同,与成膜基片制造方式不同,但是应用用途与成膜基片类似,都是作为IC芯片的承载体。GJB2438B-2017标准中对成膜基片的可靠性评价做出了规定,TSV硅转接基板作为有同样用途的基板类产品,其可靠性的评价应按照成膜基片进行,表1为成膜基片评价要求。

表1 成膜基片评价要求

与薄厚膜这类成膜基片有所不同,TSV硅转接基板的制作采用了TSV结构、凸点制备等手段,其应用场景不仅涉及基片粘接还涉及芯片和基板的倒装焊。因此TSV硅转接基板的可靠性评价还要考虑工艺和结构特点。在成膜基片的评价基础上,应增加共面性检测、倒装芯片拉脱和微凸点剪切力等评价试验。综合上述因素,形成的TSV硅转接基板评价见表2。

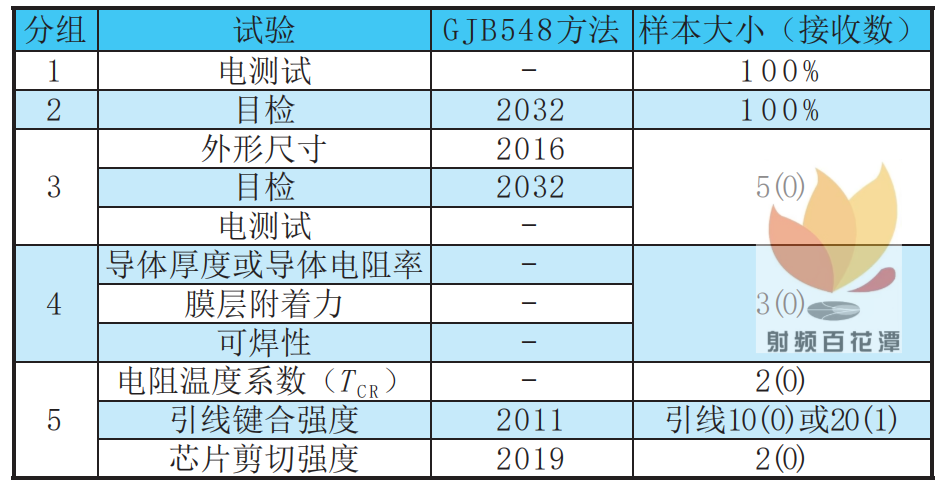

表2 TSV硅转接基板评价

3 TSV硅转接基板可靠性评价试验

以某批次硅转接基板为例,按照表2进行可靠性评价。该硅转接基板是凸点扇出型硅转接基板,没有键合,因此表2中5分组键合强度不用试验。

3.1 试验1(目检)

按照GJB548B-2005标准中方法2010的要求,对每个TSV硅转接基板进行目检,无分层、胶泡等异常情况。

3.2 试验2(尺寸、共面性、版图符合性)

在经过考核试验的TSV硅转接基板中随机选择5颗基板,按顺序进行尺寸测量、共面性检测和版图符合性检查。

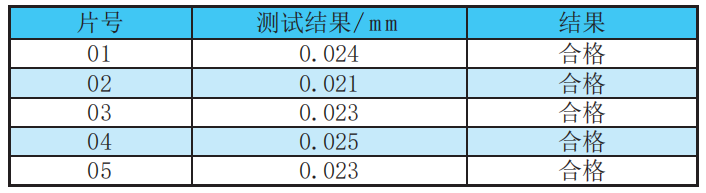

使用共面性检测来评价芯片凸点的共面性,试验方法参照GJB7677-2012标准中焊球共面性进行,由三个凸点顶点形成的平面到置球面有着最大的垂直距离,并且这三个顶点形成的三角形应包含器件的重心。或测量每一个凸点顶点,用最小二乘法拟合形成的基准平面。测量凸点最高点与最低点距基准平面距离之和,100 μm的焊凸球的共面性要求小于0.025 mm。表3是该批次凸点共面性检测结果。

表3 凸点共面性检测结果

3.3 试验3(电测试)

在经过考核试验1的TSV硅转接基板中随机选择5颗基板进行电测试,基于光板飞针测试机,采用测试探针对硅基板上测试点进行逐个测试,从而判断电路板内部各网络节点的通断情况和网络间的电阻值大小。这种直接测试方法,兼顾了可靠接触和测试充分性的要求,既不会造成产品损伤又不影响后工艺加工。该批次中随机选择5颗基板进行电测试,结果全部合格。

3.4 试验4(膜层附着力)

在经过考核试验1的TSV硅转接基板中随机选择3颗基板进行膜层附着力试验。根据百格法,使用3M胶带对TSV硅转接基板进行结合力测试。对样品片用3M胶带在TSV硅转接基板表面上粘接10 cm,注意挤出残留在粘接面内的空气,然后放置3 min,拿住胶带的悬空端使之与基片呈现60°~90°夹角,迅速将胶带从被测膜层表面剥下。在显微镜下进行目检,表面膜层完整,无缺损现象。

3.5 试验5(芯片拉脱)

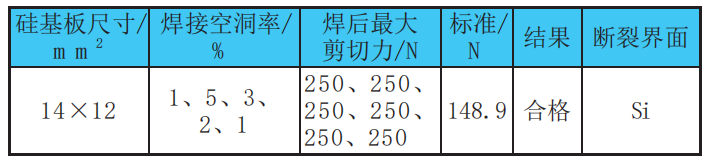

在经过考核试验1的TSV硅转接基板中随机选择2颗基板进行试验5的倒装芯片拉脱。按照GJB548B-2005标准中方法2031的要求,对TSV硅转接基板进行倒装芯片拉脱。表4为该批次芯片试验结果。

表4 芯片焊后剪切强度

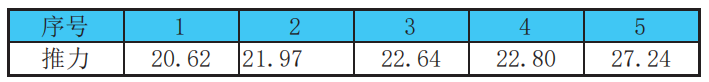

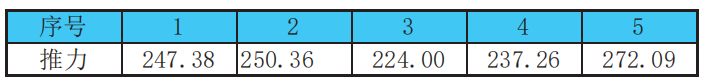

3.6 试验6(微凸点剪切力)

在经过考核试验1的TSV硅转接基板中随机选择5颗基板进行微凸点剪切力,参照GJB 7677-2012标准中焊球剪切方法进行微凸点剪切力测量,结果符合标准要求,具体数据见表5和表6。

表5 正面金属凸点推力测量值

单位:cN

表6 背面凸点下金属层(UBM)植球后推力测量值 单位:cN

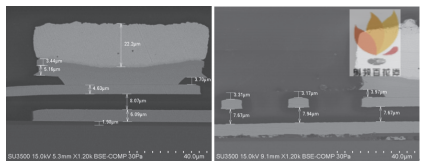

3.7 试验7(DPA)

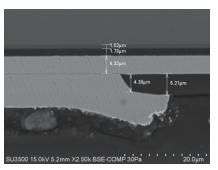

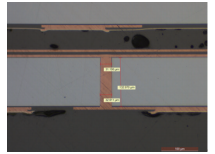

在经过考核试验1的TSV硅转接基板中随机选择1颗基板进行DPA,包括RDL层厚度和TSV填充。按照GJB548B-2005方法2013,对每个TSV硅转接基板进行RDL层厚度、TSV填充结果的检验。使用扫描电镜(SEM)观察RDL层、PI层厚度、TSV填充情况,结果如图2~图4所示。

图2 正面RDL及PI厚度测量图

图3 背面RDL及PI厚度

图4 TSV深孔电镀填充Cu形貌及X-ray结果

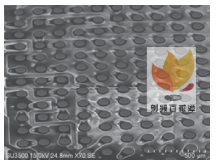

3.8 试验8(SEM检查)

在经过考核试验1的TSV硅转接基板中随机选择1颗基板进行SEM检查。按照GJB548B-2005方法2018,对硅转接基板进行SEM检查,表面无分层等异常,结果如图5所示。

图5 TSV硅转接基板表面SEM图

4 结论

本文针对TSV硅转接基板的可靠性评价方法开展了研究,分析了TSV硅转接基板的工艺结构特点,借鉴国军标中成膜基片的可靠性评价方法,针对硅基板中特有的工艺结构开展有针对性的评价试验,形成了TSV硅转接基板的可靠性评价方法,并以工程中实际应用的一款TSV硅转接基板为例,开展了评价验证试验,确定了评价方法的可行性。

编辑:黄飞

-

提供半导体工艺可靠性测试-WLR晶圆可靠性测试2025-05-07 7188

-

电机微机控制系统可靠性分析2025-04-29 324

-

浅析TSV硅转接基板的可靠性评价方法2023-06-16 1722

-

PCB线路板可靠性分析及失效分析2021-08-05 6724

-

航天电连接器的可靠性重要分析2021-03-25 4274

-

硅通孔(TSV)电镀2021-01-09 3857

-

电子线路板热可靠性分析与判断2018-09-13 1785

-

EGS通信网络可靠性分析研究2017-08-31 1029

-

石化工业仪表电源系统的可靠性分析2017-02-07 988

-

基于时序模拟的并网型微网可靠性分析_王玉梅2017-01-08 844

-

【可靠性分析第一步】构造可靠性模型2016-09-03 3329

-

飞机薄壁结构的可靠性分析2011-05-18 1188

-

单片机复位电路的可靠性分析2010-10-23 3908

-

[分享]电路板可靠性分析2009-05-18 9341

全部0条评论

快来发表一下你的评论吧 !