ASIC数字设计:前端设计、验证、后端实现

描述

前端设计

数字系统设计中有三个重要的设计级别概念:行为级(Behavior Level)、寄存器传输级(Register Transfer Level)和门级(Gate level)。其中,

行为级通过行为级算法描述数字系统;

寄存器传输级通过寄存器之间的数据传输进行电路功能设计,例如有限状态机;

门级按AND、OR、NOT、NAND等等描述,通常不会进行门级设计,门级网表一般是通过逻辑综合的输出。

RTL可以用Verilog或VHDL描述。Verilog是一种用于描述数字系统的硬件描述语言(HDL),例如Latches、Flip-Flops、组合逻辑、时序逻辑等。基本上,你可以使用Verilog来描述任何类型的数字系统。设计通常以自顶向下的方式编写,系统具有层次结构,使得设计和调试更容易。verilog模块的基本框架如下:

module top_module(

input clk,

input rst,

input [7:0] in_data,

output [7:0] out_data

);

// Instantiate submodules here

// Your code here

endmodule

模块实例化(module instance)时,需要指定被实例化的模块名称(例如NAND或INV)、实例名称(在当前模块中唯一标识该实例)和端口连接列表。模块端口连接可以按照位置顺序(位置映射)或者名称对应(命名映射)给出。一般推荐使用命名映射,因为可以避免一些错误。

1.按名称进行端口映射:

INV V2(.in(a), .out(abar));

2.按顺序进行端口映射,这种情况下,端口列表的顺序要和被实例化的模块一致:

AND A1(a, b, d);

下面是一个简单的D触发器 Verilog示例代码:

module dff (q, d, clk, rst);

output q;

input d, clk, rst;

reg q;

always @(posedge clk or posedge rst)

if (rst)

q <= 0;

else

q <= d;

endmodule

数字电路设计分为组合逻辑和时序逻辑两种。

用Verilog编写的代码并不一定都能综合成电路。我们需要保证我们的代码能综合出我们想要的电路。在Verilog中,有些与时间相关的语句是不能综合的。比如,wait, initial, delay等。

在Verilog中,可以用always语句块来建模电平敏感和边沿敏感的电路行为。

用always语句块建模组合电路时,要注意每个输出都要依赖于敏感列表。如果没有完全指定组合电路,可能会综合出锁存器(latch)。

验证

在数字系统设计完成后,要用仿真来验证逻辑功能是否正确。在Verilog中,可以用testbench(测试平台)来检验代码。编写testbench的一些基本原则如下:

1、Testbench要实例化设计的顶层模块,并给它提供输入激励(stimulus)。

2、设计(DUT)的输入激励要用'reg'类型声明。'reg'类型的数据可以在always或initial语句块中改变。

3、设计(DUT)的输出要用'wire'类型声明。'wire'类型的数据不能在always或initial语句块中赋值。

4、always和initial语句块是两种时序控制块,它们是并行执行的。initial语句块的一个例子如下:

module testbench;

// 定义clk和reset信号

reg clk, reset;

// 定义被测模块的实例

dut dut_inst(

.clk(clk),

.reset(reset),

// 其他端口

);

// 在initial块中生成clk和reset激励

initial begin

// 初始化clk和reset为0

clk = 0;

reset = 0;

// 等待一段时间后释放reset

#10 reset = 1;

// 每隔5个时间单位切换clk的值

forever #5 clk = ~clk;

end

endmodule

initial语句块在仿真开始时(时间为0)按照“begin end”之间的语句顺序执行。遇到延迟时,该语句块暂停执行,等待延迟结束后继续执行。上面的代码是一个比较典型的复位和时钟激励生成的代码。

5、系统任务。这些系统任务不会被综合工具识别,所以可以在设计代码中使用它们。系统任务以$符号开头。一些常用的系统任务如下:

$display:在仿真过程中,在屏幕上显示文本信息

$stop:暂停仿真。

$finish:结束仿真

$dumpvar,$dumpfile:生成波形文件,保存到指定的文件中。

6、tasks用于实现常用的验证功能。tasks可以有输入,输出,并且可以包含时序控制。下面是一个task的例子:

// 定义一个带有时序延迟的task

task delay_task;

input [7:0] data; // 输入数据

input [3:0] delay; // 输入延迟时间

output [7:0] result; // 输出结果

reg [7:0] result; // 定义寄存器存储结果

begin

#delay result = data; // 延迟赋值

$display("data = %b, delay = %d, result = %b", data, delay, result); // 打印结果

end

endtask

// 定义一个模块调用task

module test;

reg [7:0] data; // 定义数据信号

reg [3:0] delay; // 定义延迟信号

wire [7:0] result; // 定义结果信号

initial begin

data = 8'b10101010; // 初始化数据

delay = 4'd10; // 初始化延迟

delay_task(data, delay, result); // 调用task

#20 $finish; // 结束仿真

end

endmodule

上面的代码的功能是定义一个带有时序延迟的task,然后在一个模块中调用它。

7、编译指令`timescale设置时间单位和时间精度

`timescale 10ns/1 ns // 单位 10 ns,精度 1 ns

8、 Verilog测试平台可以使用包含C语言描述的编程语言接口(PLI)。

9、 在编写testbench之前,了解设计规范(spec),并且创建所有可能的测试用例列表非常重要。

10、 可以根据波形检查信号值是否正确。

11、 在编写testbench时,可以设置断点,也可以单步执行。

12、 进行功能仿真时,最好进行受约束的随机仿真。受约束的随机仿真可以提供有效输入的随机组合。当随机仿真运行很长时间时,它可以覆盖大部分的corner cases。在verilog中,可以使用$random在testbench中创建随机变量。

13、覆盖率统计:观察存在多少种可能性以及有多少种可能性已经通过仿真。

13.1、行覆盖率:代码中的行仿真覆盖百分比,由仿真工具统计。

13.2、条件覆盖:它检查代码中的各种条件语句覆盖百分比。

13.3、状态机覆盖率:检查状态转换覆盖百分比。

14、 回归测试(Regression):将新的模块添加到已验证的代码中。回归测试是一种验证方法,用于确保修改或更新后的代码不会影响原有的功能和性能。

仿真目标

功能正确:通过验证来验证设计的功能,主要的test cases(主要功能)和corner cases(特殊条件下)。功能正确是仿真的基本要求,确保设计符合规范和预期。例如,可以使用assertions来检查设计的输出是否与预期相符。

设计的错误处理:通过验证来检测设计中可能存在的错误或异常情况,并测试设计如何应对或恢复。设计的错误处理是仿真的重要目标,提高了设计的可靠性和安全性。例如,可以使用fault injection来模拟设计中可能发生的故障,并观察设计的反应和行为。

性能:通过验证来评估设计的性能指标,如时延,吞吐量,功耗等,并与设计目标进行比较。性能是仿真的重要目标,影响了设计的效率和优化。例如,可以使用profiling tools来分析设计中各个部分的资源占用和执行时间,并找出性能瓶颈和改进点。

真实世界仿真

在软件的功能仿真之后,如何在真实世界中仿真你的设计呢?

FPGA原型:加快验证速度。

硬件加速器:将一些可综合的代码映射到FPGA上。其他不可综合的部分,如testbench用仿真工具驱动。当设计非常大时,这种硬件加速验证方法能大幅度提高验证效率。

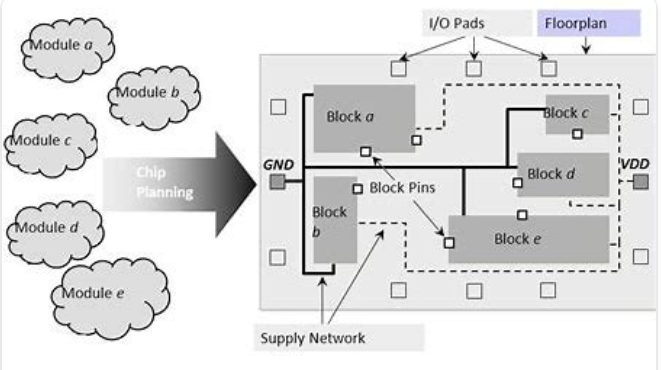

后端实现

在数字物理设计流程中需要对多个目标进行优化,包括面积,走线长度和功耗,以及需要确保物理实现之后的网表满足设计的时序要求。以下将概述芯片数字后端的基本步骤:

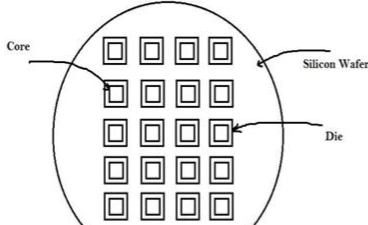

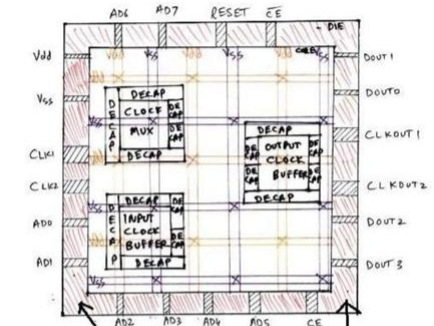

物理设计的第一步是floor planning,定义芯片(die&core)的宽度和高度,也就是芯片的面积。

“core”是芯片的核心区域,用于放置(place)设计的基本逻辑单元。芯片是从晶圆(wafer)上切割出来的,晶圆是一种圆形的硅片,上面可以制造多个芯片(die)。

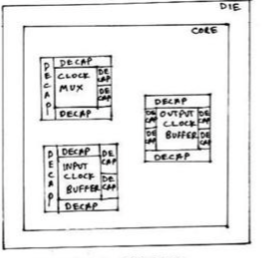

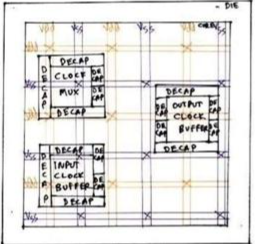

在布局布线(P&R)阶段,工具会根据约束条件来放置逻辑单元。在正式进行P&R之前,需要先确定一些关键模块的位置,例如RAM,ROM等。这些模块被称为“预放置单元(preplaced cells)”。

将关键模块摆放之后,围绕关键模块摆放Decap(decoupling capacitors),提高了芯片的可靠性和效率。

在电路原理图中,我们通常只看到一个“Vdd”和一个’Vss’,表示电源和地。但是,在芯片上,我们需要构建一个电源网络,将电源和地分布到各个模块。在floorplan阶段,我们还需要放置引脚(pin)或焊盘(pad),用于与外部设备连接。引脚是模块级别的接口,焊盘是芯片级别的接口。

在floorplan确定(freeze)后,就可以开始布局布线(P&R)了。P&R工具的输入包括综合后的门级网表,时序库,物理库和设计约束。P&R工具根据设计约束(constraints),例如时钟频率,时序裕度(margin),最大电容等,用算法来确定标准单元(Flipflops,AND,OR,BUFFER等)的位置,并把它们放在core里。

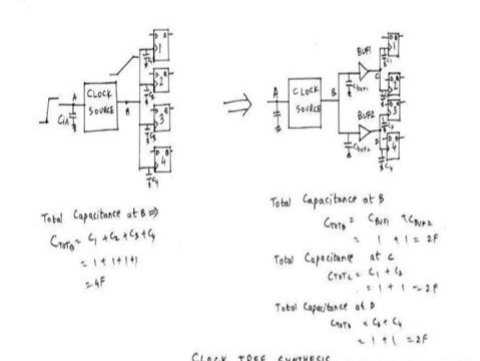

假设时钟网络的最大电容限制是2F。看看上面的图,时钟节点’B’连着4个触发器的’clk’脚。假设每个触发器的’clk’脚的电容是1F。那么,PNR工具就会算出节点’B’的总电容是4F。然后它会把这个电容和约束文件里的最大电容2F比较。

因为节点’B’的电容超过了2F,工具就会用2个buffer把节点’B’的负载分开,就像图上那样。它从库里选buffer(假设每个buffer的输入电容是1F),并建一个树(时钟树),来满足设计的最大电容约束。这个过程叫做’时钟树综合(Clock tree synthesis)'。

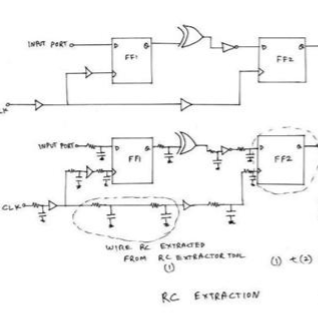

最后,物理设计完成后,PNR工具会对原来的网表做一些修改。比如:加buffer,调整单元大小(size)等。然后,可以提取电阻和电容的值RC(resistances、capacitance),把它们保存在一个文件里,一般叫做SPEF(Standard Parasitic Extraction Format)文件。

最后,要用静态时序分析(STA)工具做timing sign off。静态时序分析(STA)工具会检查设计的各条路径是否符合约束文件里的时序要求,包括建立时间检查,保持时间检查,最大电容检查和过渡时间检查等(Setup check,Hold check, Max Capacitance check 和 Transition Check)。

设计约束

3、指定设计约束

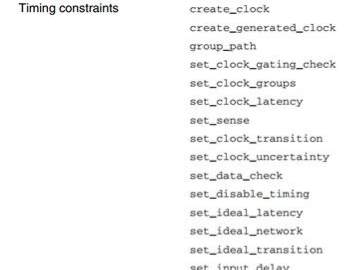

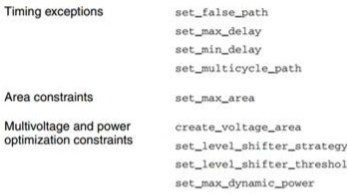

SDC(Synopsys Design Constraints)是一种基于Tcl的格式。SDC文件里的所有命令都遵循Tcl的语法规则。SDC文件用来告诉EDA工具设计的意图,包括时序、面积和功耗等。SDC文件包含以下信息:

•版本(可选)

•单位(可选)

•约束值

•约束对象

•注释(可选)

SDC文件里不包含加载或链接设计的命令。所以,在读取SDC文件之前必须先读取你的设计。

1、指定SDC版本

如果没有指定SDC版本,那么版本就取决于读取SDC文件的EDA工具。为了保证SDC文件在不同工具之间的兼容性,可以在文件开头用以下命令指定SDC版本:

set sdc_version value

2、指定SDC单位

set_units命令指定SDC文件里的电容,电阻,时间,电压,电流和功耗等单位。

3、指定设计约束

用约束命令来指定设计约束。如果命令太长,可以用反斜杠字符()把命令分成多行。SDC约束命令有下表这些。

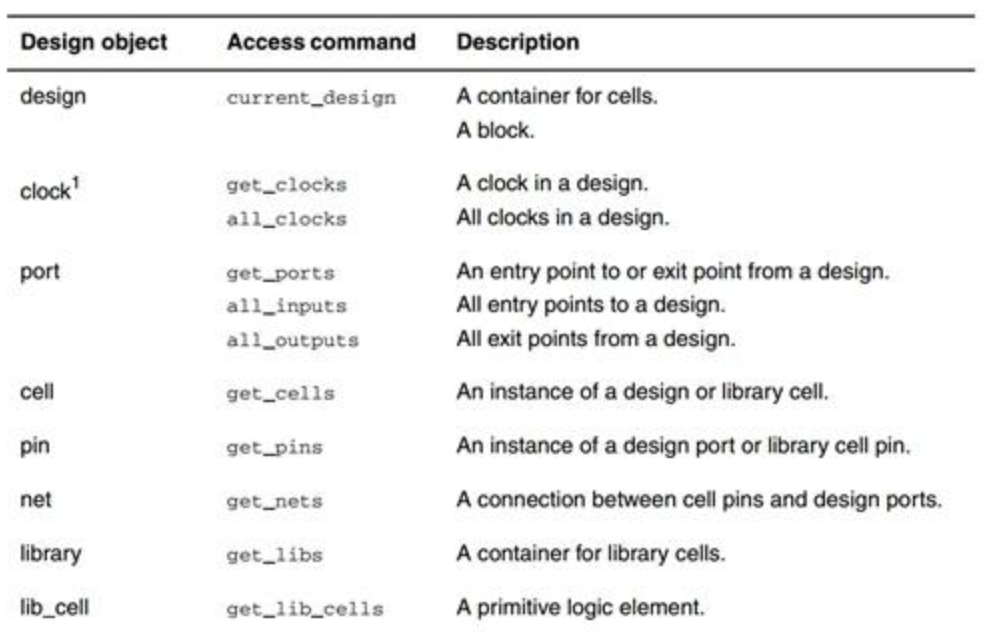

4、指定约束对象

大多数约束命令都需要设计对象作为命令参数。

如果当前设计中有一个名为U1的单元,可以通过命令

[get_cells U1]

找到。下表SDC格式中寻找设计对象的命令。

同时,可以使用Tcl列表或通配符(?、*)指定多个对象。默认情况下,当前设计约束的参考点是顶级设计。我们可以使用分隔符(/)来约束层次结构化设计。

5、添加注释

可以使用#将注释添加到SDC文件中。

例如,

# This is an SDC comment line.

create_clock -period 10 [get_ports CLK] ; #comment fragment

6、管理大型项目SDC文件

当设计非常大时,SDC文件可能会得很大。减少SDC文件大小的一种方法是压缩文件

read_sdc命令自动检测gzip压缩文件并解压缩,然后读取它们的文件。例如,

read_sdc design.sdc.gz

审核编辑:汤梓红

-

典型的基于RTL的ASIC设计流程分析2022-06-20 6731

-

【高端人才招聘】格见半导体 资深数字后端工程师2026-03-14 554

-

IC前端和后端设计的区别2011-12-19 43849

-

集成电路前端及后端设计培训2012-05-16 3135

-

数字ASIC/SOC芯片后端设计工程师2014-06-05 2995

-

[招聘] 新思科技(Synopsys)上海/西安招聘数字前端AC2017-03-03 3058

-

【招聘】职位包括数字IC设计/验证/后端物理设计、模拟IC设计/版图工程师2017-04-05 3170

-

ASIC原型验证的实现2019-07-11 3099

-

数字IC后端设计介绍,写给哪些想转IC后端的人!2020-12-29 4386

-

如何去实现一种数字前端的设计?包括哪些步骤?2021-06-18 1501

-

数字IC前端和后端有何区别2021-07-28 5803

-

数字IC前端后端的区别,数字IC设计流程与设计工具2021-11-06 2450

-

芯片设计分为哪些步骤?为什么要分前端后端?前端后端是什么意思2023-12-07 6608

-

模拟前端和数字后端哪个好 模拟前端和数字后端的区别2024-03-16 2253

-

数字电路设计中:前端与后端的差异解析2025-02-12 2101

全部0条评论

快来发表一下你的评论吧 !