详解Verilog赋值语句、块语句、条件语句

电子说

描述

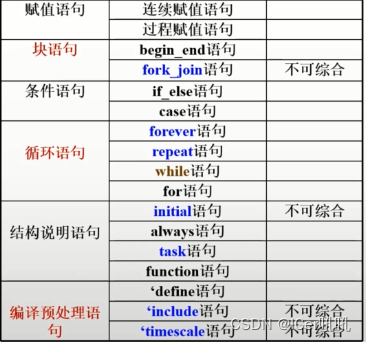

不可综合语句经常用在测试文件中,未注明的语句均是可综合的

赋值语句

1.连续赋值语句——assign语句,用于对wire型变量赋值,是描述组合逻辑最常用的方法之一。

例:assign c=a&b; // a,b,c 均为wire型变量

2.过程赋值语句——用于对reg型变量赋值,有两种方法:

非阻塞赋值方法:符号<=

阻塞赋值方法:符号为=

阻塞与非阻塞赋值的区别:

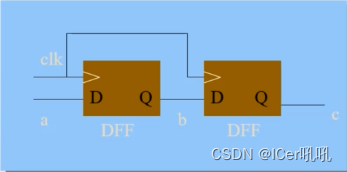

1.非阻塞赋值方式:

always @(posedge clk)

begin

b <= a;

c <= b;

end

非阻塞赋值在块结束时才完成赋值操作(c的值比b的值落后一个时钟周期)

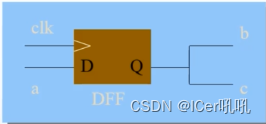

2.阻塞赋值方式

always @(posedge clk)

begin

b = a;

c = b;

end

阻塞赋值语句在该语句结束时就完成赋值操作(在块语句中,如果有多条阻塞赋值语句,在前面的赋值语句没有完成之前,后面的语句就不能被执行,就像被阻塞一样,因此称为阻塞赋值方式。这里的c和b的值一样。)

非阻塞赋值于阻塞赋值方式的主要区别:

非阻塞赋值:b的值被赋成新值a的操作,并不是立刻完成,而是在块结束时才完成;

块内的多条语句在块结束时同时赋值。

硬件有对应电路。

阻塞赋值: b的值立刻被赋成新值a;

完成该赋值语句后才能执行下一条语句;

硬件没有对应的电路,因而综合结果未知。

块语句

用来将两条或多条语句组合在一起,使其在格式上更像一条语句,以增加程序的可读性

块语句有两种:

begin...end语句——标示顺序执行的语句

fork...join语句——标示并行执行的语句(不可综合)

begin...end:

块内的语句是顺序执行的

每条语句的延迟时间是相对于前一条语句的仿真时间而言的

直到最后一条语句执行完,程序流程控制才能跳出该顺序块

块内语句可以是参数声明,reg变量声明,integer变量声明,real变量声明语句

#可以用在语句块中表示延迟,(在模块调用过程中使用#表示参数的传递)

fork...join:

块内的语句是并行执行的

每条语句的延迟时间是相对于开始仿真时间而言的

如何跳出该顺序块由(fork...join,fork...join_any,fork...join_none)决定

块内语句可以是参数声明,reg变量声明,integer变量声明,real变量声明语句,time变量声明语句和事件(event)说明语句。

条件语句

条件语句分为两种:if...else语句和case语句

它们都是顺序语句,应该放在“always”块内;

if...else:

判定给出的条件是否满足,根据判定的结果(真或假)决定执行给出的两种操作之一。

if...else语句有3中形式:

其中,表达式为逻辑表达式或关系表达式,或一位的变量

若表达的值为0或者z,则判定的结果为假,若为1,则加过为真

语句分为单句,也可分为多句;多句一定用“begin...end”语句括起来,形成一个符合块语句

方式1:

if (表达式) 语句1;

方式2:

if(表达式) 语句1;

else 语句2;

方式3:

if(表达式1) 语句1;

else if(表达式2) 语句2;

...

else if(表达式n) 语句n;

允许一定形式的表达式简写方式,如:

if(expression) 等同于if(expression ==1)

if(!expression) 等同于if(expression!=1)

if 语句可以嵌套

若if和else的数目不一样,要使用“begin..end”语句来确定if于else的配对关系。

嵌套语句:

if(表达式1)

if(表达式2)语句1;

else 语句2;

else

if(表达式3) 语句3;

else 语句4;

module count60(qout, cout,data,load,cin,reset,clk);

output[7:0] qout;

output cout;

input [7:0] data;

input load,cin,reset,clk;

reg [7:0] qout;

always@(posedge clk)

begin

if(reset) qout = 0; //同步复位

else if(load) qout = data; //同步置数

else if (cin) /如果cin为1,执行加1计数

begin

if (qout[3:0]==9)

begin

qout[3:0]=0;

if (qout[7:4]==5)

qout[7:4] = 0;

else

qout[7:4] =qout[7:4]+1;

end

else

qout[3:0]=qout[3:0]+1;

end

end

assign cout = ((qout ==8'h59)&cin)?1:0; //产生进位输出

endmodule

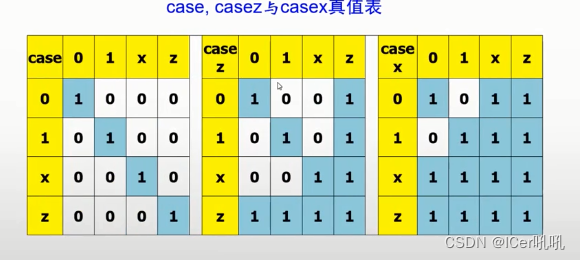

case语句

当敏感表达式取不同的值时,执行不同的语句;

功能:当某个(控制)信号取不同的值时,给另一个(输出)信号赋不同的值。常用于多条件译码电路(如译码器,数据选择器,状态机,微处理器)

case语句有三种不同形式:case,casez,casex

说明:

其中“敏感表达式”有称为“控制表达式”,通常表示为控制信号的某些位。

值1—值n称为分支表达式,用控制信号的具体状态值表示,因此有分为常量表达式。

default项可有可无,一个case语句中只有一个default项;

值1—值n必须互不相同,否则矛盾;

值1—值n的位宽必须相等,且与控制表达式的位宽相同。

casez与casex语句:

使用条件语句的注意事项:

- 应列出所有条件分支,否则当条件不满足时,编译器会生成一个锁存器保持原值;

- 这一点可用于设计时序电路,如计数器:条件满足时加1,否则保持原值不变;

- 在组合电路设计中,应避免生成隐含的锁存器,有效的方法是在if语句最后写上else,在case语句最后写上default项。

审核编辑:汤梓红

-

assign语句和always语句的用法2024-02-22 5110

-

考虑x和z在verilog条件语句中的使用情况2023-11-02 3246

-

Python中什么是语句块2023-09-12 1807

-

C语言中if语句、if-else语句和switch语句详解2023-08-18 13598

-

条件语句/循环语句simulink的实现方法(一)2023-07-21 15738

-

Verilog常用的循环语句及用途2023-05-12 4162

-

Verilog中的If语句和case语句介绍2023-05-11 7556

-

详解Python条件语句2023-04-19 1535

-

条件判断语句(if语句)2023-02-21 5056

-

Verilog的块语句fork...join 和 begin...end2022-06-09 4205

-

Verilog的块语句2022-05-18 1992

-

简述Verilog HDL中阻塞语句和非阻塞语句的区别2021-12-02 7621

-

Verilog的两种块语句解析2021-06-18 3674

-

Verilog中的赋值语句的区别2020-11-26 4417

全部0条评论

快来发表一下你的评论吧 !