《先进半导体封装材料及工艺-2023版》

描述

为什么需要先进半导体封装?

据麦姆斯咨询介绍,人类正生活在一个以数据为中心的时代。各行各业产生的数据量不断攀升,持续推动对高带宽计算的需求增长。机器学习和人工智能(AI)等应用需要强大的处理能力,因此需要在芯片上更密集地布置晶体管,在封装中需要更紧凑地互连凸点间距。后者强调了半导体封装技术在满足上述需求时的重要性。在此背景下,英国知名研究公司IDTechEx发布了这份关于先进半导体封装材料及工艺的最新研究。

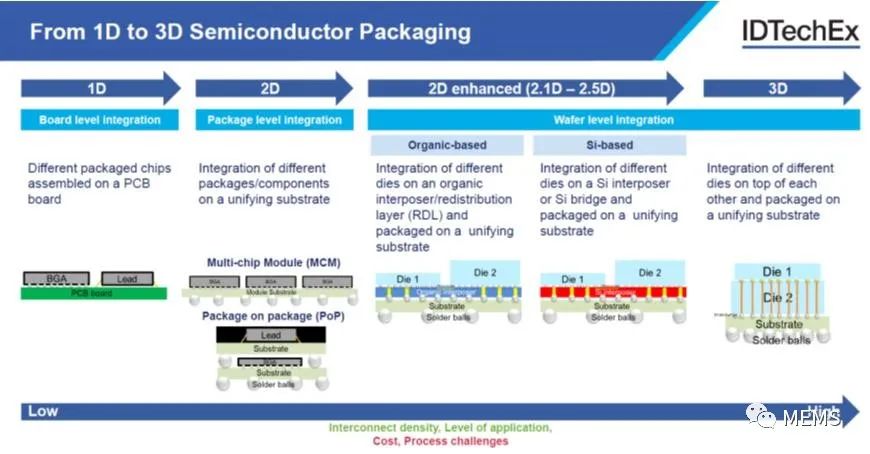

1D到3D半导体封装

半导体封装已经从板级集成发展到晶圆级集成,带来了显著的进步。晶圆级集成提供了优于传统方案的诸多优势,例如:提高了互连密度,为尺寸敏感应用提供了更小的占位面积,同时还增强了性能。

目前,包括2.5D IC、3D IC和高密度扇出晶圆级封装等封装技术,被归类为“先进半导体封装”,其特点是凸点间距低于100 µm,能够实现至少10倍的更高互连密度以及更高的集成能力。

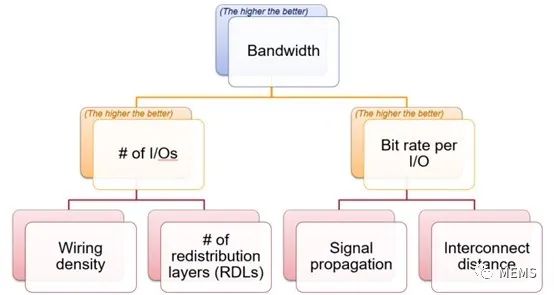

带宽是关键

从封装的角度来看,要提高带宽,需要考虑两个关键因素:I/O(输入/输出)总数和每个I/O的比特率。增加I/O总数需要在每个布线层/再分布层(RDL)中实现更精细的线宽/间距(L/S),并具有更高数量的布线层。另一方面,提高每I/O比特率受到芯粒(chiplets)之间互连距离和介质材料选择的影响。这些因素直接影响着封装系统的整体性能和效率。

影响封装模块带宽的关键因素

释放高带宽:探索先进半导体封装的材料和工艺

从材料和工艺角度深入研究如何实现更高的布线密度和每I/O比特率,揭示了介质材料选择和适当工艺技术所发挥的关键作用。这些因素对封装系统的整体性能和功能具有重大影响。

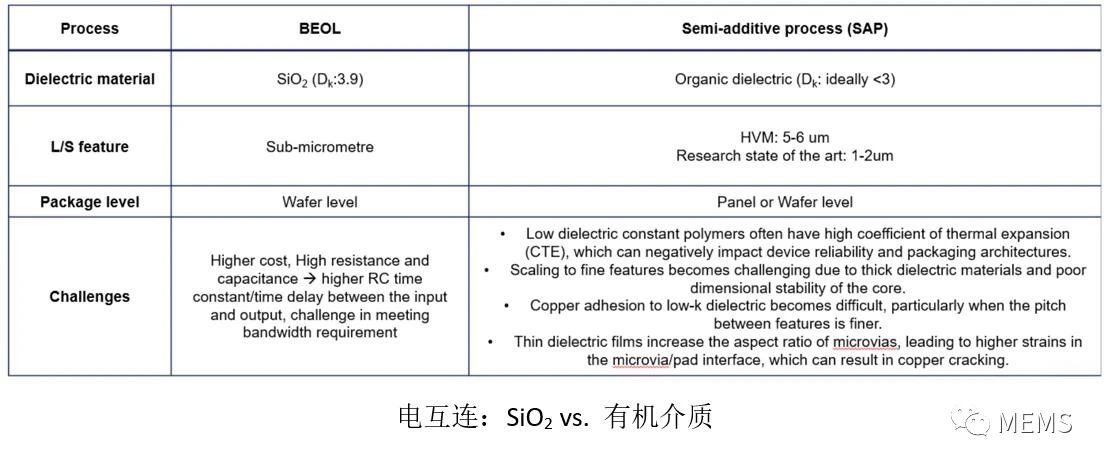

电互连:SiO2 vs. 有机介质

选择合适的介质材料至关重要,需要考量低介电常数、最佳CTE(尽可能接近Cu的CTE)等特性,以及确保模块可靠性的有利机械特性(例如杨氏模量和延伸率等)。这些选择可以实现更高的数据速率,同时保持信号完整性,并有助于更精细的线宽/间距以提高布线密度。

在GPU等高性能加速器中,SiO2等无机介质已被广泛用于实现超精细线宽/间距。然而,由于它们的高RC延迟,在需要高速连接的应用中受到限制。作为一种替代方案,有机介质因其成本效益,以及通过低介电常数减轻RC延迟而获得关注。不过,有机介质仍存在挑战,包括可能对器件可靠性带来负面影响的高CTE,以及线宽/间距难以扩展等。

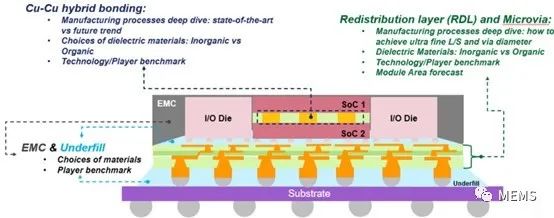

除了选择合适的材料,封装制造过程中采用的工艺技术在实现更高数量I/O以及提高I/O比特率方面也发挥着至关重要的作用。2.5D封装工艺中涉及的步骤(光刻、CMP、蚀刻工艺等),以及3D Cu-Cu混合键合中的CMP和键合工艺,在实现更紧密布线和增加布线密度等方面提出了挑战。IDTechEx在这份报告中提供了有关材料选择如何影响制造工艺的详细见解,帮助用户全面了解它们对先进半导体封装的影响。

本报告覆盖了哪些材料和技术?

报告研究覆盖的案例

本报告主要可分为四个部分,提供了理解先进半导体封装材料和工艺的结构化方法。报告第一部分全面介绍了先进半导体封装的技术、发展趋势、关键应用和生态系统,为用户提供了坚实的概述知识。

第二部分重点介绍了2.5D封装工艺,深入研究了RDL和微孔介质材料、RDL制造技术以及EMC和MUF材料选择等关键技术。本部分中的每个小章节都详细分析了工艺流程、技术对标、厂商评估以及未来趋势,为用户提供了全面的见解。

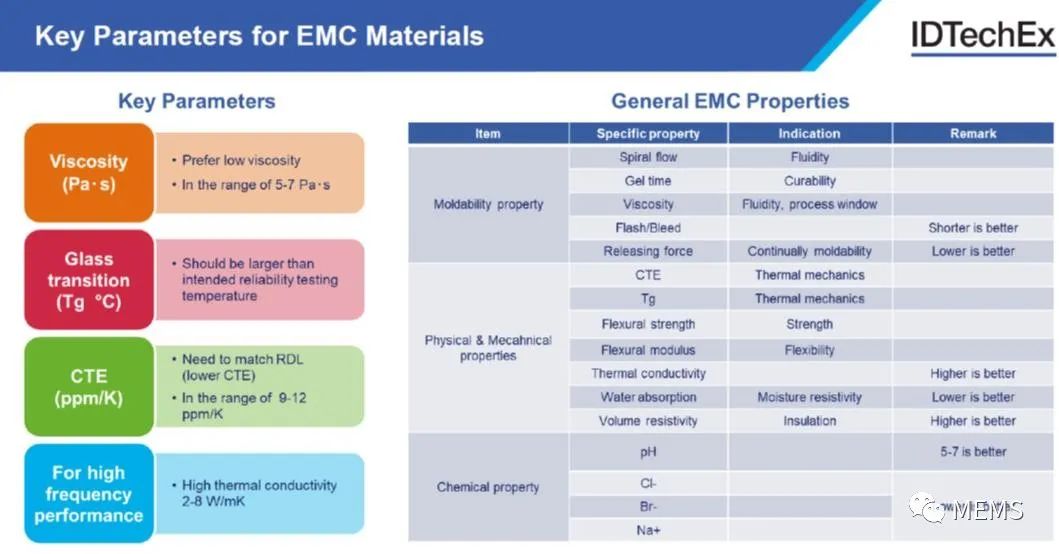

EMC材料关键考量参数

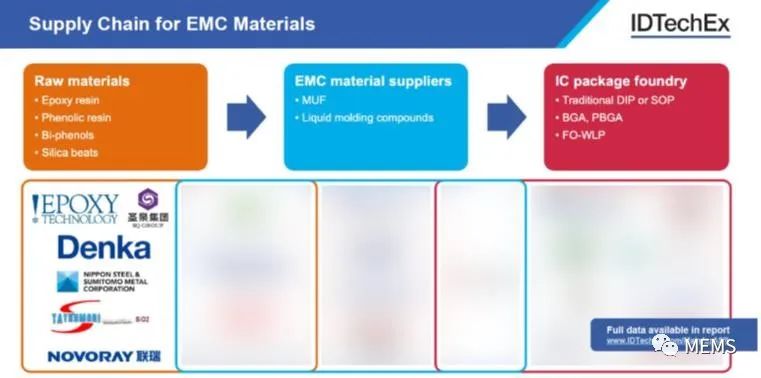

EMC材料供应链(样刊模糊化)

关于2.5D封装的讨论继续到第三部分,重点聚焦了用于3D芯片堆叠的创新Cu-Cu混合键合技术。本章节提供了对制造工艺的深入研究,并为实现最佳结果提供了材料选择指南。报告还展示了很多案例研究,重点介绍了使用有机和无机介质成功实现Cu-Cu混合键合的案例。

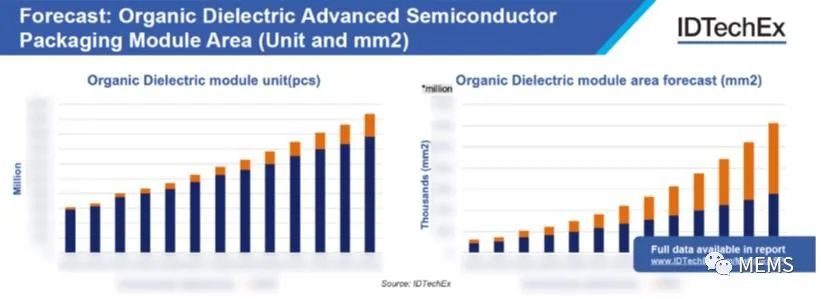

有机介质先进半导体封装模块10年期市场预测

此外,本报告在最后一部分提供了有机介质先进半导体封装模块的10年期市场预测,对未来预期的市场增长和趋势提供了重要展望。

-

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测2025-04-15 1793

-

#工作原理大揭秘 #半导体 #半导体材料 半导体材料及应用领域~MDD辰达行半导体 2023-03-09

-

有关半导体工艺的问题2009-09-16 5853

-

半导体工艺讲座2009-11-18 97513

-

半导体材料的特性与参数2013-01-28 9258

-

适合用于射频、微波等高频电路的半导体材料及工艺情况介绍2019-06-27 6208

-

SiC半导体材料及其器件应用2011-11-01 1410

-

主流射频半导体材料及特性介绍2017-11-24 3546

-

主流射频半导体材料及特性介绍2017-12-07 2828

-

盘点半导体制造工艺中的主要设备及材料2018-10-13 6053

-

简析适用于射频微波等高频电路的半导体材料及工艺2020-10-30 1902

-

高频电路的半导体材料及工艺详细资料说明2020-12-30 1385

-

先进封装技术之设计·材料·工艺新发展2023-09-08 1136

-

半导体行业将从设备时代过渡到材料时代2023-12-28 1356

-

主要先进封装厂商汇总名单半导体材料与工艺设备2024-01-30 1861

全部0条评论

快来发表一下你的评论吧 !