常用的数模混合PLL的两种经典结构

电子说

描述

经典锁相环结构小结

频率合成器一般分为直接合成模拟式频率合成器、锁相环频率合成器、直接数字频率合成器(DDS)。其中锁相环频率合成器按照实现技术分为模拟PLL、数字PLL(ADPLL)、数模混合PLL。

这篇文章中主要讲的就是比较常用的数模混合PLL(以下简称PLL)的两种经典结构。

主要构成

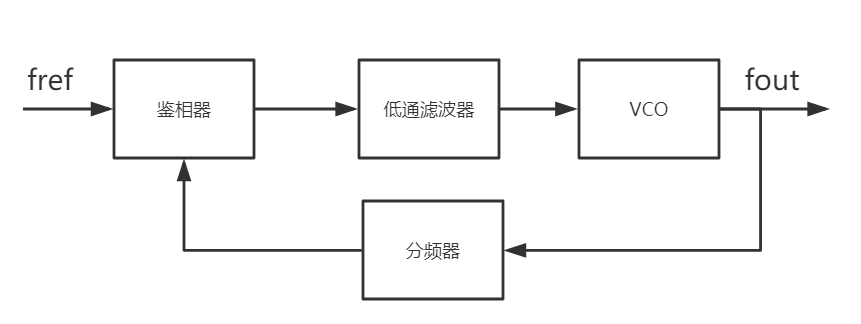

PLL一般由PD(PFD)、LPF、VCO、分频器等组成。

核心器件之鉴相器

模拟鉴相器就是一个乘法器,通常由Gilbert乘法器单元构成,由于当两信号相位差为 时,鉴相器的增益最大,又称为正交型鉴频器,同时环路的相位误差

时,鉴相器的增益最大,又称为正交型鉴频器,同时环路的相位误差 等于两信号的相位差减去

等于两信号的相位差减去 。当某一个输出信号为方波或者由于输入信号幅度很大类似方波时,需要对VCO的频率范围进行限制,防止环路锁定到高阶谐波频率上,鉴相范围为

。当某一个输出信号为方波或者由于输入信号幅度很大类似方波时,需要对VCO的频率范围进行限制,防止环路锁定到高阶谐波频率上,鉴相范围为 。

。

数字鉴相器主要为异或型鉴相器、时序型鉴相器、以及可鉴频又可鉴相的鉴频鉴相器PFD。

- 异或型鉴相器由数字异或门构成,稳定状态类似模拟鉴相器,相位差为

时,鉴相器经过低通滤波器的输出为0,环路相位误差

时,鉴相器经过低通滤波器的输出为0,环路相位误差 为0。也要注意锁定到高阶谐波频率上,鉴相范围为

为0。也要注意锁定到高阶谐波频率上,鉴相范围为 。

。 - 时序型鉴相器可由JK触发器构成,一般鉴相范围为2

,环路锁定时两信号的相位差为0,稳定平衡点和不稳定平衡点的鉴相器增益差距较大,与异或型鉴相器相比,锁定时间减小,但因为是边沿触发,需要保证J、K两端的边沿响应速度相同。

,环路锁定时两信号的相位差为0,稳定平衡点和不稳定平衡点的鉴相器增益差距较大,与异或型鉴相器相比,锁定时间减小,但因为是边沿触发,需要保证J、K两端的边沿响应速度相同。 - 鉴频鉴相器可以理解为在鉴相器的基础上加一个鉴频器,目的是在两信号频率差较大时,能够锁定,且减小锁定时间,同时由于有鉴频器的反馈作用,对于鉴频鉴相器来说没有捕获范围的限制,鉴相范围为4

。

。

经典结构之I型锁相环

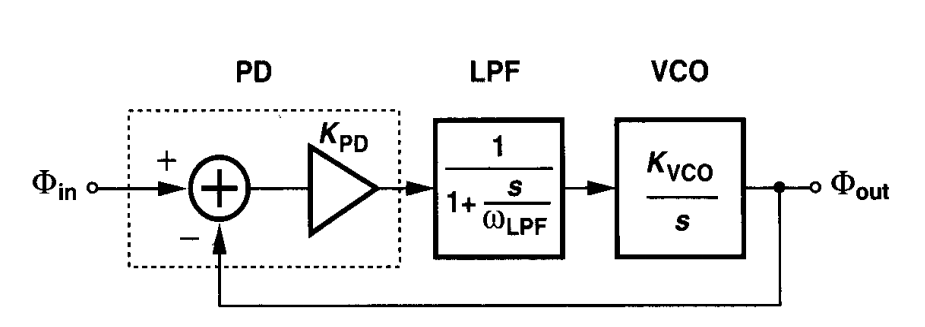

下图所示的PLL是一个二阶I型锁相环。“二阶”是因为低通滤波器为一阶,Ⅰ型是因为环路增益在原点处有一个极点。

锁定过程

两输入之间相位不同时,鉴频器会输出与相位差正比的宽脉冲,经过低通滤波器后,变为控制VCO振荡频率的控制信号,改变振荡器的频率,再反馈与鉴相器,在各个参数合适的情况下,最终使得输出相位差减小为一稳态值,两输入信号的频率相等。

主要问题

I型锁相环需要在阻尼系数,低通滤波器带宽与相位误差之间进行折衷,或者说系统锁定时间、系统稳定度、相位误差、控制电压的纹波之间需要折衷,而且这种类型的锁相环只有 和

和 的差值比

的差值比 略小时才能锁定。

略小时才能锁定。

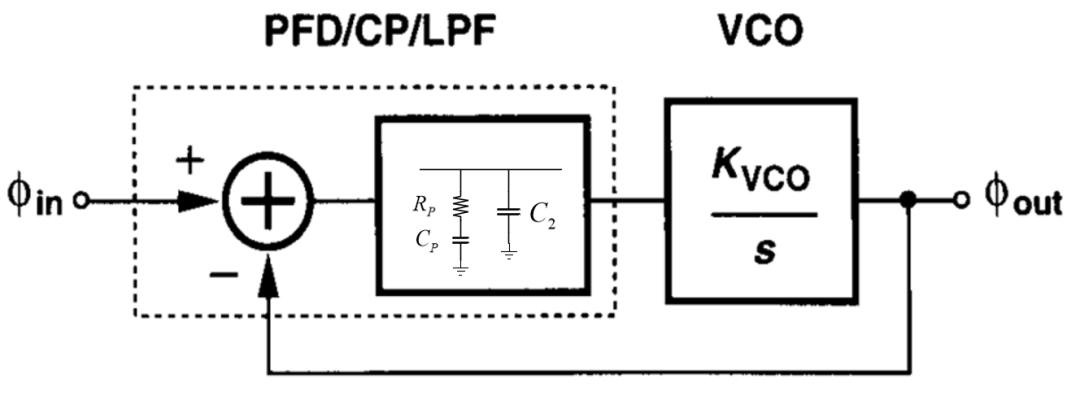

经典结构之II型锁相环

上图所示为三阶II型锁相环,由于鉴相器改为鉴频鉴相器,又可称为电荷泵锁相环(CPPLL)。同理,“三阶”是因为低通滤波器为二阶,II型是因为环路增益在原点处有两个极点。

锁定过程

两输入之间相位不同时,鉴频鉴相器、电荷泵和低通滤波器会产生和相位差、频率差,正比的控制信号,改变VCO振荡频率,再反馈回去,在各个参数合适的情况下,由于鉴频鉴相器中鉴频作用,使得锁定时间减小且捕获范围增大,同时又因为电荷泵直流增益较大,使得锁定时,相位差趋于0,两输入频率也相等。

与I型锁相环的差异点

- 环路增益在原点处有两极点,容易导致系统的不稳定,低通滤波器设计需要更加注意

- 环路的直流增益较大,相位差趋于0,且相位和频率不会有太大的漂移;

- PFD/CP/LPF在原点有一极点,而I型锁相环的PD/LPF没有。

主要问题

- 鉴频鉴相器有死区,需要额外电路的设计处理;

- 电荷泵不够理想,带来杂散;比如电荷泵的上脉冲和下脉冲延迟时间不一样、电流源和电流沉不一样,开关管的时间馈通和电荷注入不匹配等。

-

VCXO和TCXO:两种常用的晶体振荡器,你了解它们的原理和应用吗?2023-12-06 3435

-

射频与数模混合类高速PCB设计2023-09-27 962

-

详解PMSM中常用的两种坐标变换2023-01-19 4365

-

ATK-HS-ADDA模块常用的两种芯片?2021-09-27 1245

-

智能插座常用的两种通信协议是什么?2021-09-26 1581

-

介绍两种常用的微型水泵2021-09-10 2886

-

两种典型的ADRC算法介绍2021-09-07 3601

-

两种不同结构的永磁同步电机特点说明2021-06-28 2351

-

常用的hdl语言有哪两种2020-08-25 9994

-

单片机常用的两种延时控制方式2020-07-17 6794

-

Wincc如何与PLC进行通讯两种常用的方式介绍2019-02-17 31896

-

贴片机常用的两种直线驱动结构2018-09-03 1965

-

介绍两种电机机械过载保护的结构2017-01-01 927

-

两种新型一维微带开口环PBG结构2010-08-02 655

全部0条评论

快来发表一下你的评论吧 !