碳化硅介绍:三种SiC衬底制作方法对比

模拟技术

描述

碳化硅概况

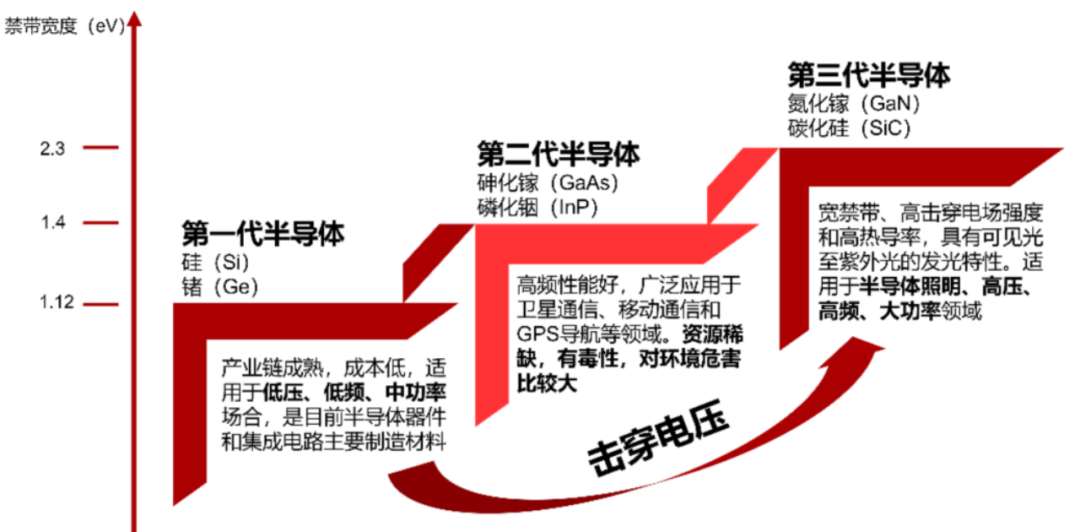

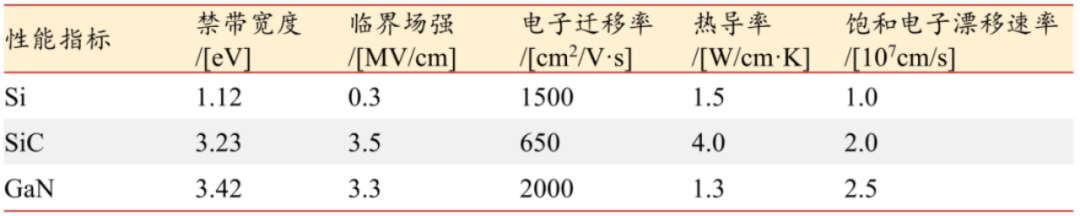

碳化硅(SiC)是由碳元素和硅元素组成的一种化合物半导体材料,是制作高温、高频、大功率、高压器件的理想材料之一。相比传统的硅材料(Si),碳化硅的禁带宽度是硅的3倍;导热率为硅的4-5倍;击穿电压为硅的8-10倍;电子饱和漂移速率为硅的2-3倍,满足了现代工业对高功率、高电压、高频率的需求,主要被用于制作高速、高频、大功率及发光电子元器件,下游应用领域包括智能电网、新能源汽车、光伏风电、5G通信等,在功率器件领域,碳化硅二极管、MOSFET已经开始商业化应用。

图表 1:半导体材料发展路径

耐高温。碳化硅的禁带宽度是硅的2-3倍,在高温下电子不易发生跃迁,可耐受更高的工作温度,且碳化硅的热导率是硅的4-5倍,使得器件散热更容易,极限工作温度更高。耐高温特性可以显著提升功率密度,同时降低对散热系统的要求,使终端更加轻量和小型化。

耐高压。碳化硅的击穿电场强度是硅的10倍,能够耐受更高的电压,更适用于高电压器件。

耐高频。碳化硅具有2倍于硅的饱和电子漂移速率,导致其器件在关断过程中不存在电流拖尾现象,能有效提高器件的开关频率,实现器件小型化。

低能量损耗。碳化硅相较于硅材料具有极低的导通电阻,导通损耗低;同时,碳化硅的高禁带宽度大幅减少泄漏电流,功率损耗降低;此外,碳化硅器件在关断过程中不存在电流拖尾现象,开关损耗低。

图表2:不同半导体材料性能对比

图表3:GaN、SiC与Si性能对比雷达图

碳化硅产业链主要包括衬底、外延、器件设计、制造、封测等环节。碳化硅从材料到半导体功率器件会经历单晶生长、晶锭切片、外延生长、晶圆设计、制造、封装等工艺流程。在合成碳化硅粉后,先制作碳化硅晶锭,然后经过切片、打磨、抛光得到碳化硅衬底,经外延生长得到外延片。外延片经过光刻、刻蚀、离子注入、金属钝化等工艺得到碳化硅晶圆,将晶圆切割成die,经过封装得到器件,器件组合在一起放入特殊外壳中组装成模组。

产业链上游1:衬底—晶体生长为最核心工艺环节碳化硅衬底约占碳化硅器件成本的47%,制造技术壁垒最高、价值量最大,是未来SiC大规模产业化推进的核心。从电化学性质差异来看,碳化硅衬底材料可以分为导电型衬底(电阻率区15~30mΩ·cm)和半绝缘型衬底(电阻率高于105Ω·cm)。这两类衬底经外延生长后分别用于制造功率器件、射频器件等分立器件。其中,半绝缘型碳化硅衬底主要应用于制造氮化镓射频器件、光电器件等。通过在半绝缘型碳化硅衬底上生长氮化镓外延层,制得碳化硅基氮化镓外延片,可进一步制成HEMT等氮化镓射频器件。导电型碳化硅衬底主要应用于制造功率器件。与传统硅功率器件制作工艺不同,碳化硅功率器件不能直接制作在碳化硅衬底上,需在导电型衬底上生长碳化硅外延层得到碳化硅外延片,并在外延层上制造肖特基二极管、MOSFET、IGBT等功率器件。

图表4:半绝缘型和导电型碳化硅衬底的对比

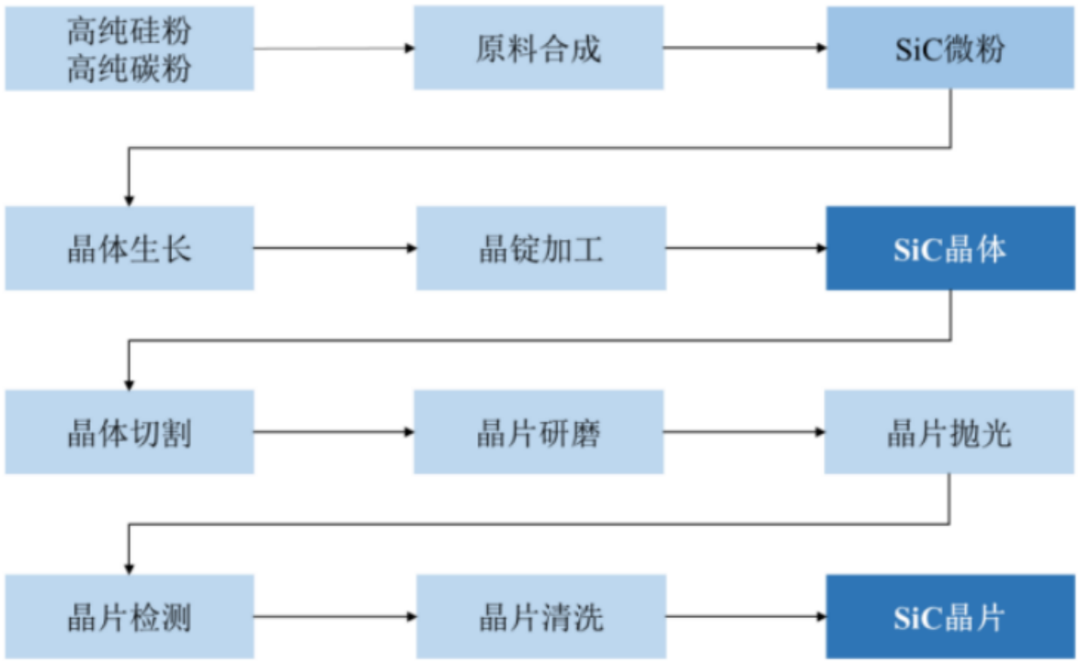

以高纯碳粉、高纯硅粉为原料合成碳化硅粉,在特殊温场下生长不同尺寸的碳化硅晶锭,再经过多道加工工序产出碳化硅衬底。核心工艺流程包括:

原料合成:将高纯的硅粉+碳粉按配方混合,在2000°C以上的高温条件下于反应腔室内进行反应,合成特定晶型和颗粒度的碳化硅颗粒。再通过破碎、筛分、清洗等工序,得到满足要求的高纯碳化硅粉原料。

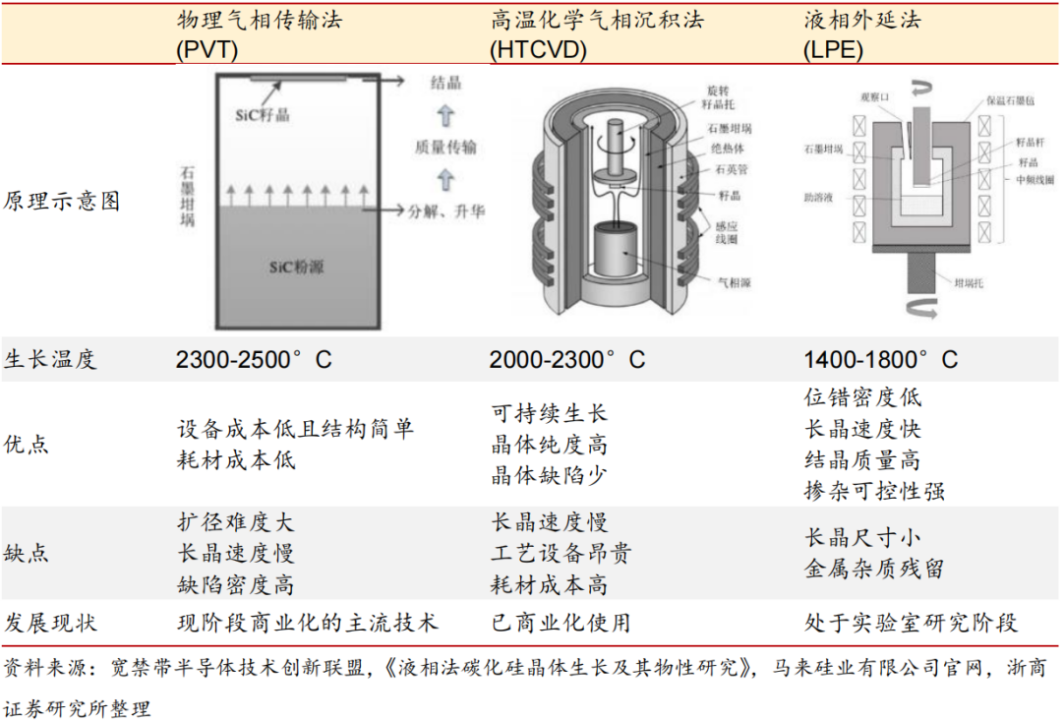

晶体生长:为碳化硅衬底制造最核心工艺环节,决定了碳化硅衬底的电学性质。目前晶体生长的主要方法有物理气相传输法(PVT)、高温化学气相沉积法(HT-CVD)和液相外延(LPE)三种方法。其中PVT法是现阶段商业化生长SiC衬底的主流方法,技术成熟度最高、工程化应用最广。

图表5:三种SiC衬底制作方法对比

晶体加工:通过晶锭加工、晶棒切割、研磨、抛光、清洗等环节,将碳化硅晶棒加工成衬底。

图表6:SiC衬底工艺流程

SiC衬底制备难度大,导致其价格居高不下

温场控制困难:Si晶棒生长只需 1500℃,而 SiC 晶棒需要在 2000℃以上高温下进行生长,并且 SiC 同质异构体有 250 多种,但用于制作功率器件的主要是 4H-SiC 单晶结构,如果不做精确控制,将会得到其他晶体结构。此外,坩埚内的温度梯度决定了 SiC 升华传输的速率、以及气态原子在晶体界面上排列生长方式,进而影响晶体生长速度和结晶质量,因此需要形成系统性的温场控制技术。与 Si 材料相比,SiC 生产的差别还在如高温离子注入、高温氧化、高温激活等高温工艺上,以及这些高温工艺所需求的硬掩模工艺等。

晶体生长缓慢:Si晶棒生长速度可达 30~150mm/h,生产 1-3m 的硅晶棒仅需约 1 天的时间;而 SiC 晶棒以 PVT 法为例,生长速度约为 0.2-0.4mm/h,7 天才能生长不到 3-6cm,长晶速度不到硅材料的百分之一,产能极为受限。

良品参数要求高、良率低:SiC衬底的核心参数包括微管密度、位错密度、电阻率、翘曲度、表面粗糙度等,在密闭高温腔体内进行原子有序排列并完成晶体生长,同时控制参数指标,是复杂的系统工程。

材料硬度大、脆性高,切割耗时长、磨损高:SiC莫氏硬度达 9.25 仅次于金刚石,这导致其切割、研磨、抛光的加工难度显著增加,将一个 3cm 厚的晶锭切割 35-40 片大致需要花费 120 小时。另外,由于 SiC 脆性高,晶片加工磨损也会更多,产出比只有 60%左右。

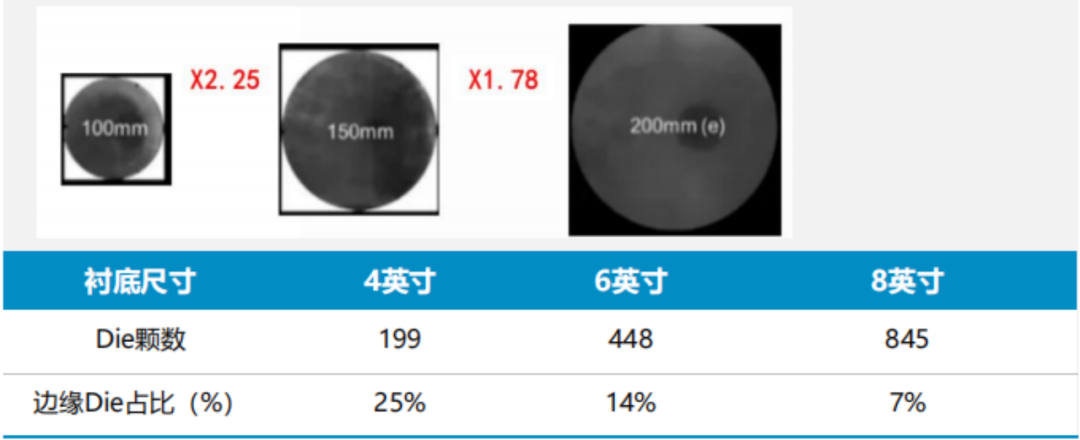

发展趋势:尺寸增加+价格下降全球SiC市场6英寸量产线正走向成熟,领先公司已进军8英寸市场。国内正在开发项目以6英寸为主。目前虽然国内大部分公司还是以4寸产线为主,但是产业逐步向6英寸扩展,随着6英寸配套设备技术成熟后,国产SiC衬底技术也在逐步提升大尺寸产线的规模经济将会体现,目前国内6英寸的量产时间差距缩小至7年。更大的晶圆尺寸可以带来单片芯片数量的提升、提高产出率,以及降低边缘芯片的比例,研发和良率损失部分成本也将保持在7%左右,从而提升晶圆利用率。

图表7:4-6-8英寸的芯片数量变化

衬底直径及大直径衬底占比将不断增加,助力全产业链降本。预计未来30年,大尺寸衬底的比例将不断增加,在大部分衬底提供商具备新型大尺寸量产能力,一轮尺寸更新周期迭代完成后,衬底单位面积价格会迎来相对快速的降低。

SiC衬底价格会随着尺寸增加有所下降,同时进一步带来销量的稳步上升。目前衬底发展最重要的方向趋势是扩大直径,这会降低衬底生产成本进而降低售价,价格的下降也会加速SiC衬底在各领域内的渗透。根据CASA数据预测,SiC衬底和外延随着产业技术逐步成熟(良率提升)和产能扩张(供给提升),预计衬底价格将以每年8%的速度下降。

编辑:黄飞

-

什么是MOSFET栅极氧化层?如何测试SiC碳化硅MOSFET的栅氧可靠性?2025-01-04 2617

-

SIC碳化硅二极管2016-11-04 5604

-

碳化硅(SiC)肖特基二极管的特点2019-01-11 8321

-

碳化硅的历史与应用介绍2019-07-02 5055

-

碳化硅深层的特性2019-07-04 6094

-

碳化硅二极管选型表2019-10-24 1907

-

碳化硅基板——三代半导体的领军者2021-01-12 4437

-

什么是碳化硅(SiC)?它有哪些用途?2021-06-18 9405

-

传统的硅组件、碳化硅(Sic)和氮化镓(GaN)2021-09-23 6167

-

请教碳化硅刻蚀工艺2022-08-31 42012

-

功率模块中的完整碳化硅性能怎么样?2023-02-20 9408

-

归纳碳化硅功率器件封装的关键技术2023-02-22 2952

-

碳化硅SiC技术导入应用的最大痛点2023-02-27 1883

-

三种碳化硅外延生长炉的差异2023-12-15 5516

-

碳化硅衬底 TTV 厚度测量方法的优劣势对比评测2025-08-09 1297

全部0条评论

快来发表一下你的评论吧 !