RAL寄存器模型操作指南

电子说

描述

寄存器模型操作,指的是通过寄存器模型对RTL中寄存器进行读写访问,或者同步寄存器模型与RTL中寄存器的值。对寄存器模型的操作,可以通过调用模型提供的方法来实现。这些方法的调用,建立在已经完成寄存器模型的构建和集成到验证环境的基础上。

本文将展开介绍寄存器模型访问上的一些内容,包括寄存器域段的成员值、寄存器的前后门访问以及具体各种访问方法图示。

01 寄存器域段

按照前文介绍UVM寄存器模型基础时的描述,寄存器域段(uvm_reg_field)是构造寄存器模型最小的功能单元。这也就意味着,寄存器的值,是由多个域段的值拼接起来的。那么,在介绍寄存器的访问方法之前,有必要先看看寄存器的域段都是怎么存放值的。

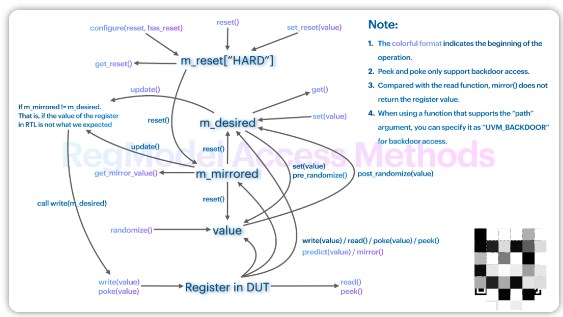

从uvm_reg_field类型定义的源码可以看到,跟域值相关的成员变量有这么几个:value, m_mirrored, m_desired, m_reset[“HARD”]。它们的数据类型均为uvm_reg_data_t,其实也就是UVM对bit unsigned [`UVM_REG_DATA_WIDTH-1:0]的类型重命名。

尽管除value以外其他三个成员都是local可见的,但是知道这些local成员的存在和意义,对理解和使用后面要介绍的操作方法会有很大的帮助。

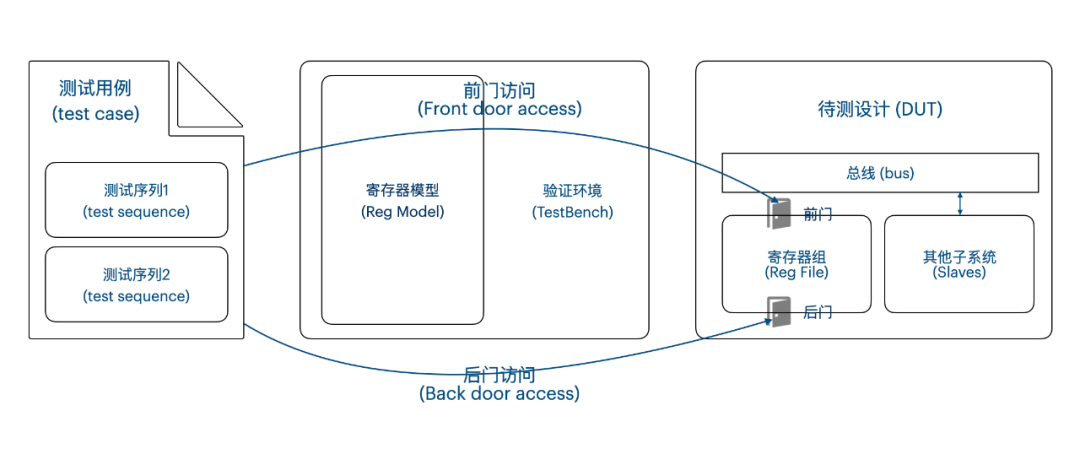

02 前后门访问

寄存器的前门访问(front door access),指的是Testbench所发出的寄存器操作,都会被转换成总线事务,并实际驱动到DUT的总线上,会占用总线和消耗总线周期。换句话说,这种寄存器访问方式跟其他硬件组件访问寄存器一样,是从”明面“上对寄存器进行访问。

寄存器的后门访问(back door access),指的是用户通过仿真器,对DUT中指定路径的寄存器信号进行改写或读取。这种寄存器访问方式不需要消耗仿真时间,毕竟”走后门“总是要比走前门要方便快捷很多。后门访问的前提是,在建立寄存器模型的时候,指定了对应寄存器在DUT中的路径(HDL_path)。

后门访问带来的坏处是,这种直接改写和读取寄存器的操作不会被反映成总线行为,也就无法覆盖到寄存器访问涉及到的总线系统,以及总线上其他相关的逻辑模块。举个栗子,后门访问可以掩盖掉总线系统上本来存在着的地址译码错误。总结起来:除一些特殊的测试场景,寄存器的访问少走后门,多走前门。

下一小节介绍寄存器模型操作方法的同时,也会提到哪些是对寄存器的前门访问,哪些是后门访问。

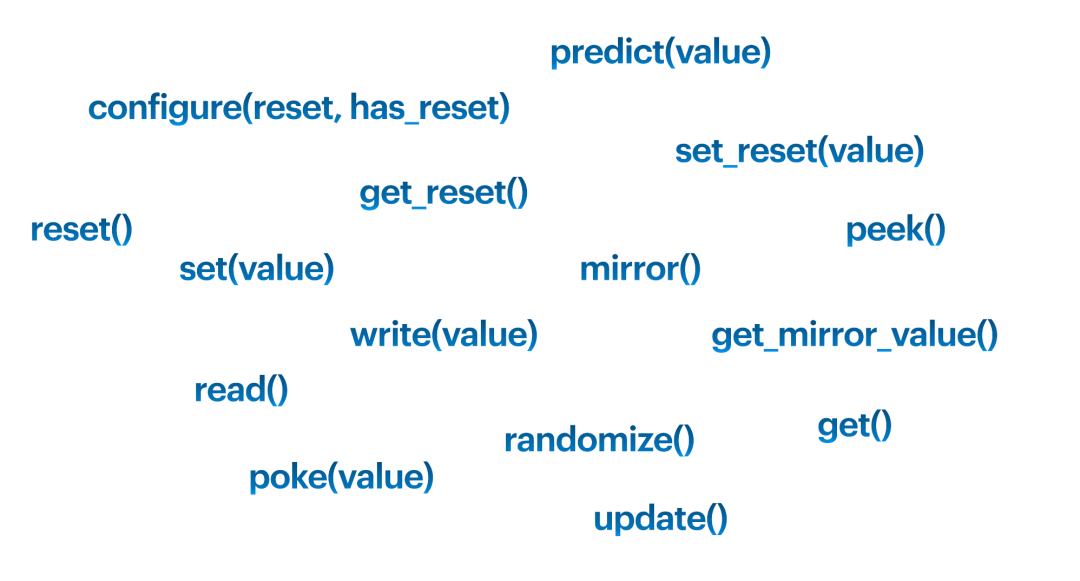

03 寄存器模型方法

寄存器模型方法有很多,大致如下图所示。由于方法较多,本文就不再列出这些方法的原型,有需要的读者完全可以通过UVM提供的类型手册找到非常详细的函数原型和说明。

对寄存器的访问方法,无非是对DUT中寄存器,或者是对寄存器模型中各个成员值的改写或读取。因此,可以整理出每种方法对这些值的影响(见下图),然后总结出来常用场景下的操作组合。下图中彩色渐变格式表示操作的开始。

在大多数的应用场景,对寄存器的访问完全可以通过write(value) & read()这样的组合来完成,也可以选用set(value)先修改期望值,然后在通过update()函数去做同步。这样的好处是,如果RTL寄存器的值已经是我们的期望值,那么就不会也没有必要再浪费总线资源去重新配置一遍。

审核编辑:刘清

-

UVM寄存器模型的常规方法有哪些呢?2023-11-25 4359

-

如何在shell中操作寄存器2023-09-26 2216

-

寄存器是什么?怎么操作寄存器点亮LED灯?2023-07-21 5537

-

寄存器模型Register Model学习笔记2023-07-11 5649

-

简化UVM寄存器模型的使用2023-05-29 2734

-

RAL寄存器模型操作图鉴2023-05-17 2235

-

VersaClock 6 系列寄存器描述和编程指南2023-03-15 411

-

简述RAL寄存器模型基础2023-02-14 3863

-

简化UVM寄存器模型的使用教程2023-01-30 3669

-

如何构建UVM寄存器模型并将寄存器模型集成到验证环境中2022-09-23 3550

-

C语言:寄存器操作2022-01-13 744

-

寄存器变量2019-06-03 3037

-

寄存器操作方法_对寄存器操作的通用方法总结2018-05-22 24863

全部0条评论

快来发表一下你的评论吧 !