三相桥式全控整流电路仿真设计

电子说

描述

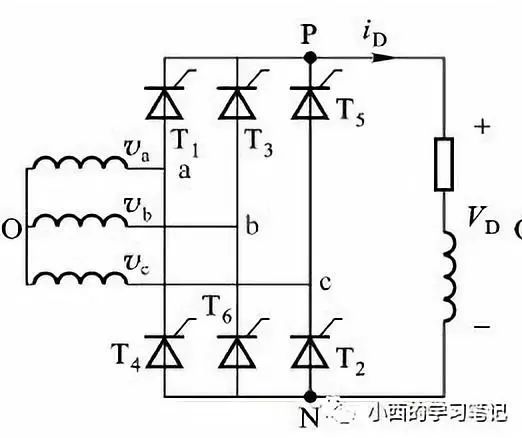

理论知识:

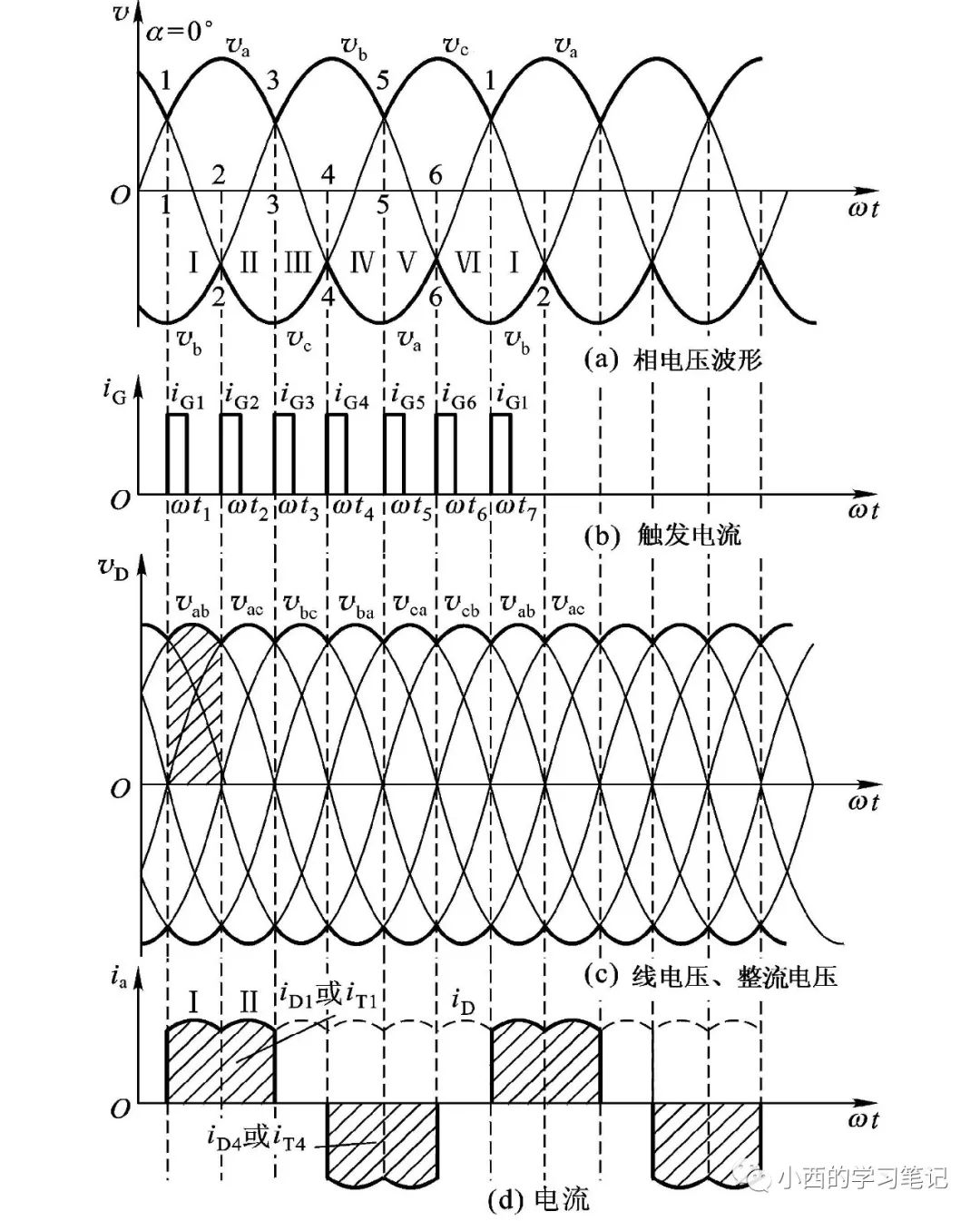

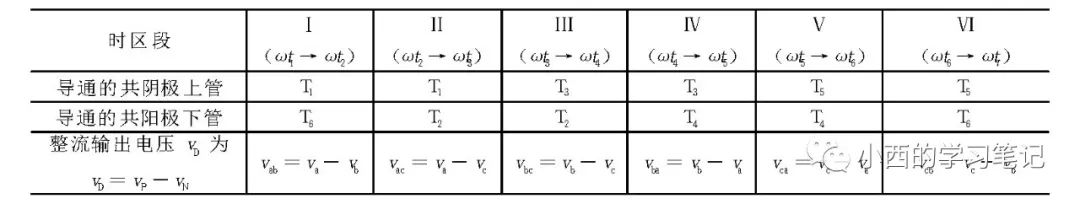

电路带电阻负载,α=0°时的波形

(1) 每个时刻均需要两个晶闸管同时导通,形成向负载供电的回路,其中一个晶闸管是共阴极组的,一个是共阳极组的,且不能为同一组的晶闸管。

(2) 对触发脉冲的要求:六个晶闸管的脉冲按 VT1-VT2-VT3-VT4-VT5-VT6的顺序,相位依次相差60° ;共阴极组VT1、VT3、VT5的脉冲依次相差120°,共阳极组的VT4、VT6、VT2也依次差120°;同一相的上下两个桥臂,即VT1与VT4,VT3与VT6,VT5与VT2,脉冲相差180°。

(3) 整流输出电压Ud一周期脉动六次,每次脉动的波形都一样,故该电路为六脉波整流电路。

(4) 在整流电路合闸启动中或电流断续时,为了确保电路的正常工作,需保证同时导通的两个晶闸管均有脉冲。为此,可采用两种办法:一种是使触发脉冲宽度大于60°(一般是80°~100°),称为 宽脉冲触发 ;另一种方式是在触发某个晶闸管的同时,给前一个晶闸管补发脉冲,即用两个窄脉冲代替宽脉冲,两个窄脉冲的前沿相差60°,脉宽一般为20°~30°,称为 双脉冲触发 。

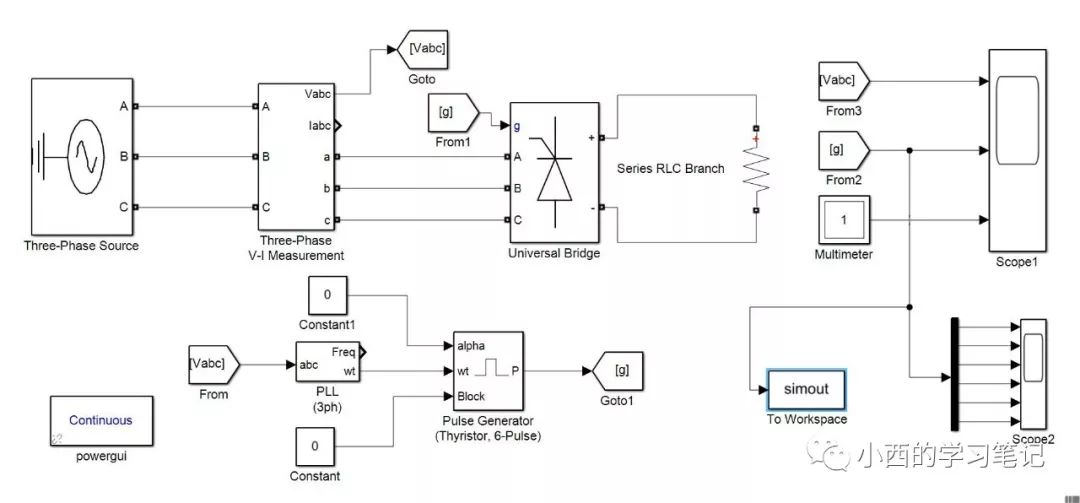

** 三相全控桥式电路模型的建立与仿真**

1.触发脉冲的得到:

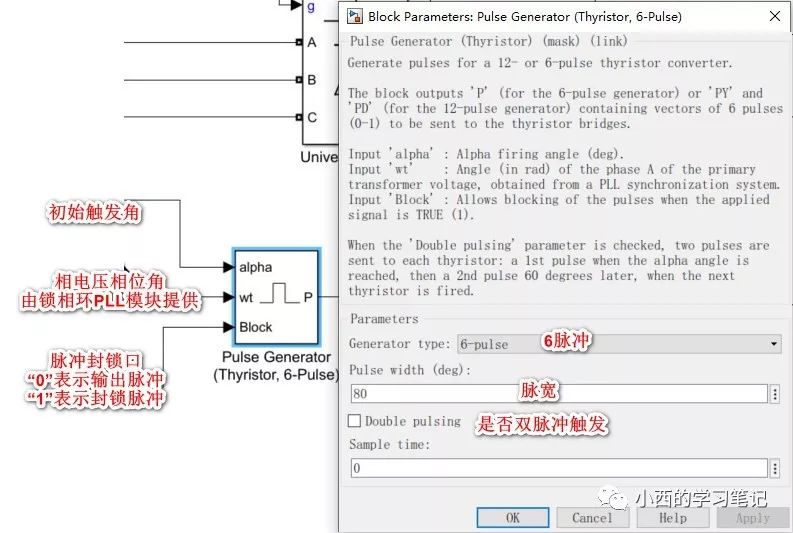

三相桥式全控整流电路每个晶闸管的脉冲需要按照VT1-VT2-VT3-VT4-VT5-VT6的顺序,相位依次相差60°。我们使用”Pluse Generator”

来得到晶闸管触发6脉冲。

我们选择宽触发6脉冲,脉宽选80,初始触发角为0度。

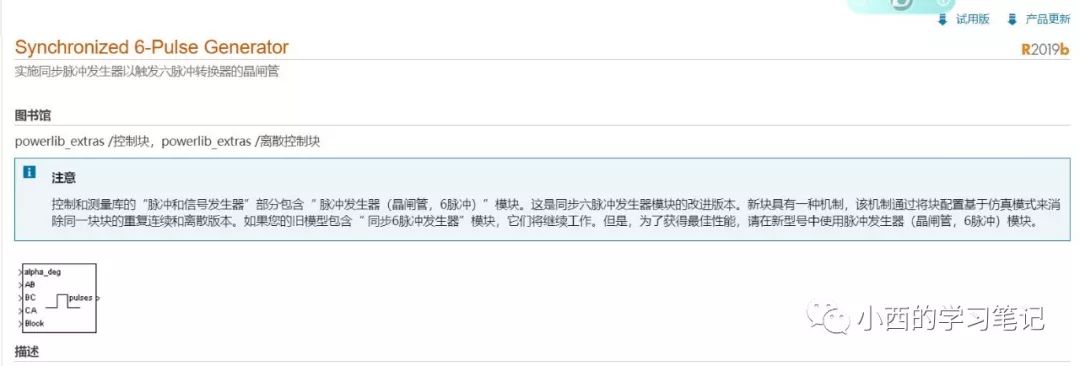

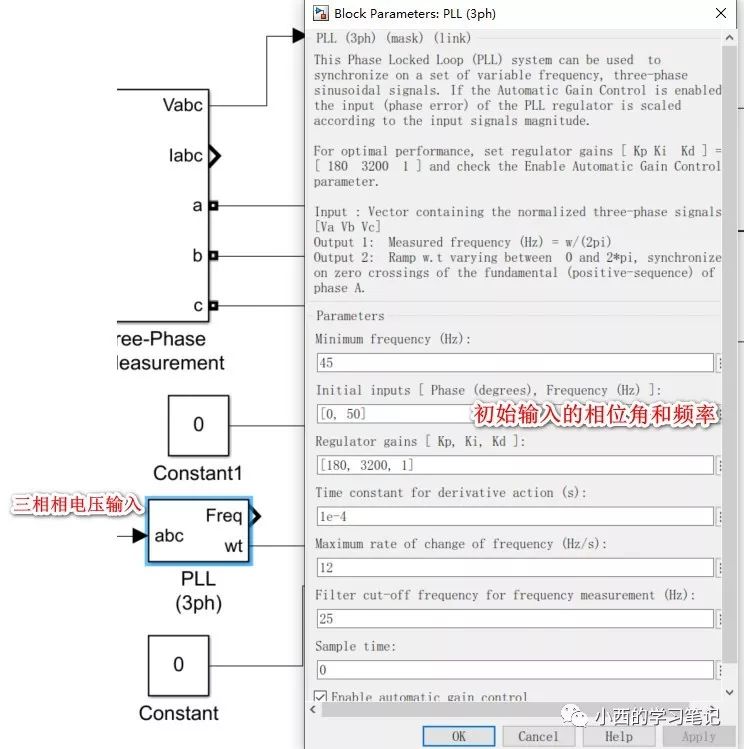

2014版本之前的“PulseGenerator”输入为Vab Vbc Vca,而新版本输入为wt,这个令很多人感到疑惑,实际上,这个wt由锁相环PLL模块提供。

老版本的”Pluse Generator”

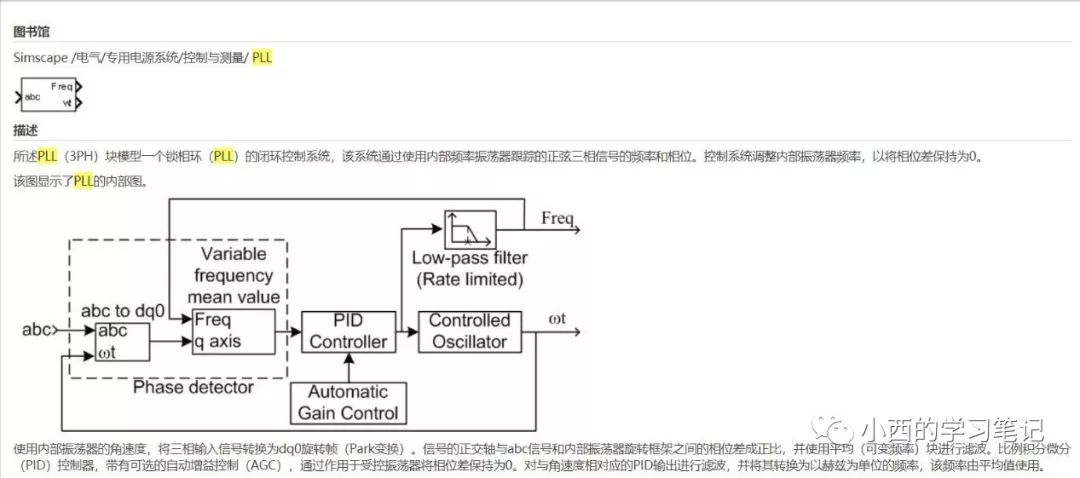

2.三相锁相环PLL模块设置:

锁相环用于检测正弦信号的频率和相位,为控制器提供电压同步信号

一般只需设置初始频率,其他保持默认设置。

“锁相环PLL”技术文档

3.三相相电压的得到:

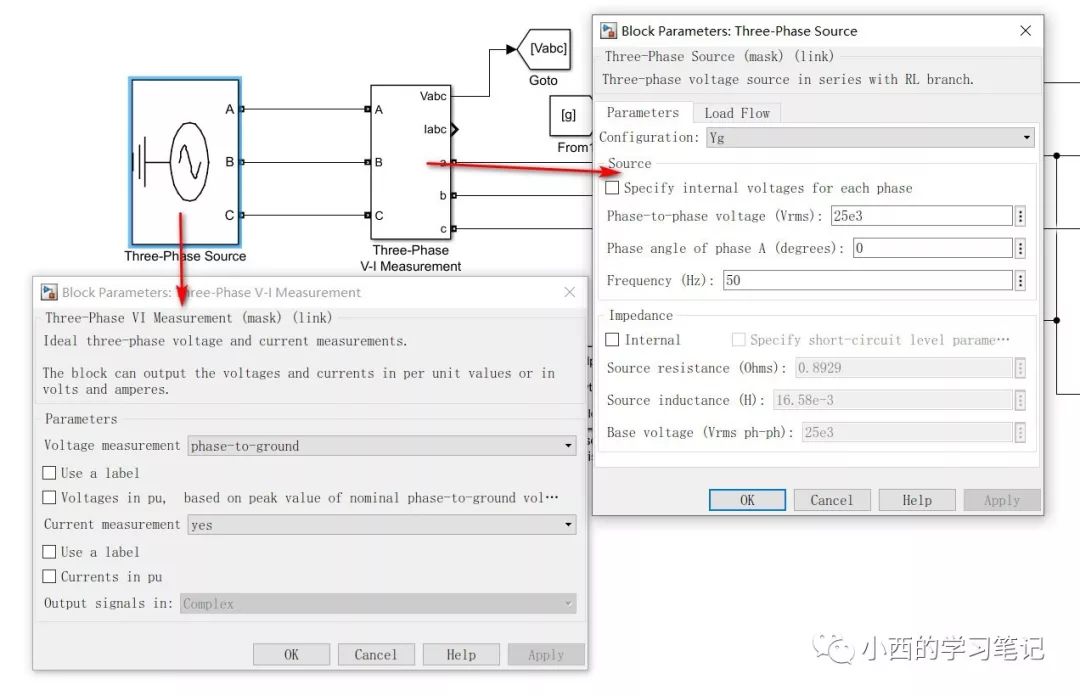

我们使用三相电压源Three-Phase Source和Three-Phase V-I Measurement 来得到。

4.将触发脉冲输出到工作区间:

触发脉冲一个有6个脉冲,我们需要将触发脉冲输出到MATLAB工作空间进行处理,将其以6行1列的形式展示出来,方便对比。

5.使用多功能测量仪Multimeter:

测量三相电压波形、阻性负载的电压以及6触发脉冲。

仿真模型与结果:

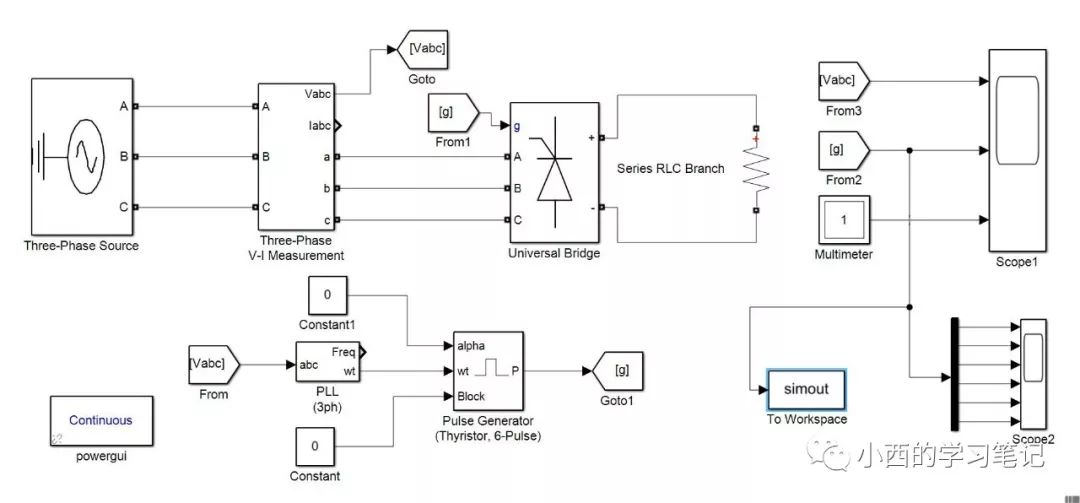

1.模型:

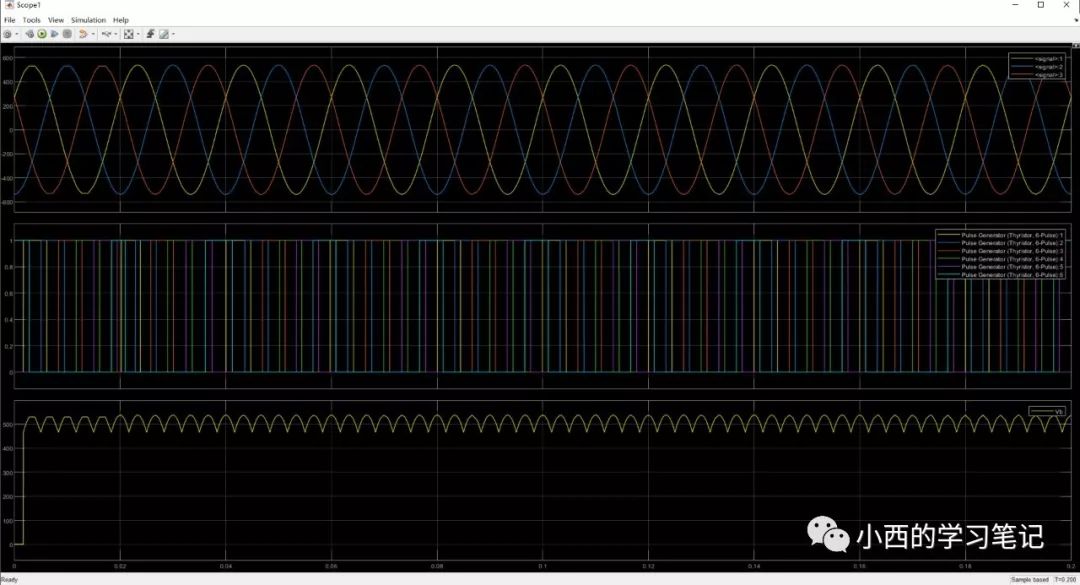

2.仿真波形

从上往下依次是三相电压信号、6脉冲触发信号、阻性负载电压信号,其中我们看到6脉冲触发信号图例有6种颜色。

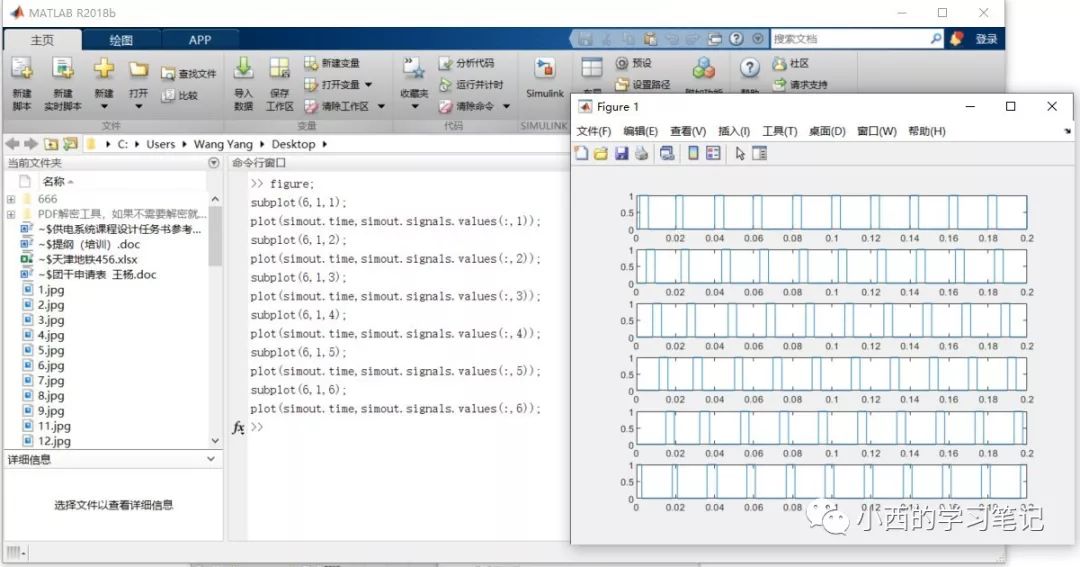

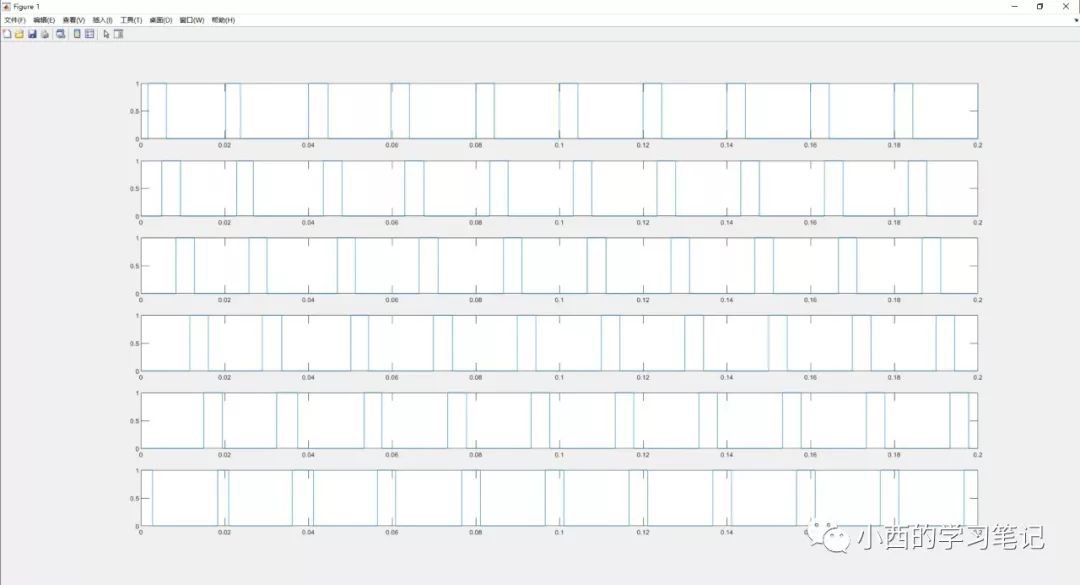

使用To Workspace,将6脉冲数据导入MATLAB工作空间,存为变量simout,在工作区输入以下语句:

figure;

subplot(6,1,1);

plot(simout.time,simout.signals.values(:,1));

subplot(6,1,2);

plot(simout.time,simout.signals.values(:,2));

subplot(6,1,3);

plot(simout.time,simout.signals.values(:,3));

subplot(6,1,4);

plot(simout.time,simout.signals.values(:,4));

subplot(6,1,5);

plot(simout.time,simout.signals.values(:,5));

subplot(6,1,6);

plot(simout.time,simout.signals.values(:,6));

3.处理后的6脉冲波形

-

IGBT三相全桥整流电路原理是什么2024-09-30 13604

-

三相半控桥式整流电路与三相全控整流电路相比有哪些特点2024-02-19 10307

-

基于Matlab的三相桥式全控整流电路的仿真研究2021-11-30 2690

-

三相桥式全控整流电路的基本电路原理2021-11-16 2459

-

三相桥式整流及有源逆变电路的原理和仿真模型2021-11-15 3750

-

三相全控桥式整流电路matlab仿真.doc 精选资料分享2021-07-09 1797

-

基于matlab的三相桥式全控整流电路的仿真研究2021-07-06 1713

-

Matlab的三相桥式全控整流电路如何进行仿真?2021-04-06 3408

-

如何使用Matlab对三相桥式全控整流电路进行仿真研究?2018-09-26 3347

-

半桥逆变snubbber电路//三相桥式全控整流电路2013-06-11 3854

-

采用Matlab/Simulink对三相桥式全控整流电路的仿2010-06-28 12857

-

三相桥式可控整流电路2009-12-10 7788

-

三相PWM整流电路2009-09-09 10204

全部0条评论

快来发表一下你的评论吧 !