提高开关电源效率的方法 怎样提高开关电源效率

电源/新能源

描述

能量转换系统必定存在能耗,虽然实际应用中无法获得100%的转换效率。

但是,一个高质量的电源效率可以达到非常高的水平,效率接近95%。

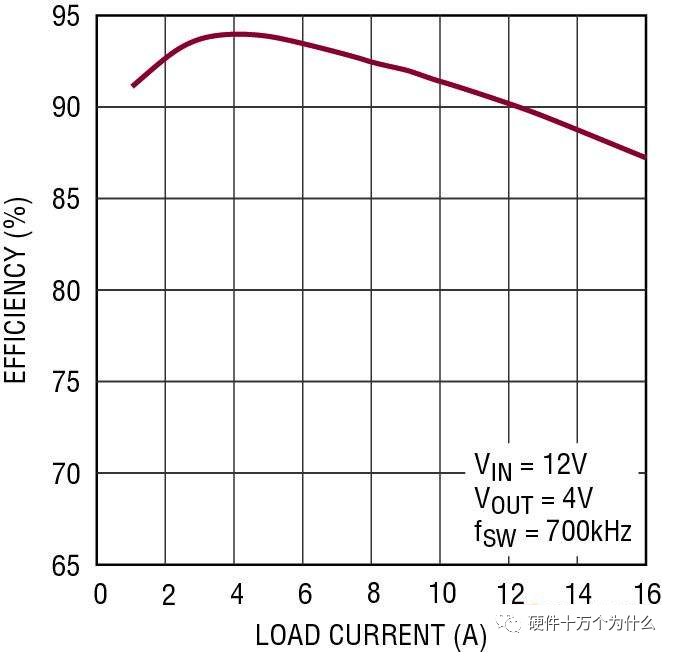

下图是杰华特JW5031S降压转换器集成了低导通电阻的MOSFET,采用同步整流,效率曲线如图所示。

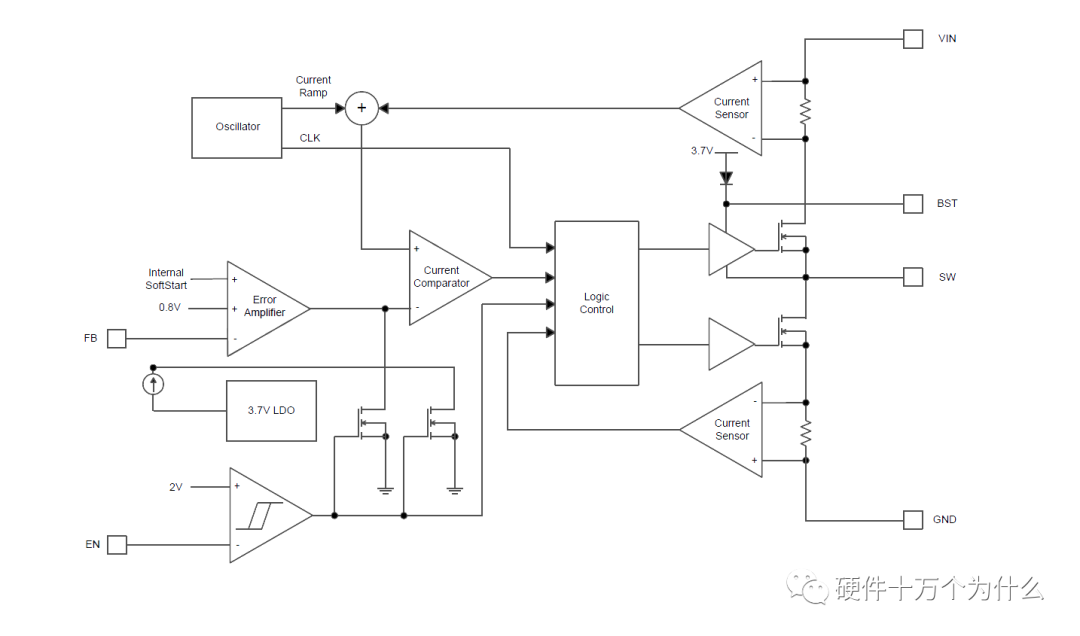

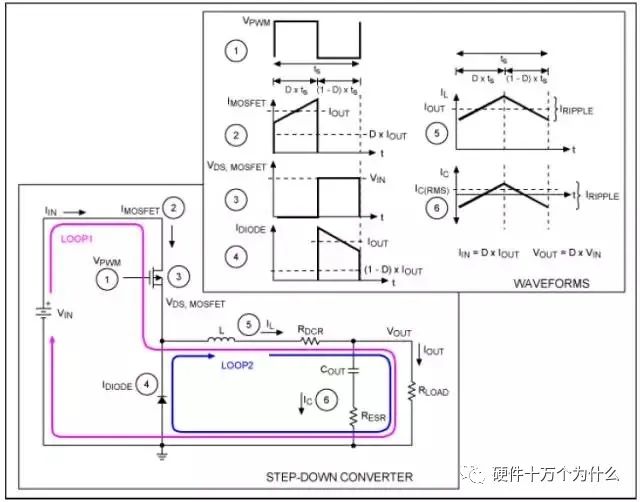

降压转换器的主要功能是把一个较高的直流输入电压转换成较低的直流输出电压。

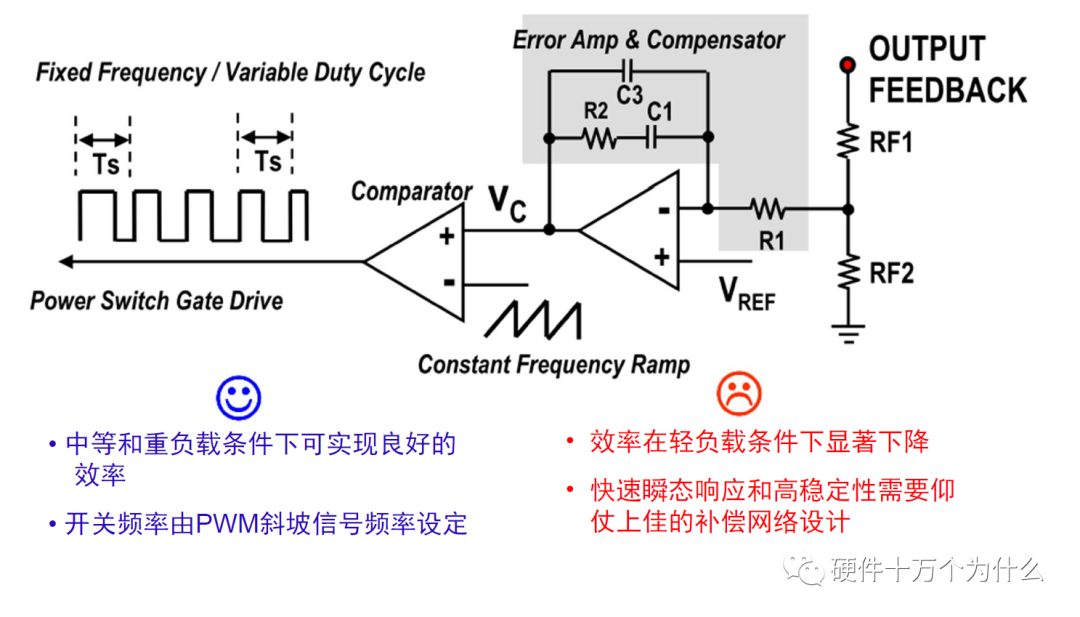

为了达到这个要求,MOSFET 以固定频率(fs),在脉宽调制信号(PWM)的控制下进行开、关操作。

当MOSFET 导通时,输入电压给电感和电容(L 和COUT)充电,通过它们把能量传递给负载。

在此期间,电感电流线性上升,电流回路如上图中的回路1 所示。

当MOSFET 断开时,输入电压断开与电感的连接,电感和输出电容为负载供电。

电感电流线性下降,电流流过二极管,电流回路如上图中的环路2 所示。

MOSFET 的导通时间定义为PWM 信号的占空比(D)。

D 把每个开关周期分成[D × tS]和[(1 - D) × tS]两部分,它们分别对应于MOSFET 的导通时间(环路1)和二极管的导通时间(环路2)。

所有拓扑(降压、反相等)都采用这种方式划分开关周期,实现电压转换。

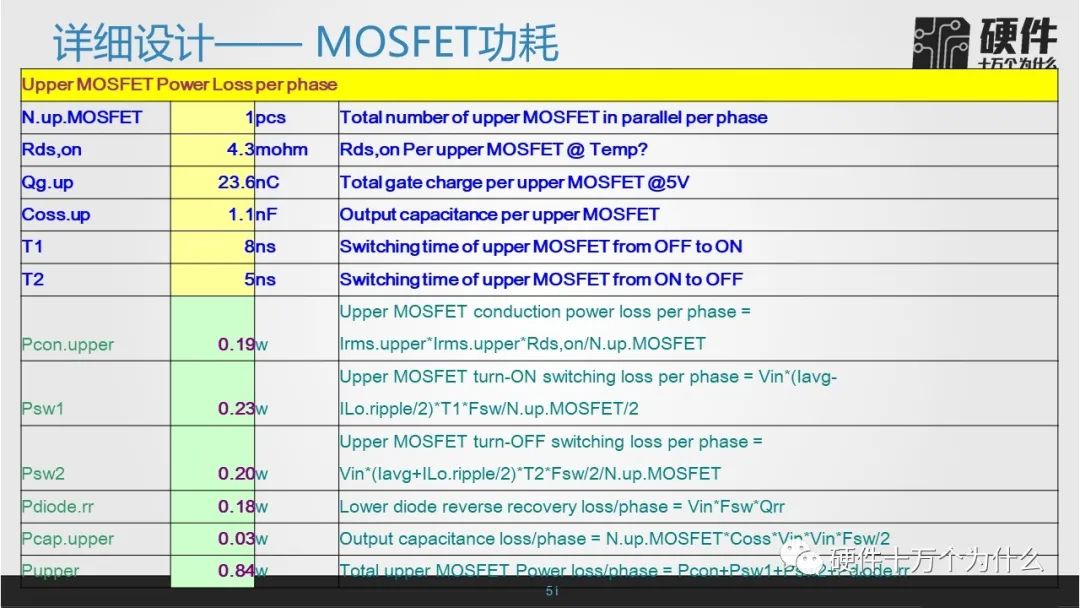

1、MOSFET导通损耗

绝大多数DC-DC 转换器拓扑中的MOSFET 和二极管是造成功耗的主要因素。

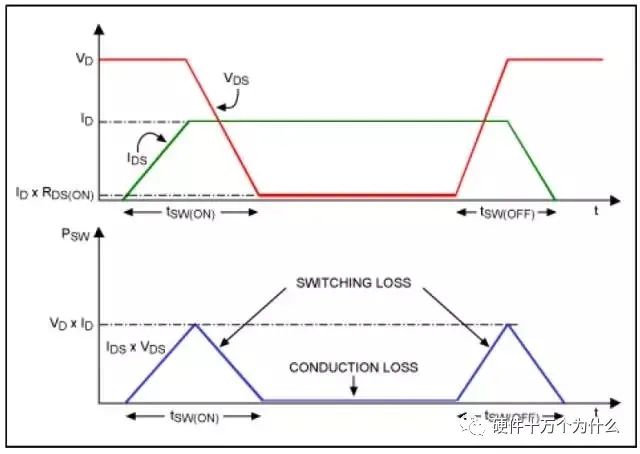

相关损耗主要包括两部分:传导损耗和开关损耗。

MOSFET和二极管是开关元件,导通时电流流过回路。

器件导通时,传导损耗分别由MOSFET 的导通电阻(Rds(ON))和二极管的正向导通电压决定。

MOS作为开关管时的导通损耗

上式给出了中MOSFET 传导损耗的近似值,但它只作为电路损耗的估算值,因为电流线性上升时所产生的功耗大于由平均电流计算得到的功耗。

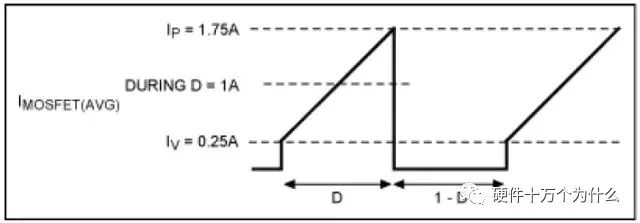

对于“峰值”电流,更准确的计算方法是对电流峰值和谷值(下图中的IV 和IP)之间的电流波形的平方进行积分得到估算值。

典型的降压型转换器的MOSFET 电流波形,用于估算MOSFET 的传导损耗。

更准确的估算损耗的方法,利用IP 和IV 之间电流波形I²的积分替代简单的I²项。

1.1 降低开关管的导通电阻可以有效地降低导通损耗

对于MOSFET而言,降低导通电阻可以有效降低导通损耗。

例如将IRF840换成IRF740可以将导通电阻从0.8Ω降低到0.55Ω,导通损耗可以降低40%以上;

若采用CoolMOS的SPP07N06C3(RDS(ON)=0.6Ω)替代IRFBC40(RDS(ON)=1.2Ω)导通损耗可以降低一半。

MOSFET厂家也是有类似摩尔定律的军备竞赛一样,在Rds(on)的竞争也是非常激烈。主要玩家有英飞凌、NXP等。

1.2增加占空比可以降低导通损耗

在开关管额定电流相同的条件下,占空比为0.5的导通损耗是占空比0.4的导通损耗的80%。

有时为了获得更合理的占空比,不惜采用多级电源转换器。

例如48V产生1V,则先转为12V,再转为1V。12V转1V,采用先转5V,再转1V等方案。

MOSFET作为开关管时,导通损耗一般占开关管总损耗的2/3;

IGBT作为开关管时,导通损耗一般占开关管总损耗的1/3。

1.3 其他降低导通损耗的方法

降额使用,例如将可以输出250W的TOP250用于输出50W的方案中,可以使电源效率达到87%;

选择产品出厂时间比较晚的器件性能会比出厂时间比较早的器件导通电阻小;

选择导通电压降更低的器件作为开关管,例如用IRF740替代IRF840。

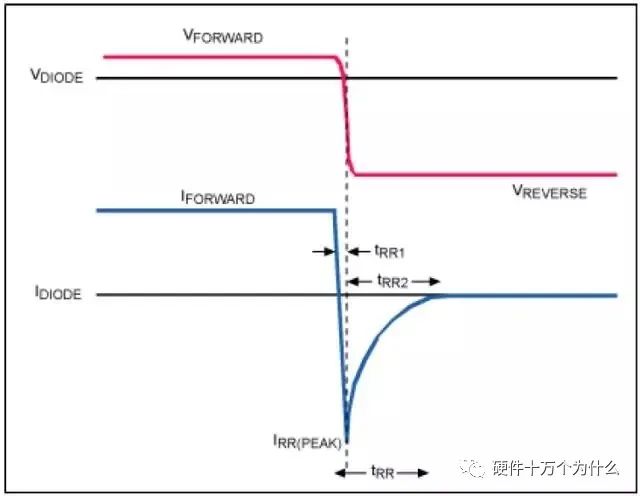

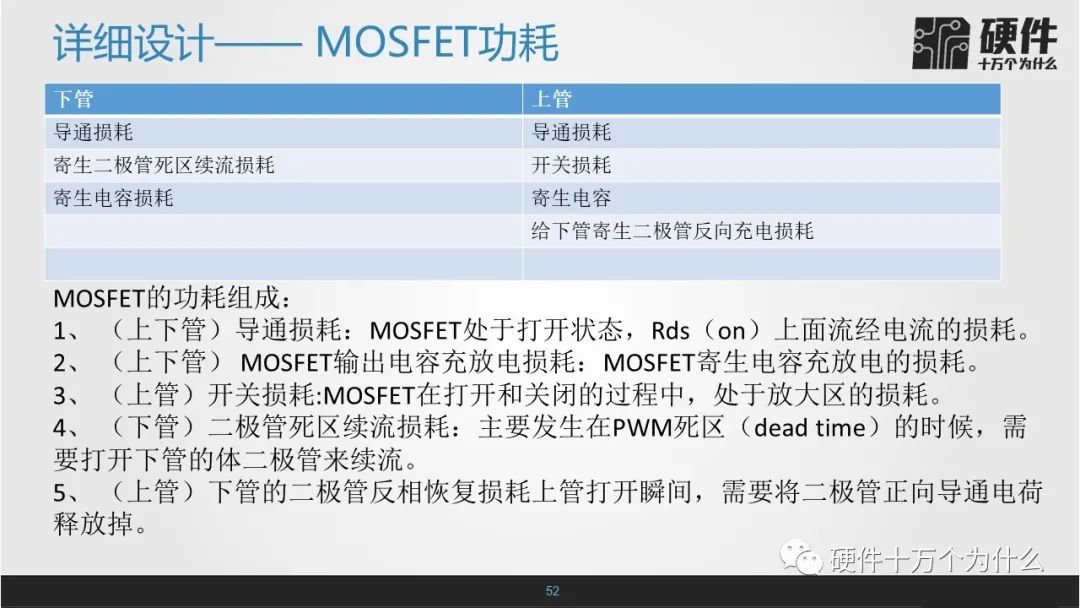

2、二极管导通损耗

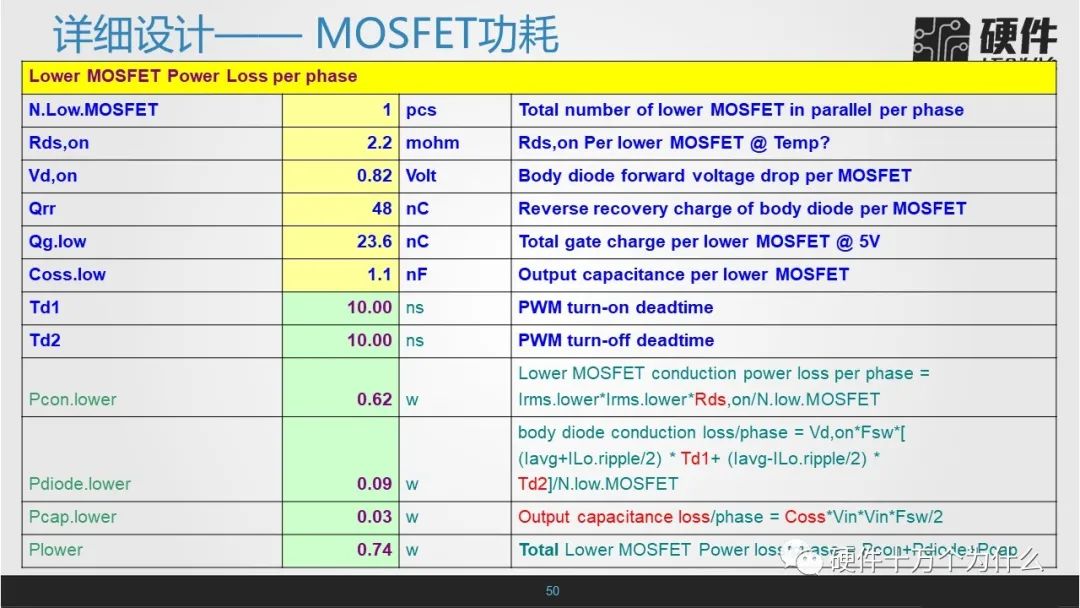

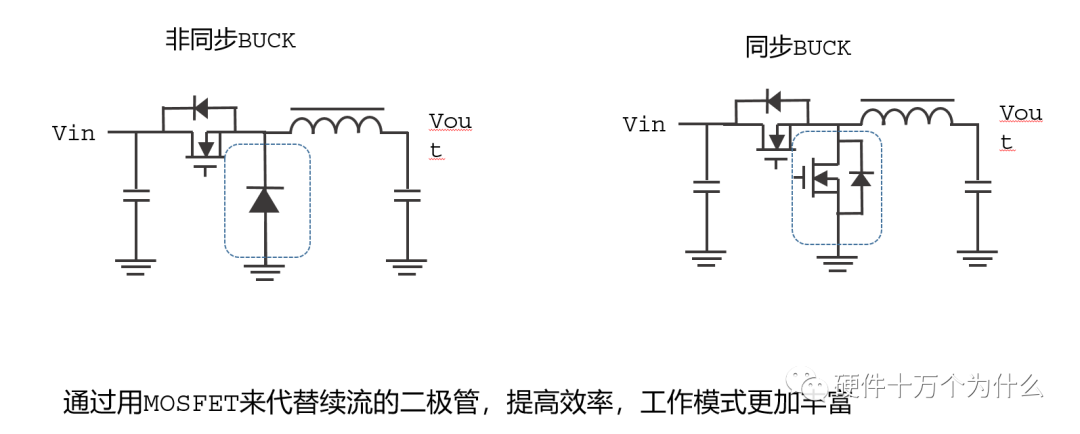

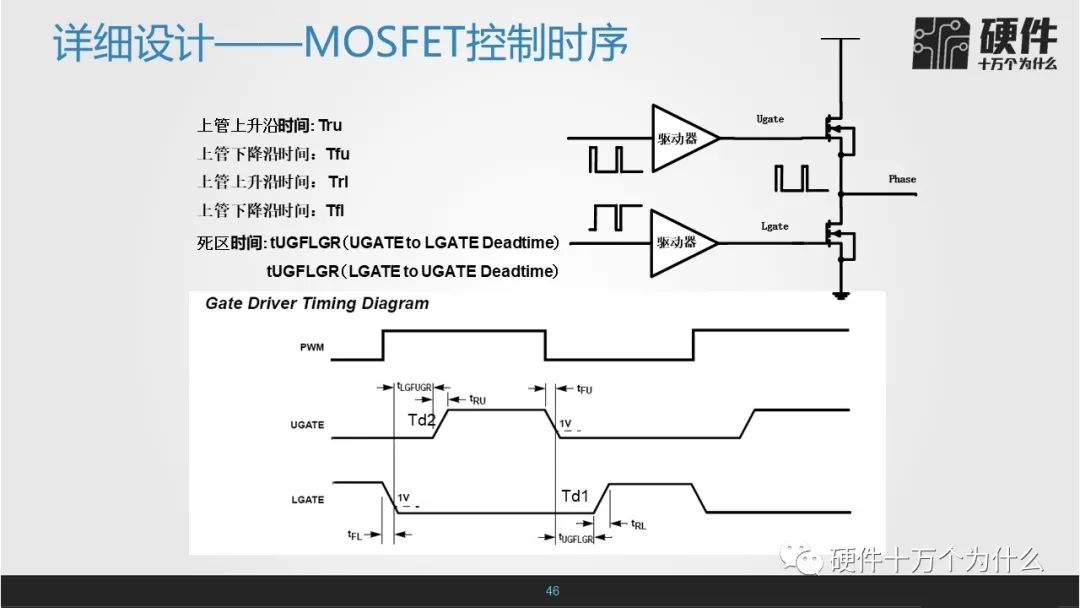

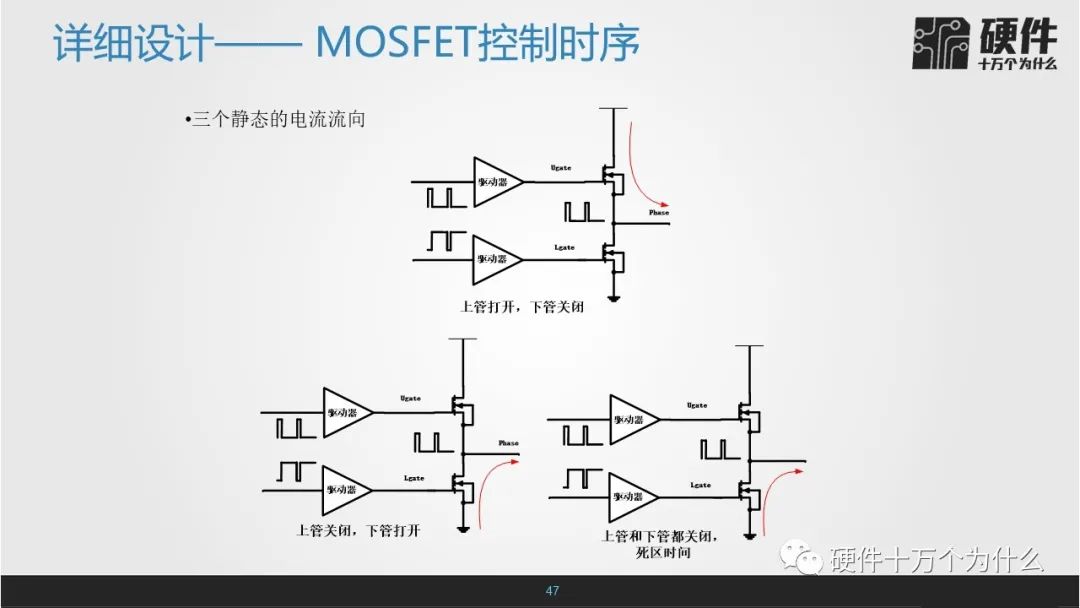

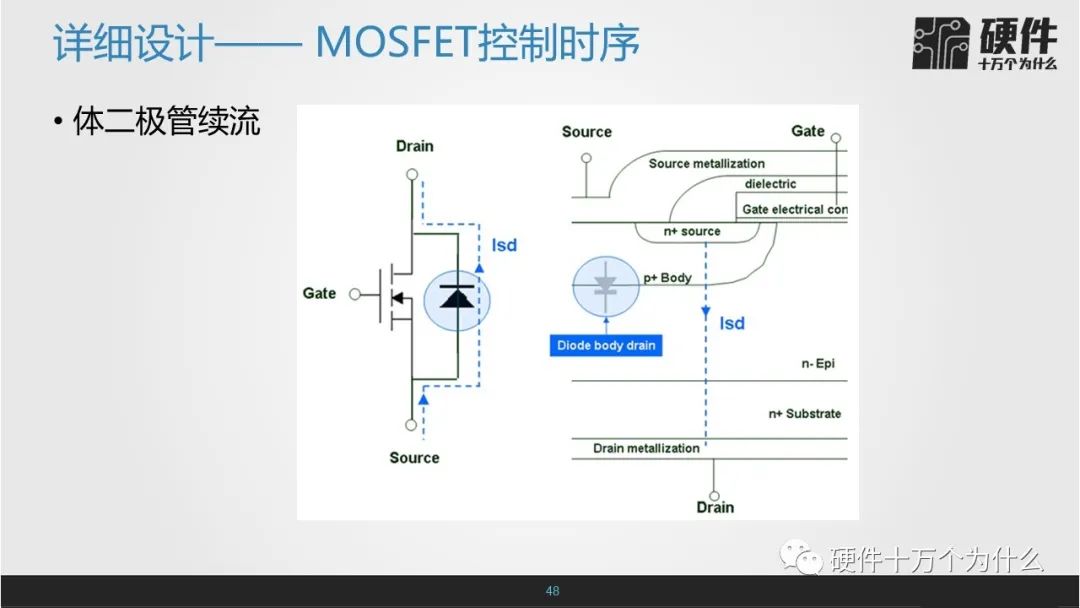

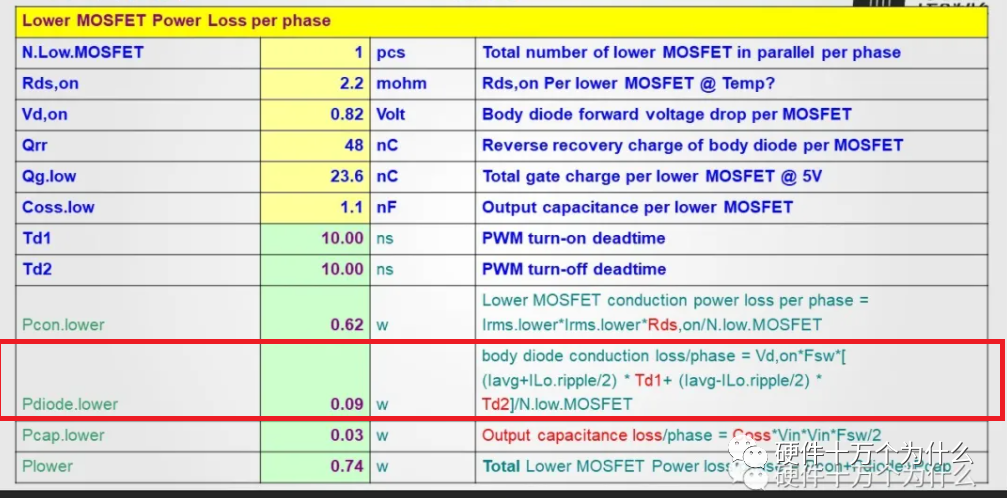

如果是同步控制器,我们需要计算下管的寄生二极管在死区时间的导通损耗。

如果是非同步控制器,我们则需要计算二极管的续流时间的所有损耗。

二极管功耗,与正向导通电压、开关频率、死区时间、平均电流、相数有关。

所以我们需要选择,导通电压更小的MOSFET;

死区时间更小的控制器MOSFET组合;

适当选择开关频率。

3、MOSFET开关损耗

开关损耗随着频率的升高而增大,这一点很容易理解,随着开关频率提高(周期缩短),开关过渡时间所占比例增大,从而增大开关损耗。

开关转换过程中,开关时间是占空比的二十分之一对于效率的影响要远远小于开关时间为占空比的十分之一的情况。

由于开关损耗和频率有很大的关系,工作在高频时,开关损耗将成为主要的损耗因素。

在常规技术下,开关损耗随开关频率的升高而上升,轻载时(如30%负载)开关电源的效率会明显降低。

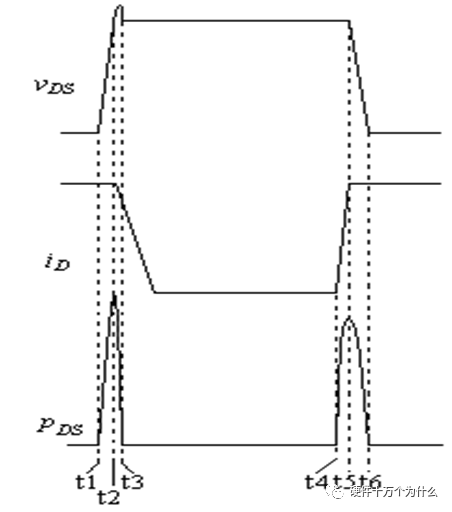

开关管开关过程是开关感性负载,开通过程需要电流首先上升到“电源电流” 然后才是电压的下降;

关断过程则是电压上升到“电源电压”,然后才是电流的下降。

这些过程中,有电压电流同时存在的现象。

其电流、电压的乘积非常高,因而产生开关损耗。

如何降低开关损耗:

在开关管的开关过程中让电流、电压相对 的相位发生变化可以降低开关损耗;

在开关管的开关过程中电流、电压值存在一个,而另一个为零,可以消除开关损耗;

缩短开关过程可以减小开关损耗

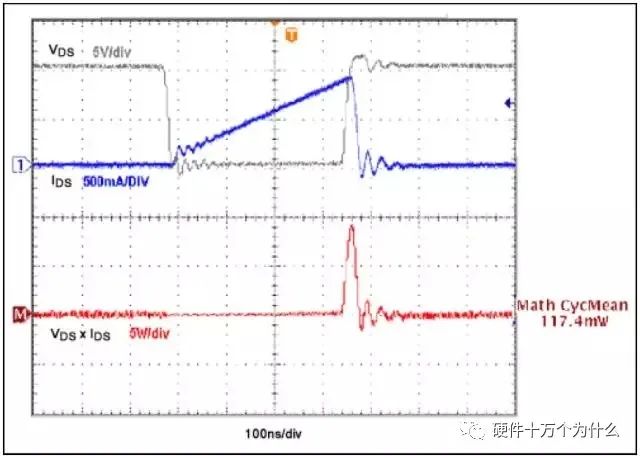

驱动MOSFET能力对开关损耗产生的影响

驱动MOSFET实际上是对MOSFET的栅极电容的充放电过程。

例如在100ns时间内驱动一个100nC栅极电荷的MOSFET由关断到导通或由导通到关断需要1A驱动电流,如果是200mA则驱动时间就会变为500ns。

对应的开关损耗将会增加到1A驱动电流的5倍。

因此,驱动电流对于快速开关MOSFET非常重要。

经常我们在大功率的控制器的驱动管脚需要增加一个专门的控制器来控制MOSFET。

栅极电荷对开关损耗产生的影响

其中对MOSFET开关过程影响最大的是米勒电荷,即栅-漏极电荷。

例如栅极电荷为140nC的IRFP450(14A/500V)的栅-漏极电荷为80nC。

而fairchild的FQAF16N50(16A/500V,全塑封装为11.5A)的栅-漏极电荷为28nC;ST的STE14NK50Z的栅-漏极电荷为31nC。

在相同的驱动条件下,IRFP450的开关时间大约为FQAF16N50的2.86倍;是STE14NK50Z的2.58倍。

对应的ORFP450的开关损耗也将是FQAF16N50的2.86倍,STE14NK50Z的2.58倍。

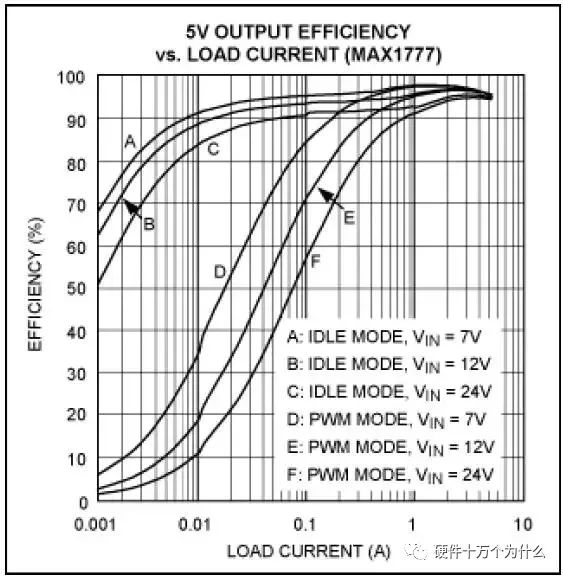

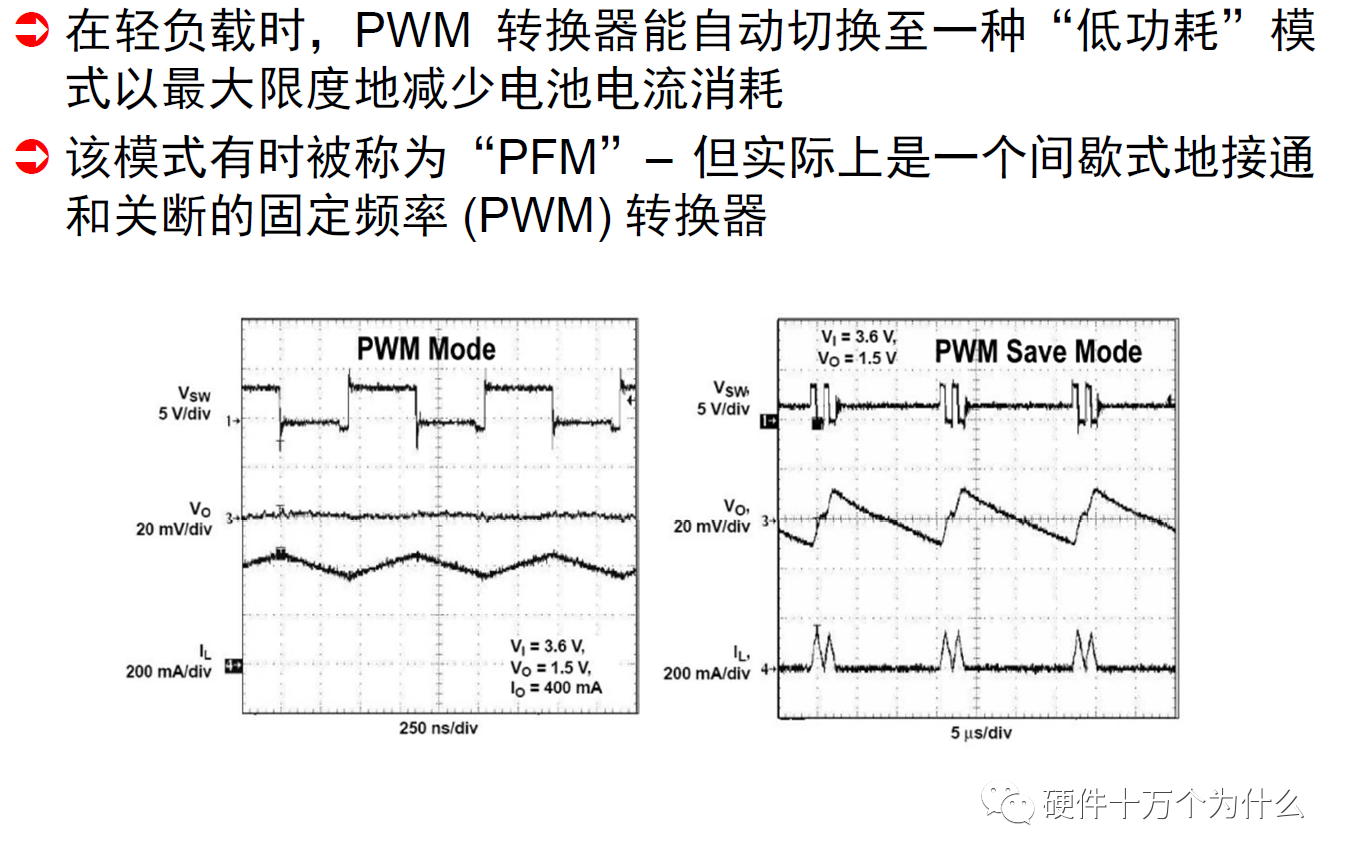

4、切换控制模式实现轻载高效率

另一种重要的控制架构是针对轻载工作或较宽的负载范围设计的,即跳脉冲模式,也称为脉冲频率调制(PFM)。

与单纯的PWM 开关操作(在重载和轻载时均采用固定的开关频率)不同,跳脉冲模式下转换器工作在跳跃的开关周期,可以节省不必要的开关操作,进而提高效率。

跳脉冲模式下,在一段较长时间内电感放电,将能量从电感传递给负载,以维持输出电压。

当然,随着负载吸收电流,输出电压也会跌落。

当电压跌落到设置门限时,将开启一个新的开关周期,为电感充电并补充输出电压。

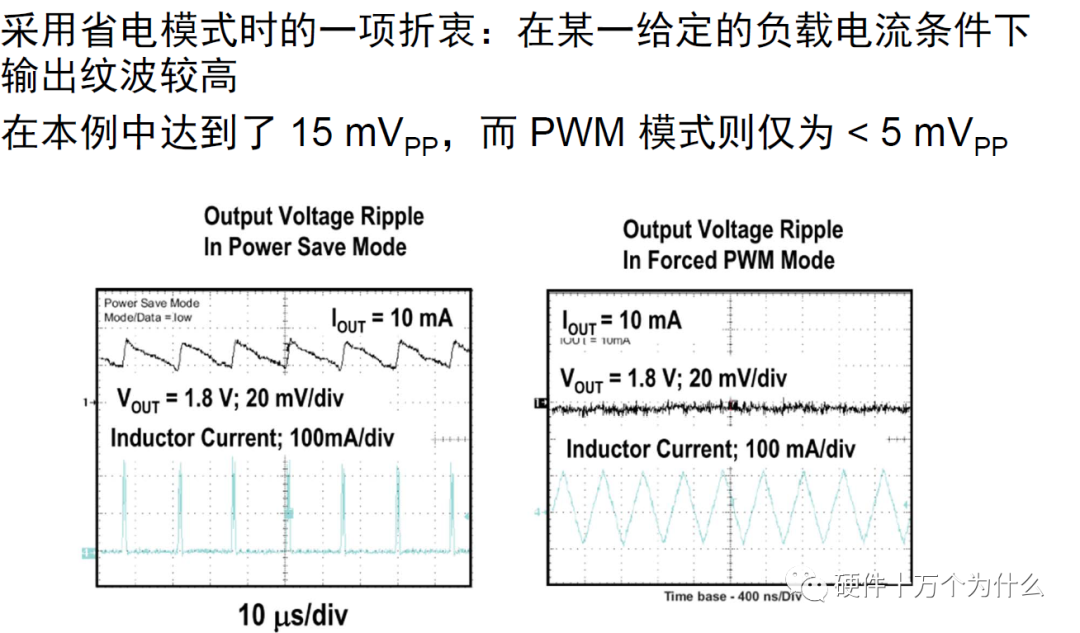

需要注意的是跳脉冲模式会产生与负载相关的输出噪声,这些噪声由于分布在不同频率(与固定频率的PWM 控制架构不同),很难滤除。

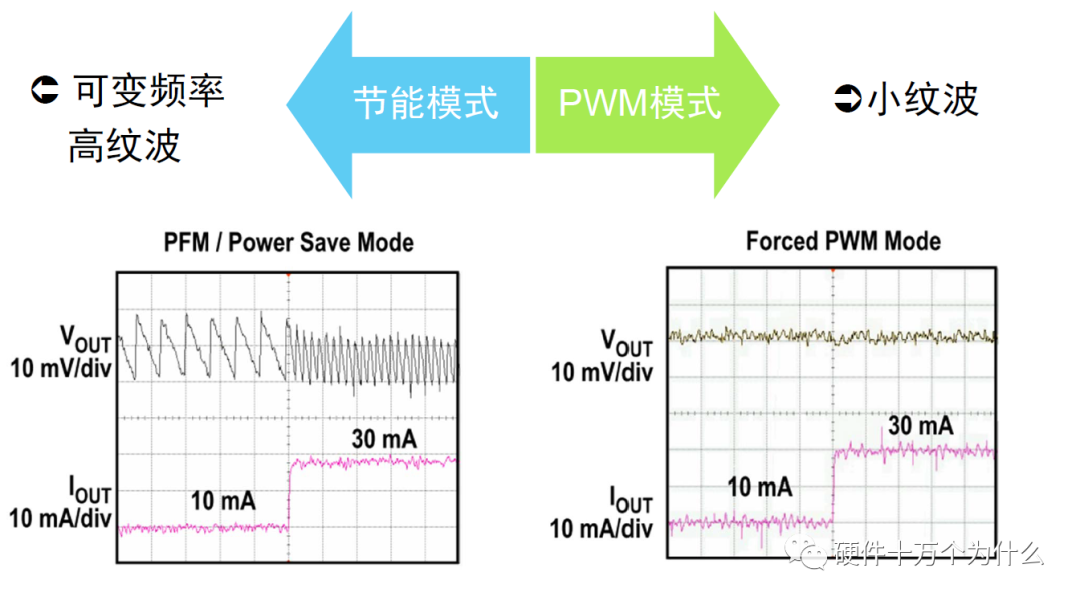

先进的 IC 会合理利用两者的优势:重载时采用恒定PWM 频率;轻载时采用跳脉冲模式以提高效率。

当负载增加到一个较高的有效值时,跳脉冲波形将转换到固定PWM,在标称负载下噪声很容易滤除。

在整个工作范围内,器件根据需要选择跳脉冲模式和PWM 模式,保持整体的最高效率。

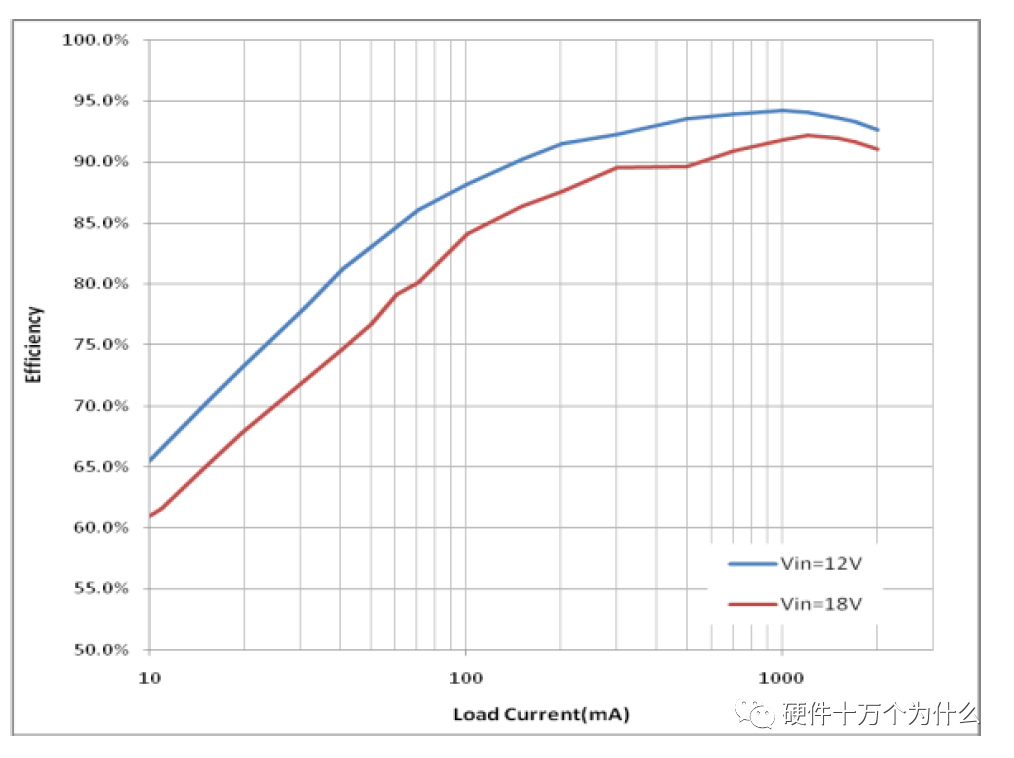

降压转换器在PWM 和空闲(跳脉冲)模式下效率曲线。

注意:轻载时,空闲模式下的效率高于PWM模式。

PWM

PFM 电源纹波

电源纹波

PWM VS PFM

5、电感功耗阻性损耗

电感功耗包括线圈损耗和磁芯损耗两个基本因素,线圈损耗归结于线圈的直流电阻(DCR),磁芯损耗归结于电感的磁特性。

为了获取更低的DCR,有些电感采用非常粗的导体缠绕磁芯,实现电感的值,会造成封装很大。

这也是功率电感封装一般比较大的原因。

已知DCR 和平均电感电流,电感的电阻损耗(PL(DCR))可以用下式估算:

PL(DCR) = LAVG2× DCR

6、磁芯损耗

磁芯损耗并不像传导损耗那样容易估算,很难估测。它由磁滞、涡流损耗组成,直接影响铁芯的交变磁通。

尽管平均直流电流流过电感,由于通过电感的开关电压的变化产生的纹波电流导致磁芯周期性的磁通变化。

磁滞损耗源于每个交流周期中磁芯偶极子的重新排列所消耗的功率,可以将其看作磁场极性变化时偶极子相互摩擦产生的“摩擦”损耗,正比于频率和磁通密度。

相反,涡流损耗则是磁芯中的时变磁通量引入的。由法拉第定律可知:交变磁通产生交变电压。

因此,这个交变电压会产生局部电流,在磁芯电阻上产生I2R 损耗。

磁芯材料对磁芯损耗的影响很大。

SMPS 电源中普遍使用的电感是铁粉磁芯,铁镍钼磁粉芯(MPP)的损耗最低,铁粉芯成本最低,但磁芯损耗较大。

磁芯损耗可以通过计算磁芯磁通密度(B)的最大变化量估算,然后查看电感或铁芯制造商提供的磁通密度和磁芯损耗(和频率)图表。

峰值磁通密度可以通过几种方式计算,公式可以在电感数据资料中的磁芯损耗曲线中找到。

7、电容损耗

电容元件的实际物理特性导致了几种损耗。

这些损耗主要表现在三个方面:等效串联电阻损耗、漏电流损耗和电介质损耗。

电容的阻性损耗显而易见。既然电流在每个开关周期流入、流出电容,电容固有的电阻(ESR)将造成一定功耗。漏电流损耗是由于电容绝缘材料的电阻(RL)导致较小电流流过电容而产生的功率损耗。

电介质损耗比较复杂,由于电容两端施加了交流电压,电容电场发生变化,从而使电介质分子极化造成功率损耗。

8、线路寄生电感产生的开关损耗

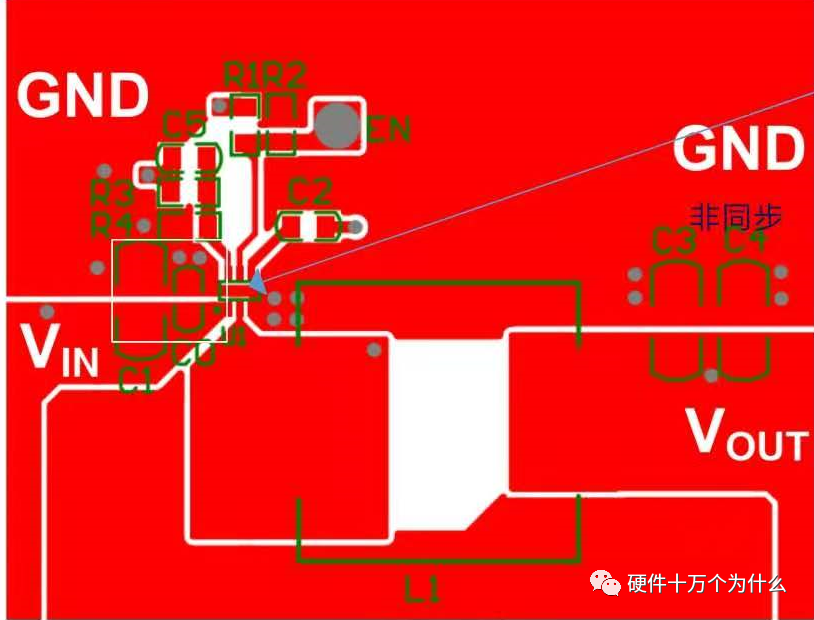

线路的寄生电感在每一次开关过程都要将其储能完全释放到开关管,变为热能,这是造成开关损耗的主要原因之一。所以我们可以减短功率路径的走线长度。

9、缓冲电路损耗

为了降低开关电源的电磁干扰,需要降低开关管的di/dt、dv/dt,常利用缓冲电路实现。如果缓冲电路是RC或RCD形式,就会产生损耗。

如果选用LC或LCD电路形式则可以大幅度降低缓冲电路的损耗。这其中还是存在L、D的损耗以及电容器电压复位时的开关管的损耗。

采用软开关或零电压开关可以省去缓冲电路,也没有了缓冲电路的损耗。

审核编辑:刘清

-

开关电源的效率优化方法 如何定制开关电源解决方案2024-11-29 5089

-

怎样提高开关电源效率2023-08-27 4665

-

怎么才能提高开关电源的效率呢2023-08-01 4583

-

怎样去提高开关电源的转换效率2021-11-15 1424

-

提高开关电源待机效率的方法2021-06-17 1041

-

降频和Burst Mode方法提高开关电源待机效率2019-04-15 3029

-

如何提高开关电源效率2017-03-22 1549

-

11个提高开关电源效率的小技巧2016-09-06 862

-

高效率开关电源设计与制作2016-06-12 5400

-

怎么提高开关电源的待机效率2015-09-06 4000

-

如何将开关电源工作效率提高2013-11-18 2633

-

请问怎么提高开关电源效率?2012-05-16 1901

-

揭秘怎样提高开关电源待机效率2011-12-14 7573

-

高效率开关电源的研制2008-12-21 1379

全部0条评论

快来发表一下你的评论吧 !