什么原因会影响TSV的可靠性呢?

电子说

描述

就像PCB中的高纵横比通孔和小直径通孔一样,半导体封装中的3D互连也面临着与3D晶片堆栈的热力学行为相关的可靠性挑战。同样的挑战也出现在用于2.5和3D封装的硅中间层的3D互连中。具有讽刺意味的是,这些可靠性挑战最初是在围绕半导体的学术文献中观察到的,现在PCB行业正在处理与电子组装规模较小相同的挑战。

目前的垂直互连技术由硅通孔组成,其中铜互连用于在中间插口或堆叠小片中的电触点之间路由垂直连接。随着越来越多的设计以更高的功率运行,并且在垂直堆叠中包含更多的骰子,3D集成封装的热机械可靠性成为系统级设计中需要解决的一个重要问题。

#1

TSV可靠性失效机制

TSV的可靠性研究已经进行了多年,并提出了许多提高TSV可靠性的解决方案。确保任何制造结构的可靠性需要了解主要失效机制,在TSV中可以观察到的两种主要失效机制是:

CTE失配引起的应力

TSV电迁移失败

这些失效机制可以在用于2.5D/3D封装的中间体的TSV中观察到,也可以在用于3D堆叠小芯片的TSV中观察到。

#2

应力导致开裂

应力诱发的TSV结构失效主要是由于硅(2-3ppm/°C)和铜(16-17ppm/°C)之间的CTE不匹配。与PCB中使用的较大过孔和HDI PCB中使用的微过孔一样,TSV各部分的应力集中将导致不同类型的机械诱发故障。此外,热循环会导致TSV结构的应力集中区域出现疲劳。

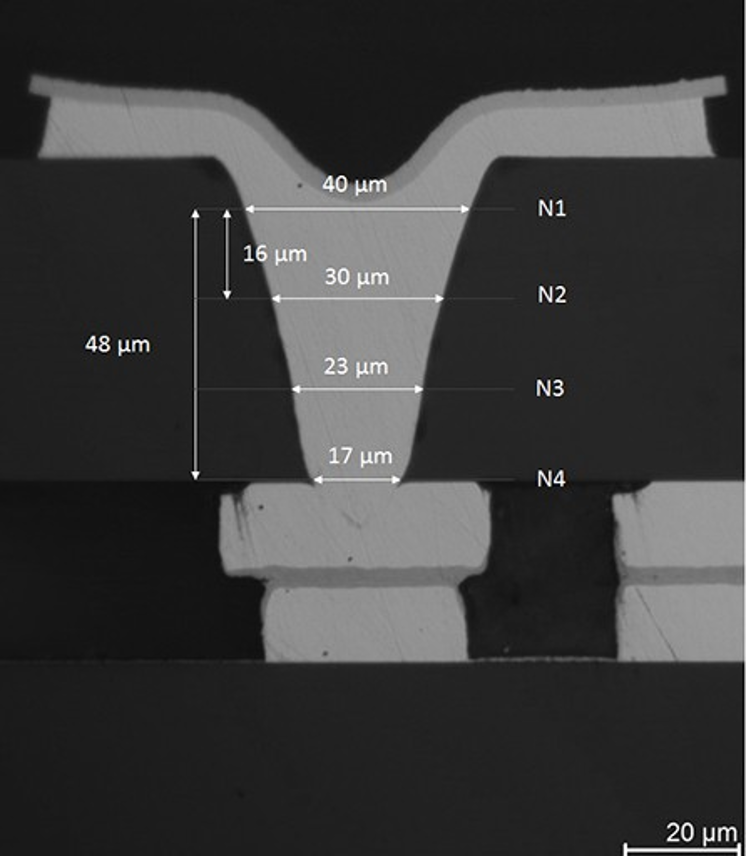

如果我们检查TSV结构的横截面,它看起来非常类似于HDI PCB中的盲通结构。较大的热失配会在TSV的上下表面产生应力集中,导致铜断裂、扩散和污染等多种影响。

扫描电镜图像显示TSV在微凸点顶部的横截面

(来源:弗劳恩霍夫电子纳米系统研究所)

在这种类型的结构中可能出现的一些问题包括:

将铜泵入后端管线(BEOL)区域或再分配层(RDL)

铜沿铜-半导体界面从种子层剥离

退火效应(铜形态的变化)由于反复的热循环和膨胀/收缩

铜在长时间暴露于高温后从结构中扩散出去

形成脆性金属间化合物,更容易断裂

#3

TSV中的电迁移

电迁移是长期可靠性的另一个驱动因素,当TSV结构开始出现裂纹时,电迁移会加速机械失效。TSV中的电迁移发生的机制与集成电路中的轨道相同:金属在电流影响下的扩散。中间层和3D堆叠小芯片中使用的TSV必须通过堆叠携带一些电流,为封装中的组件提供电源和信号.

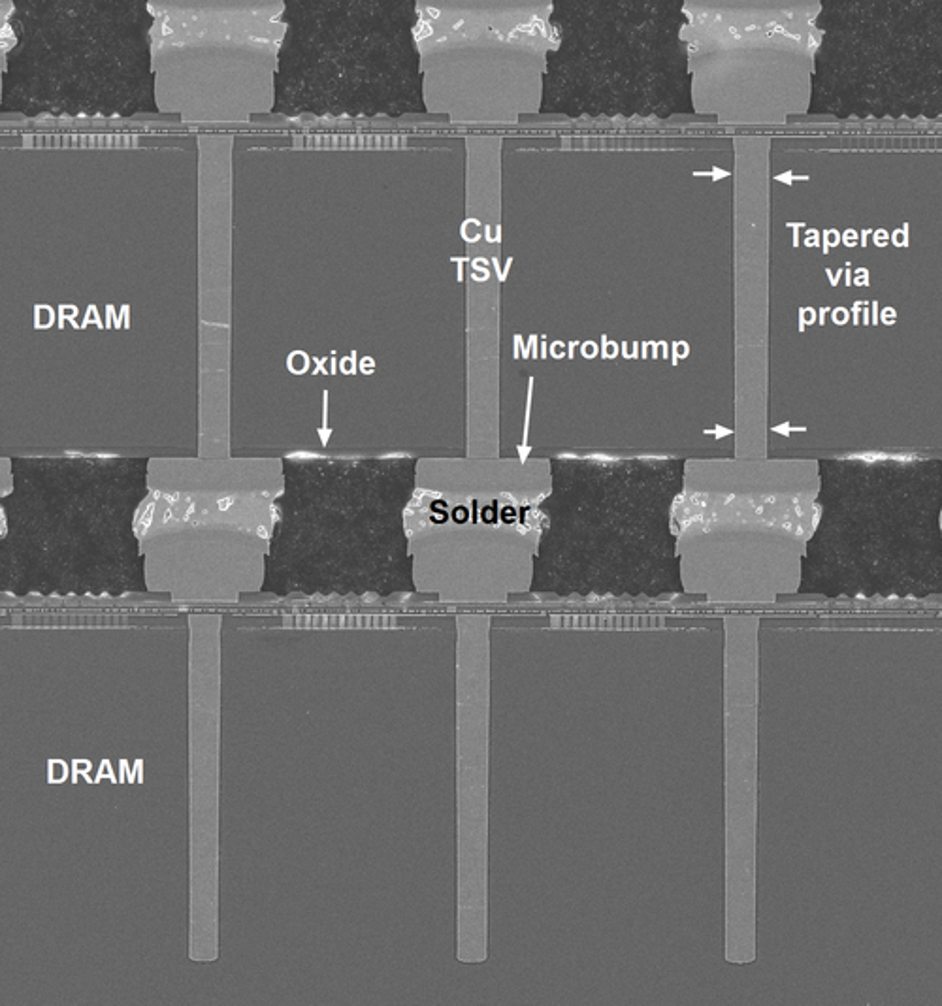

较小的TSV通常用于3D堆叠芯片,由于尺寸较小,在给定电压水平下通常携带更大的电流密度。根据布莱克方程,这意味着对于传播信号中包含的给定功率水平,它们更有可能经历电迁移失败。当我们观察用于具有HBM接口的DRAM 3D堆叠的典型TSV的横截面时,可以确定更容易发生电迁移的位置。

(用于DRAM堆栈的TSV)

一旦制造完成,TSV通常会留下轻微的锥度,其中结构底部的通孔更薄。较薄的区域由于其截面积较小,因此电流密度较大,因此电迁移更有可能首先发生在那里。结果会形成空洞,最终导致开路。一旦空洞开始形成,空洞也会成为应力集中的区域,并可能发生机械断裂。

#4

工艺优化有助于提高可靠性

在TSV中,电迁移和机械应力之间存在重要的相互作用,这需要工艺优化以确保这些问题得到解决。具有更均匀轮廓的TSV可以防止应力集中,使用阻挡层来防止电迁移,使用高热退火和抛光来防止泵送,以及保形衬里沉积工艺可以帮助防止TSV中的铜断裂,污染和扩散。 接下来,给各位推荐一个大型行业技术交流论坛。

审核编辑:刘清

-

TSV三维堆叠芯片的可靠性问题2024-12-30 3280

-

#硬声创作季 #可靠性 电子封装可靠性评价中的实验力学方法-1水管工 2022-09-29

-

TCP协议如何保证可靠性呢2021-12-24 1938

-

无线模块校验失败是什么原因呢2021-10-13 2791

-

2Pro AC器件是如何提高设备可靠性的?又是什么原因致使驱动芯片损坏的呢?2021-04-06 1876

-

影响硬件可靠性的因素2021-01-25 2660

-

什么是高可靠性?2020-07-03 14455

全部0条评论

快来发表一下你的评论吧 !