介绍dsPIC33C系列MCU带高速PLL的振荡器模块

控制/MCU

描述

本文介绍dsPIC33C系列MCU 带高速PLL的振荡器模块,对于任何MCU来说,系统基础时钟配置都很关键,务必清晰。

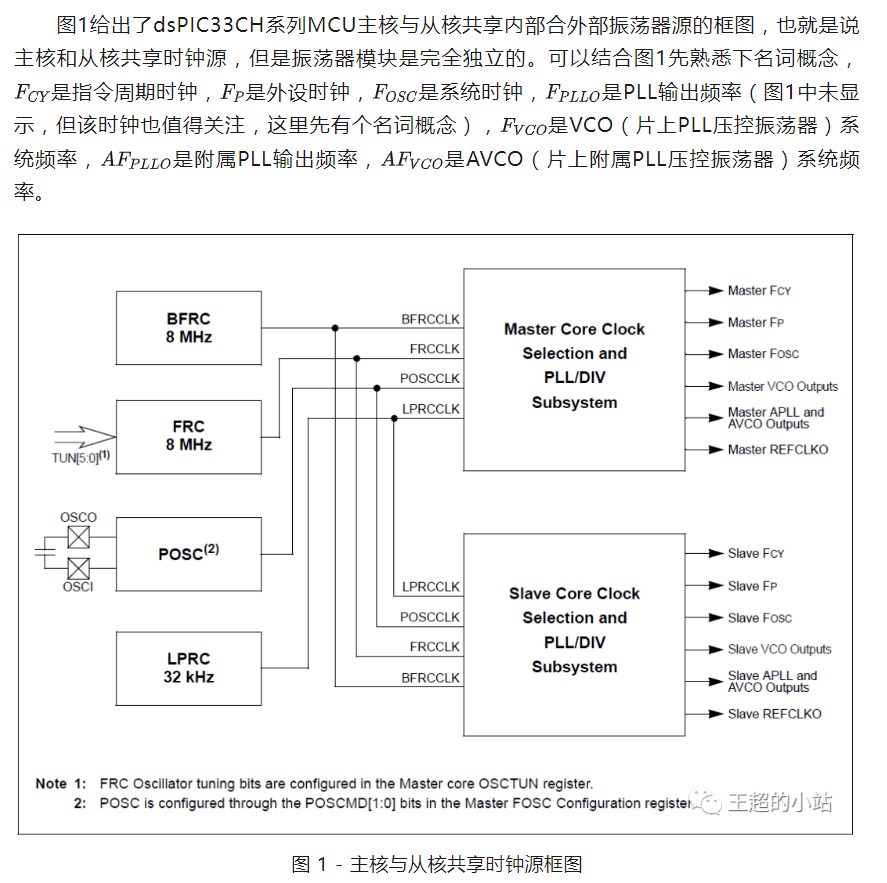

1. 上电启动逻辑

图1中我们已经知道了主核与从核共享时钟源,接下来看下主核和从核如何选择时钟源。参见表1,对于主核时钟源的选择靠配置位FNOSC<2:0>和POSCMD<1:0>来处理,对于从核时钟源的选择靠配置位S1FNOSC<2:0>和POSCMD<1:0>处理。

表 1 - 输入时钟源选项

一般在MCU上电启动过程中先选择内部8MHz的FRC振荡器,因为内部FRC可以立即起振,与需要数毫秒起振的晶振不同。然后系统若不接外部振荡器则进一步切换为带PLL后分频的FRC振荡器;若有接外部振荡器,则根据所接外部振荡器的情况切换为带PLL的主振荡器。后者的PLL主要是为了获得100MIPS的系统时钟(这里也就是100MHz的指令周期时钟)。

上述描述看起来是双速启动(使能靠配置寄存器FOSCSEL<7>或FS1OSCSEL<7>的IESO和S1ESO)的概念,通过内部FRC振荡器启动,然后切换到用户选择的振荡器。当受限于PLL模式在启动时输入的限制,即PLL锁相环相关寄存器的默认值无法满足实际项目需要,因此实际应用中一般设置FNOSC<2:0>或S1FNOSC<2:0>值为0x0,然后设置好PLL锁相环相关的寄存器及其他所有振荡器寄存器后采用手动的方式切换到最终的带PLL后分频的FRC振荡器或带PLL的主振荡器(靠OSCCON寄存器的NOSC<2:0>指定)。

为了允许时钟切换,需要对时钟切换模式配置位(FCKSM<1:0>或S1FCKSM<1:0>)(分别为FOSC<7:6>或FS1OSC<7:6>)进行编程,取值0x1或0x0。进一步在启动时钟源切换后,需要判断OSWEN位(OSCCON<0>)是否硬件清零,清零则切换成功。额外的也需检查下PLL LOCK位(OSCCON<5>),确保PLL处于锁定状态。

2. 主振荡器引脚功能

未使用振荡器时,主振荡器引脚(OSC1和OSC2)可用于其他功能。振荡器配置寄存器中的POSCMD<1:0>配置位(FOSC<1:0>)决定振荡器引脚的功能。OSCIOFNC位(FOSC<2>)与S1OSCIOFNC(FS1OSC<2>)决定OSC2引脚的功能。一般在不用外部振荡器或者外部振荡器为EC模式时,将OSC2引脚功能配置为数字I/O。

表 2 - 时钟引脚功能选择

3. 振荡器子系统

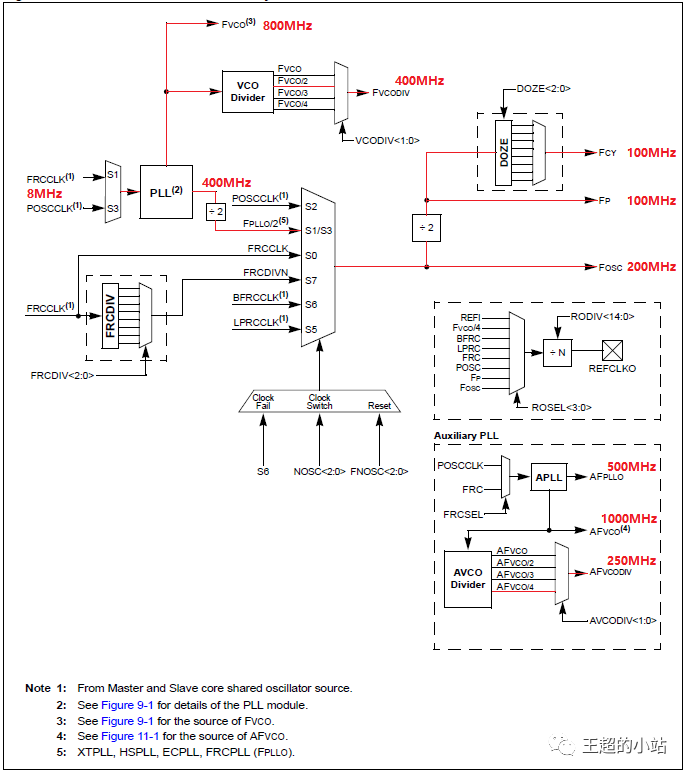

图 2 - dsPIC33CH主核振荡器子系统

图 3 - dsPIC33CH从核振荡器子系统

图 4 - dsPIC33CK振荡器子系统

上面介绍了个人喜欢的振荡器子系统,那么接下来我们主要看下PLL和APLL的相关设置情况,因内部FRC振荡器的频率为8MHz,所以若选用外部振荡器也推荐使用8MHz的外部振荡器,这样关于锁相环的设置无论选用内部FRC振荡器还是外部振荡器,对于锁相环的配置都是一样的,将多种可能的时钟配置固化为一种可以有效规避时钟配置中的小错误,小陷阱。所以接下来涉及的时钟具体配置例程均基于FRCCLK和POSCCLK都为8MHz时钟。

3.1 主核和从核锁相环(PLL)设置

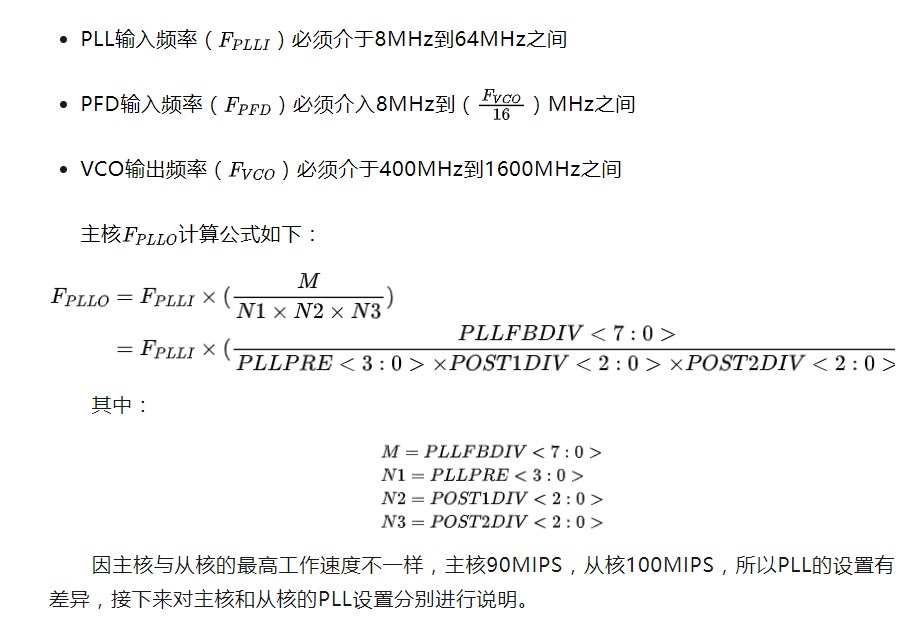

主振荡器核内部FRC振荡器可选择使用片上PLL来获取最高的工作速度。图5给出了PLL模块的框图。

图 5 - PLL和VCO详细信息

为了让PLL工作,必须始终毫无例外地满足以下要求:

3.1.1 主核PLL设置

3.1.2 从核PLL设置

注意:对于dsPIC33CK单核MCU,可以选取上述从核的PLL设置,因为dsPIC33CK单核MCU的核dsPIC33CH双核MCU的最高工作速率都是100MIPS。

3.2 主核和从核附属锁相环(APLL)设置

附属PLL用来生成独立于系统时钟的各种外设时钟源。图6给出了主核PLL模块的框图。

图 6 - 主核APLL和VCO详细信息

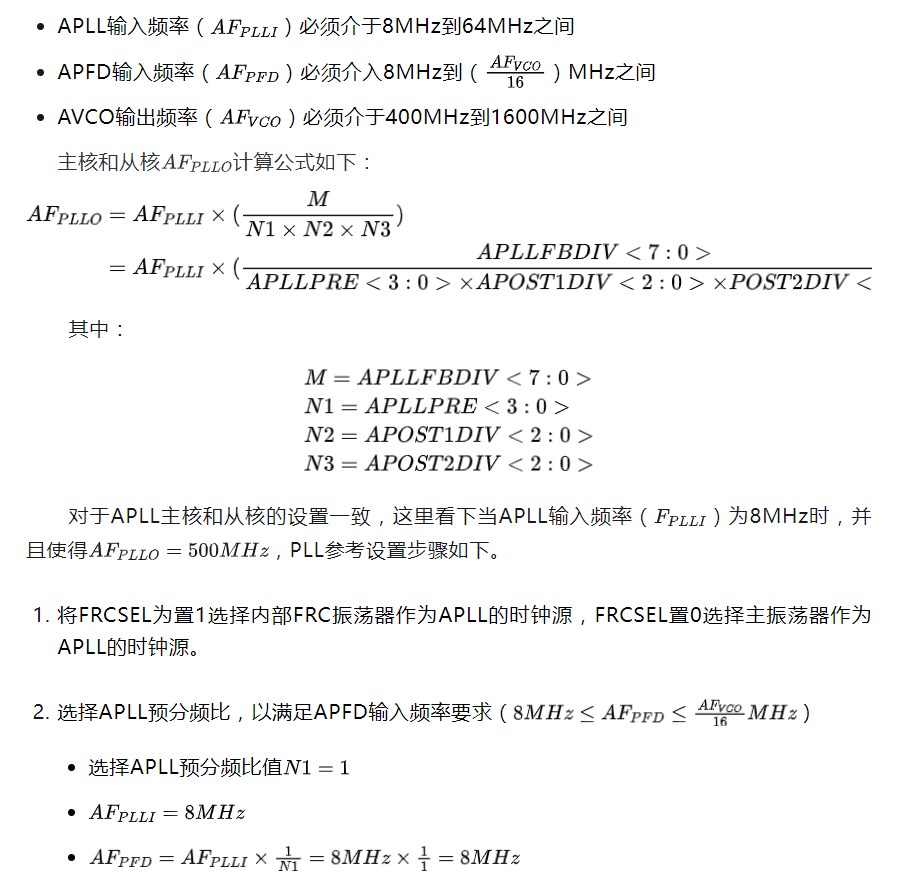

为了让APLL工作,必须始终毫无例外地满足以下要求:

注意:对于dsPIC33CK单核MCU APLL的设置与上述保持一致。

-

dsPIC33C Touch-CAN-LIN Curiosity开发板用户指南2025-01-22 370

-

带高速PLL的振荡器模块2023-09-25 1406

-

高速模拟比较器-斜率生成模式原理介绍2023-07-22 3975

-

dsPIC33C数字电源入门工具包用户指南2021-04-29 1522

-

dsPIC33上的高速PWM模块未切换2020-04-13 1483

-

dsPIC33EP256MU806 RTCC模块的辅助振荡器?2020-04-06 1726

-

dsPIC33EP32MC202内部振荡器配置怎么改变?2020-04-01 1815

-

CVCO33CL-0453-0504 压控振荡器2018-07-13 1375

-

dsPIC33F系列参考手册之振荡器(第IV部分)2018-06-22 1033

-

dsPIC33E/PIC24E系列参考手册之振荡器2018-06-06 1196

-

dsPIC33F/PIC24H系列参考手册之高速模拟比较器2018-05-25 1382

全部0条评论

快来发表一下你的评论吧 !