什么是硅或TSV通路?使用TSV的应用和优势

存储技术

描述

从HBM存储器到3D NAND芯片,再到CoWoS,硬件市场上有许多芯片是用英文称为TSV构建的,TSV是首字母缩写,意为“通过硅通孔”并翻译为via硅的事实,它们垂直地穿过的芯片和允许在它们之间垂直互通。在本文中,我们将告诉您它们是什么,它们如何工作以及它们的用途。

在2000年的第一个月,Santa Clara University的Sergey Savastiou教授在Solid State Technology期刊上发表了一篇名叫《Moore’s Law – the Z dimension》的文章。这篇文章最后一章的标题是Through-Silicon Vias,这是 Through-Silicon Via 这个名词首次在世界上亮相。这篇文章发表的时间点似乎也预示着在新的千禧年里,TSV注定将迎来它不凡的表演。

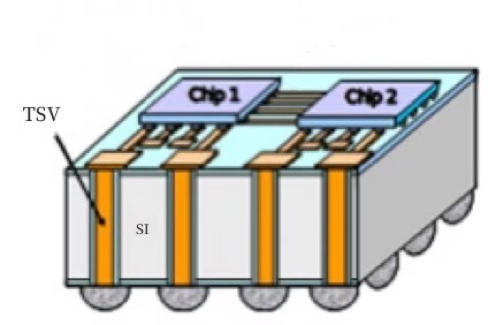

TSV示意图

TSV,是英文Through-Silicon Via的缩写,即是穿过硅基板的垂直电互连。

如果说Wire bonding(引线键合)和Flip-Chip(倒装焊)的Bumping(凸点)提供了芯片对外部的电互连,RDL(再布线)提供了芯片内部水平方向的电互连,那么TSV则提供了硅片内部垂直方向的电互连。 作为唯一的垂直电互连技术,TSV是半导体先进封装最核心的技术之一。

90年代中期,半导体行业发生一件大事: IBM用铜电镀大马士革工艺全面替代的溅射铝作为集成电路中晶体管互连。这样电镀铜在半导体行业便开始成为标准工艺,这让电镀铜用于TSV的微孔金属化填充更加顺理成章。 至此, 现代TSV的两项核心技术:深硅刻蚀和电镀都出现了。

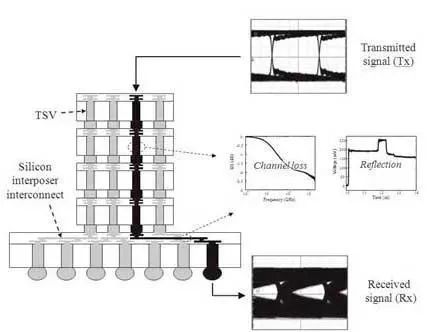

TSV不仅赋予了芯片纵向维度的集成能力,而且它具有最短的电传输路径以及优异的抗干扰性能。随着摩尔定律慢慢走到尽头,半导体器件的微型化也越来越依赖于集成TSV的先进封装。TSV对于像CMOS Image Sensor(CIS,CMOS图像传感器),High Bandwidth Memory(HBM)以及Silicon interposer(硅转接板)都极其重要。因为存在感光面的缘故,CIS芯片的电信号必须从背部引出,TSV因此成为其必不可少的电互连结构。HBM是基于多层堆叠的存储芯片,如今HBM已经可以实现12层的堆叠,16层以上更多层的堆叠相信在不久的将来也会实现,当然这一切都离不开TSV的互连。而Silicon interposer可以将多种芯片,像CPU, memory, ASIC等集成到一个封装模块的关键组件,它的垂直互连同样需要TSV。事实上,法国的Yole development咨询公司曾做过一项研究发现TSV几乎可以应用于任何芯片的封装以及任何类型的先进封装,包括LED, MEMS等。 正是因为TSV的重要性,各大Foundry和OSTA公司也不断投入TSV技术的研发。这阶段的研发重点是如何保证电镀沉积主要发生在TSV孔内而不是硅片表面。如果不采取任何措施,电镀时硅表面金属沉积的速度会远快于TSV孔内。这个问题目前的解决方法是在电镀液中添加抑制剂和加速剂,分别抑制硅片表面的金属沉积并加速TSV孔内的沉积。为了获得完美的填充效果和足够高的良率,各大Foundry和OSTA公司都做了大量研究以获得最佳的电镀的参数,例如电流,温度,硅片的与电极的相对位置,添加剂的浓度等。各大半导体设备公司也开始针对TSV的电镀推出专用的半导体设备。

在硬件世界中,经常用与速度有关的术语来谈论它,即是否是内存的带宽,处理器的时钟周期,处理器每秒执行某种类型的计算的次数等等,但是我们很少问自己这些芯片如何相互通信以及这是否重要。

在本文中,我们将讨论一种称为TSV的技术,该技术可用于相互通信的芯片。

什么是硅或TSV通路?

如果我们看大多数主板,可以看到两件事:第一,芯片之间的大多数连接都是水平的,这意味着板上发送芯片间信号的路径是水平通信的。

然后是CPU的情况,这些CPU放置在我们称为插座的插入器的顶部,并且处理器在这些插入器上垂直连接。

但是通常,在99%的时间中,我们观察到通常没有相互垂直连接的芯片,尽管事实上芯片和处理器的设计朝着这个方向发展,并且市场上已经有这种类型的示例。但是,如何使两个或更多芯片垂直互连?

TSV

好吧,正是通过所谓的硅通道来完成的,硅通道垂直穿过组成堆栈的同一芯片的不同芯片或不同层,这就是为什么它们被称为“通过”硅通道,因为它们实际上是通过的。

使用TSV的应用和优势

TSV的应用之一是,它允许将由不同部分组成的复杂处理器分离在几个不同的芯片上,并具有以下附加优点:垂直连接允许更多数量的连接,这有助于实现更大的带宽,而无需额外的带宽。很高的时钟频率会增加数据传输期间的功耗。

例如,在将来,我们将看到CPU和GPU的最后一级缓存将不在芯片上,它们具有相同的带宽,但存储容量却是原来的几倍,这将大大提高性能。我们也有使用FSV来通信Lakefield SoC的两个部分的Intel Foveros示例,即带有系统I / O所在的基本芯片的计算芯片。

将处理器划分为不同部分的原因是,随着芯片的变大,电路中错误的可能性越来越大,因此没有故障的优质芯片的数量会增加。他们可以使用的更少,而那些做得好的人必须支付失败者的费用;这意味着从理论上减小芯片的尺寸会降低总体成本,尽管稍后我们将看到情况并非完全如此。

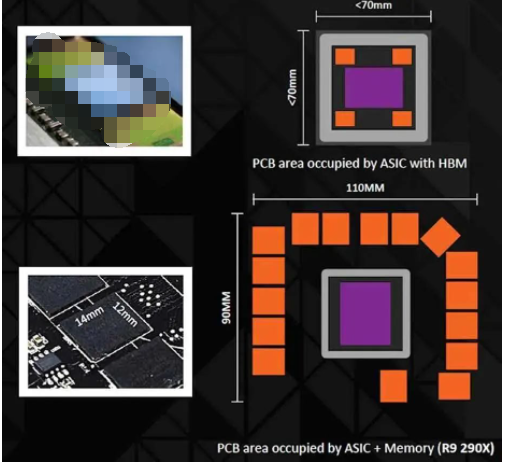

HBM-vs-GDDR

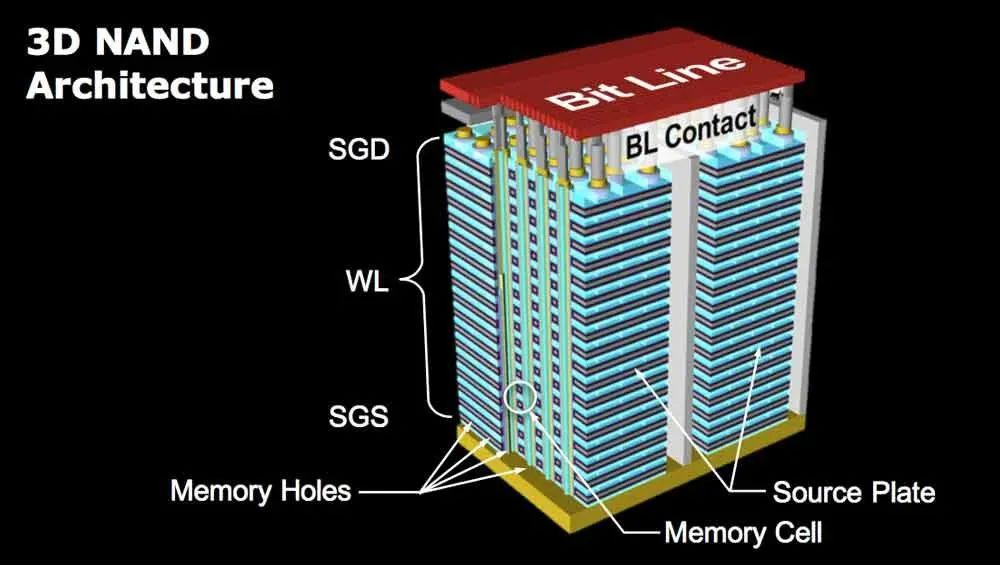

第二个应用程序与占用的空间有关;能够垂直堆叠多个芯片的事实大大减少了它们占用的面积,因为它们不会散布在板上,其中最著名的示例是将HBM内存用作某些图形处理器的VRAM,但是我们还有其他示例,例如三星的V-NAND存储器,将多个NAND闪存芯片彼此堆叠。

3DNAND

其他鲜为人知的选择是逻辑和内存的组合,其中内存位于处理器的顶部,最著名的示例是宽I / O内存,这是几年前出现在智能手机中的一种内存,包括SoC顶部的存储器通过硅互连。

2022年3月9号,苹果公司推出的M1 ULTRA处理器,这款性能爆表的处理器中,多个CPU使用带TSV的Silicon interposer进行集成的。如今,无论是AI/AR/VR中用到的传感器,图像传感器,堆叠存储芯片以及高性能处理器,都越来越离不开TSV。 TSV, 这项并不为人熟知的技术,正在硬件的底层深深的影响着人类的生产生活方式。 半个多世纪前的那个秋天,肖特基那个在硅片上打孔的想法最终将人类带入了人工智能的时代。

编辑:黄飞

-

TSV制造工艺概述2025-10-13 4217

-

TSV和TGV产品在切割上的不同难点2025-10-11 1101

-

TSV工艺中的硅晶圆减薄与铜平坦化技术2025-08-12 2095

-

先进封装中的TSV/硅通孔技术介绍2024-12-17 4357

-

3D-IC 中 硅通孔TSV 的设计与制造2023-11-30 2611

-

硅通孔TSV-Through-Silicon Via2023-07-03 5722

-

TSV工艺流程与电学特性研究2022-06-16 4264

-

硅通孔(TSV)电镀2021-01-09 3837

-

请问有TSV6390AIDT和/或TSV6290AIDT的SPICE型号吗?2019-08-06 2143

-

什么是TSV封装?TSV封装有哪些应用领域?2018-08-14 93029

-

通用输入/输出轨到轨低功耗操作放大器TSV321/TSV358/TSV324/TSV321A/TSV358A/TSV324A2017-09-05 1257

-

详解TSV(硅通孔技术)封装技术2016-10-12 18432

-

中微推出用于3D芯片及封装的硅通孔刻蚀设备Primo TSV200E(TM)2012-03-15 1845

全部0条评论

快来发表一下你的评论吧 !