CoWoS先进封装技术介绍 CoWoS-R技术主要特点分析

制造/封装

描述

随着摩尔定律放缓,芯片特征尺寸接近物理极限,先进封装成为提升芯片性能,延续摩尔定律的重要手段。先进封装是指处于前沿的封装形式和技术,通过优化连接、在同一个封装内集成不同材料、线宽的半导体集成电路和器件等方式,提升集成电路的连接密度和集成度。

CoWoS是什么?

1 后摩尔时代,先进封装成为提升芯片性能重要解法1.1 摩尔定律放缓,先进封装日益成为提升芯片性能重要手段1.2 先进封装份额占比提升,2.5D/3D 封装增速领先先进封装1.3 先进封装处于晶圆制造与封测的交叉区域2 CoWoS:台积电的 2.5D 先进封装技术2.1 CoWoS-S:最经典的 CoWoS 技术,以硅基板作为中介层2.2 CoWoS-R:使用 RDL 替代硅作为中介层 2.3 CoWoS-L:使用小芯片和 RDL 作为中介层,融合 CoWoS-S 和 InFO 技术优点 3 超越摩尔(MtM)提速,制造设备为关键3.1 光刻设备是超越摩尔的支柱,键合设备推动先进封装3.2 MtM 设备(W2W 永久键合、光刻、临时键合和解键合设备)相关工艺与流程 3.3 MtM 设备市场规模 3.4 MtM 设备厂商

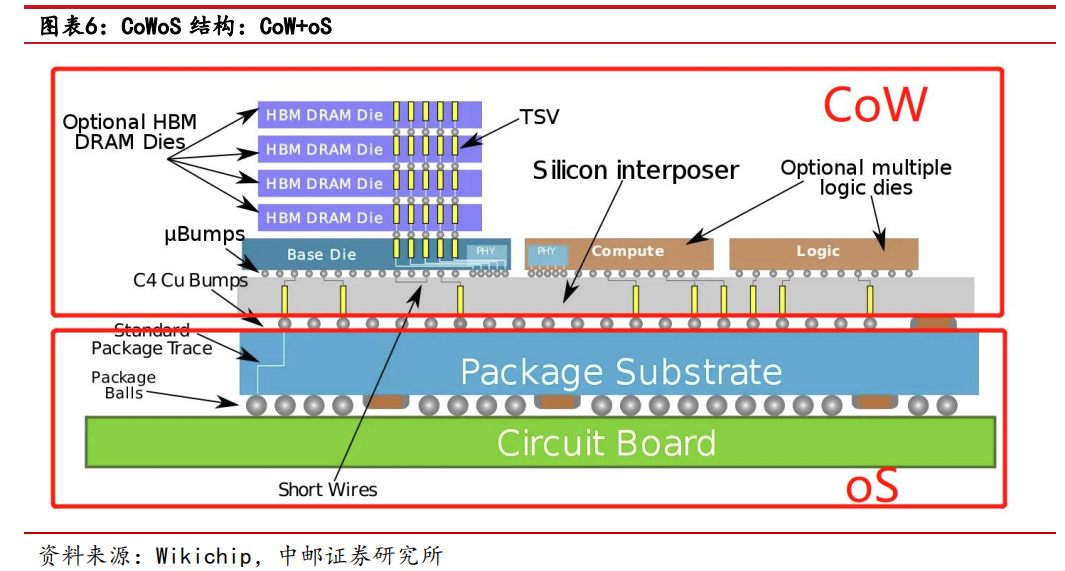

本文来自“CoWoS(Chip On Wafer On Substrate)是台积电的一种 2.5D 先进封装技术,由 CoW 和 oS 组合而来:先将芯片通过 Chip on Wafer(CoW)的封装制程连接至硅晶圆,再把 CoW 芯片与基板(Substrate)连接,整合成 CoWoS。核心是将不同的芯片堆叠在同一片硅中介层实现多颗芯片互联。在硅中介层中,台积电使用微凸块(μBmps)、硅通孔(TSV)等技术,代替了传统引线键合用于裸片间连接,大大提高了互联密度以及数据传输带宽。CoWoS 技术能够提高系统性能、降低功耗、缩小封装尺寸,也为台积电在后续的封装技术保持领先奠定了基础。

根据采用的不同的中介层(interposer),台积电把 CoWoS 封装技术分为三种类型——CoWoS-S(Silicon Interposer)、CoWoS-R(RDL Interposer)以及CoWoS-L(Local Silicon Interconnect and RDL Interposer)。

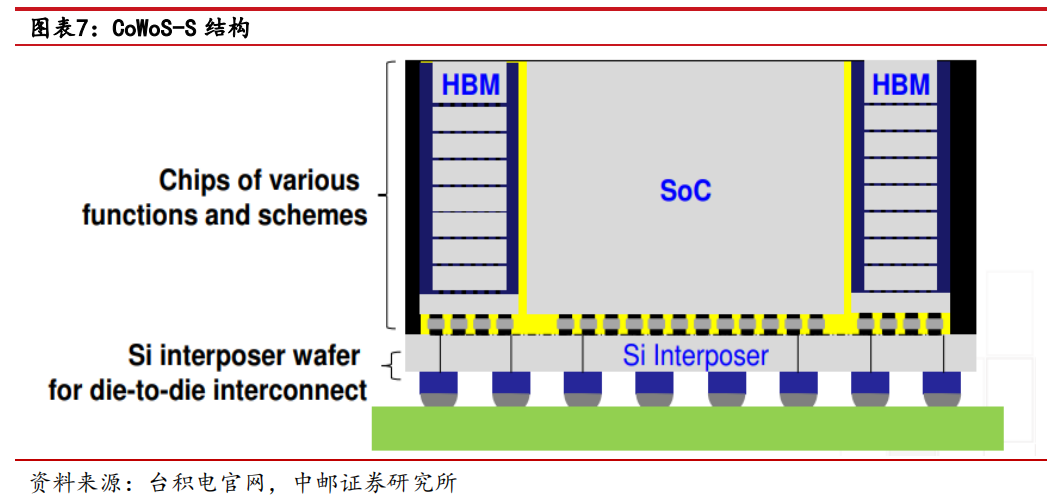

1、CoWoS-S:最经典的 CoWoS 技术,以硅基板作为中介层 CoWoS-S(Silicon Interposer)即 2011 年首次亮相的用硅(Si)衬底作为中 介 层 的 先 进 封 装 技 术 ,提供广泛的中介层尺寸、HBM 立方体数量和封装尺寸,可以实现大于 2X 的光罩尺寸(1,700mm2),中介层集成了领先的 SoC 芯片和四个以上的HBM2/HBM2E 立方体。在过去,“CoWoS”一般即指以硅基板作为中介层的先进封装技术。

CoWoS-S 从 2011 年的第一代升级到 2021 年的第五代,第六代技术有望于2023 年推出,将会在基板上封装 2 颗运算核心,同时可以板载多达 12 颗 HBM 缓存芯片。第五代 CoWoS-S 技术使用了全新的 TSV 解决方案,更厚的铜连接线,晶体管数量是第 3 代的 20 倍。它的硅中介层扩大到 2500mm2,相当于 3 倍光罩面积,拥有 8 个 HBM2E 堆栈的空间,容量高达 128 GB。并且,台积电以 Metal Tim形式提供最新高性能处理器散热解决方案,与第一代 Gel TIM 相比,封装热阻降低至 0.15 倍。

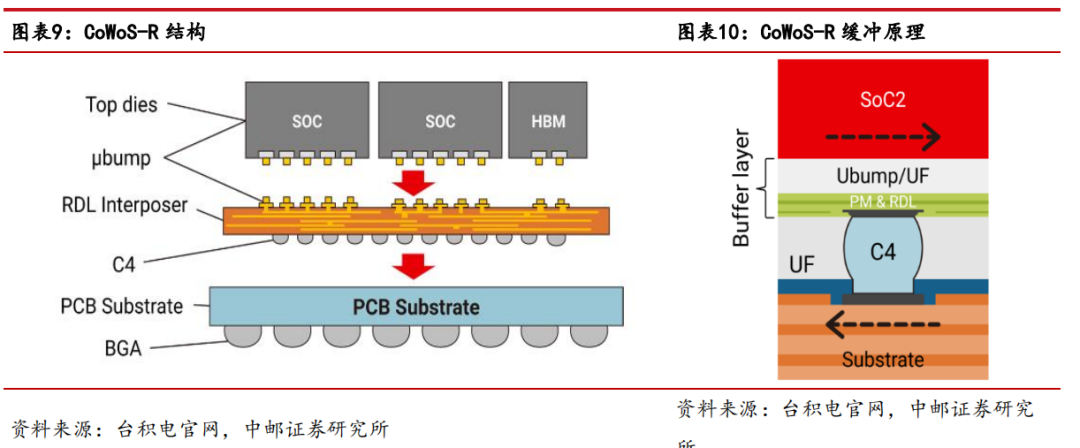

2、CoWoS-R:使用 RDL 替代硅作为中介层 CoWoS-R(RDL Interposer)是使用有机基板/重新布线层(RDL)替代了硅(Si)作为中介层的先进封装技术。CoWoS-R 采用 InFO 技术使用 RDL 作为中介层并为 chiplets 之间的互连提供服务,特别是在 HBM(高带宽存储器)和 SoC 异构集成中。RDL 中介层由聚合物和铜走线组成,机械灵活性相对较高,这种灵活性增强了 C4 接头的完整性,并允许新封装可以扩大其尺寸以满足更复杂的功能需求。

CoWoS-R 技术的主要特点包括: 1)RDL interposer 由多达 6L 铜层组成,用于最小间距为 4um 间距(2um 线宽/间距)的布线。 2)RDL 互连提供良好的信号和电源完整性性能,路由线路的 RC 值较低,可实现高传输数据速率。共面 GSGSG 和具有六个 RDL 互连的层间接地屏蔽可提供卓越的电气性能。 3)RDL 层和 C4/UF 层由于 SoC 与相应衬底之间的 CTE 不匹配而提供了良好的缓冲效果。C4 凸块的应变能密度大大降低

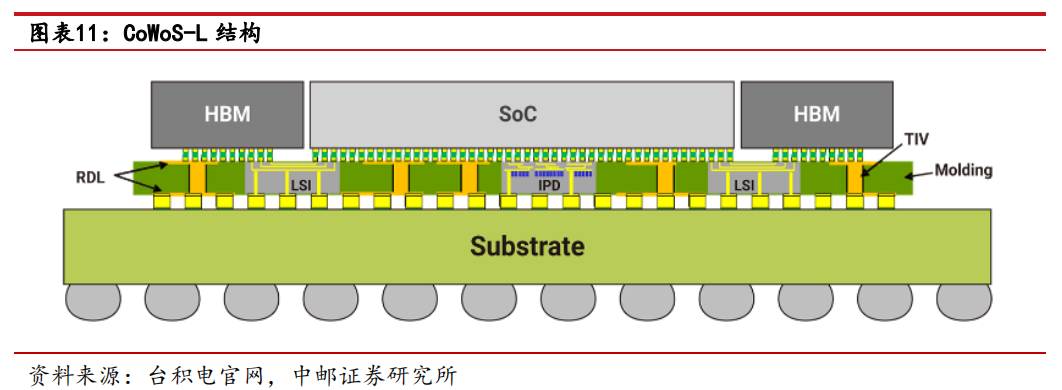

3、CoWoS-L:使用小芯片和 RDL 作为中介层,融合 CoWoS-S 和 InFO技术优点 CoWoS-L(Local Silicon Interconnect and RDL Interposer)是使用小芯片(chiplet)和 RDL 作为中介层(硅桥)的先进封装技术,结合了 CoWoS-S 和InFO 技术的优点,具有灵活的集成性。CoWoS-L 使用内插器与 LSI(本地硅互连)芯片进行芯片间互连,以及用于电源和信号传输的 RDL 层,从 1.5 倍 reticleinterposer 尺寸和 1 倍 SoC+4 倍 HBM 立方体开始,并将向前扩展,将包络扩大到更大的尺寸,以集成更多芯片。

CoWoS-L 服务的主要功能包括: 1)LSI 芯片,用于通过多层亚微米铜线实现高布线密度晶粒互连。LSI 芯片可以在每个产品中具有多种连接架构(例如 SoC 到 SoC、SoC 到 chiplet、SoC 到HBM 等),也可以重复用于多个产品。相应的金属类型、层数和间距与 CoWoS-S 的产品一致。 2)基于成型的中介层,正面和背面具有宽间距的 RDL 层,TIV(通过中介层通孔)用于信号和功率传输,可在高速传输中提供低高频信号损失。

编辑:黄飞

-

先进封装市场迎来EMIB与CoWoS的格局之争2025-12-16 2547

-

台积电CoWoS技术的基本原理2025-11-11 3993

-

HBM技术在CowoS封装中的应用2025-09-22 2700

-

日月光扩大CoWoS先进封装产能2025-02-08 1639

-

先进封装行业:CoWoS五问五答2025-01-14 7206

-

CoWoS先进封装技术介绍2024-12-17 6157

-

什么是CoWoS封装技术?2024-08-08 10850

-

什么是 CoWoS 封装技术?2024-06-05 2306

-

CoWoS封装在Chiplet中的信号及电源完整性介绍2024-04-20 3196

-

CoWoS先进封装是什么?2023-07-31 6090

-

CoWoS和HBM的供应链分析2023-07-30 4383

-

全面详解CoWoS封装技术特点及优势2023-07-11 12789

-

如何区分Info与CoWoS封装?2023-06-20 5161

-

台积电3D Fabric先进封装技术详解2022-07-05 4230

全部0条评论

快来发表一下你的评论吧 !