Verilog设计寄存器

Verilog设计寄存器

描述

现代逻辑设计中,时序逻辑设计是核心,而寄存器又是时序逻辑的基础,下面将介绍几种常见的寄存器的Verilog设计代码供初学者进行学习理解。

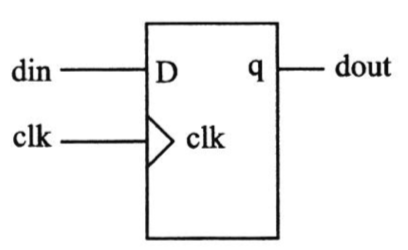

1、简单寄存器

基本寄存器

module dff(clk, din, dout)

input clk;

input din;

output dout;

reg dout;

always @ (posedge clk)begin

dout <= din;

end

endmodule

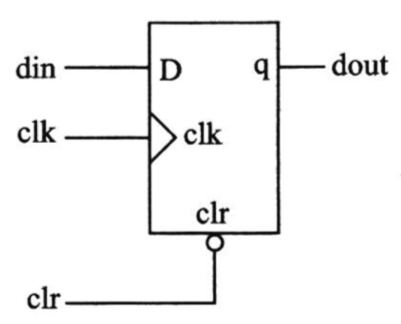

2、异步复位寄存器

异步复位寄存器

module dff(clk, rst_n, din, dout);

input clk;

input rst_n;

input din;

output dout;

reg dout;

always @ (posedge clk or negedge rst_n)begin

if(! rst_n)dout <= 1'b0;

else dout <= din;

end

endmodule

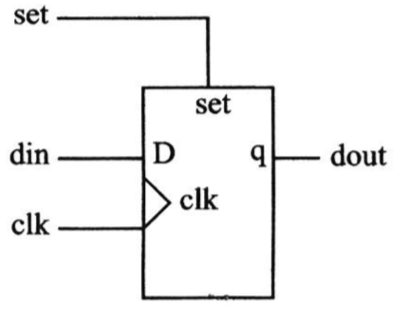

3、带异步置位的寄存器

异步置位寄存器

module dff(clk, set, din, dout);

input clk;

input din;

input set;

output dout;

reg dout;

always @ (posedge clk or posedge set)begin

if(set) dout <= 1'b1;

else dout <= din;

end

endmodule

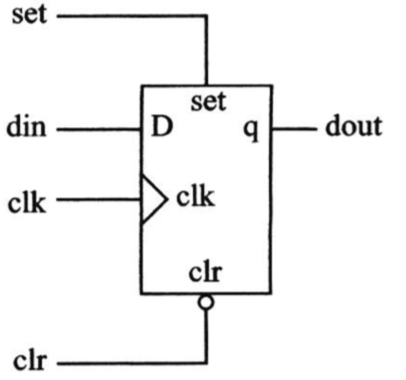

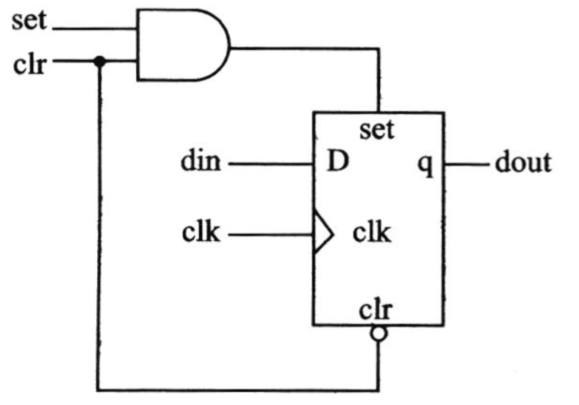

4、既带异步复位又带异步置位的寄存器

异步复位和置位寄存器

异步复位和置位寄存器(复位优先级高)

module dff(clk, rst_n, set, din, dout);

input clk;

input din;

input rst_n;

input set;

output dout;

reg dout;

always @ (posedge clk or negedge rst_n posedge set)begin

if(! rst_n) dout <= 1'b0;

else if(set) dout <= 1'b1;

else dout <= din;

end

endmodule

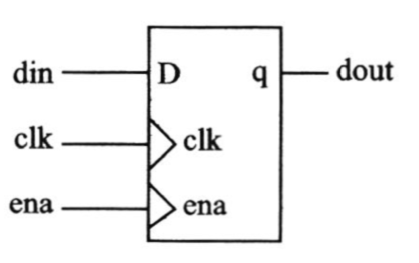

5、同步使能功能的寄存器

带同步使能的寄存器

module dff(clk, ena, din, dout);

input clk;

input din;

input ena;

output dout;

reg dout;

always @ (posedge clk) begin

if(ena) dout <= din;

end

endmodule

审核编辑:汤梓红

-

寄存器分为基本寄存器和什么两种2024-07-12 3278

-

寄存器是什么?怎么操作寄存器点亮LED灯?2023-07-21 5493

-

单片机工作寄存器作用 单片机常用专用寄存器2023-04-08 10044

-

ARM通用寄存器及状态寄存器详解2023-01-06 10005

-

AD转换寄存器设置2020-11-10 1244

-

移位寄存器的原理2019-07-15 77577

-

寄存器变量2019-06-03 3018

-

Verilog寄存器初始化没有复位引脚2019-05-16 2777

-

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途2017-12-22 21301

-

Verilog中寄存器的定义2017-01-18 15793

-

寄存器与移位寄存器2010-03-12 988

-

寄存器,寄存器是什么意思2010-03-08 22423

全部0条评论

快来发表一下你的评论吧 !