spinalhdl转Verilog可读性 SpinalHDL开发流程

描述

SpinalHDL是基于Scala全新的硬件描述语言,解决了不少Verilog等传统HDL语言的痛点,可以快速的完成某些IP的开发,和完美的融入现有的开发流程。

诚然SpinalHDL的学习路线是比较陡峭的。另外在团队协作中,你可以要求你的同伴对Verilog,VHDL语言进行掌握,但是不能要求他们也掌握SpinalHDL,Chisel这些语言,所以你的代码怎么安排别人接手也是一个问题。但是这并不妨碍我们采用SpinalHDL来快速验证我们某个想法是否是合理的,快速验证某个架构是否合理。

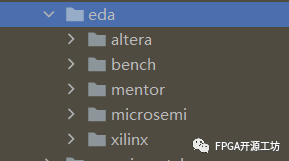

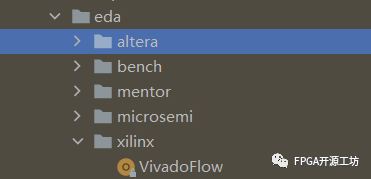

在SpinalHDL的lib里面有一个eda目录,里面有Xilinx,Altera等公司的一套工具库。

我们以Xilinx的为例来说明怎么利用里面的工具库来验证我们的代码能够跑的频率和占用的资源。

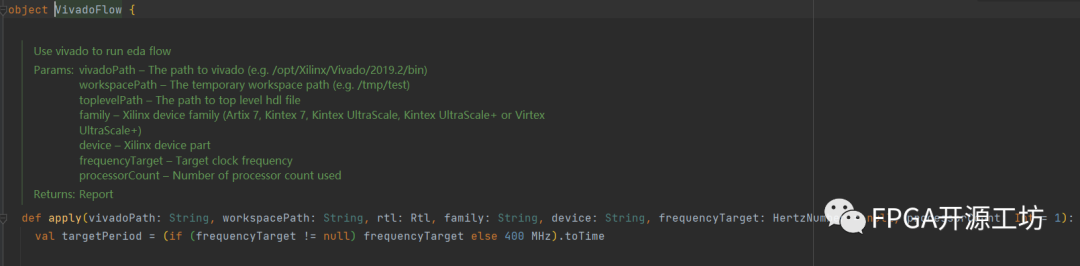

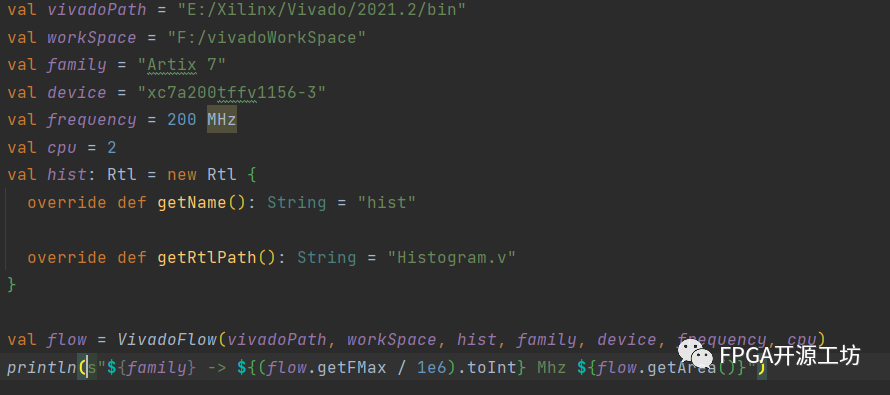

可以看到里面只有一个VivadoFlow的文件,在VivadoFlow里面需要我们指定Vivado的路径,工作目录,以及RTL,目标器件,频率等一系列参数

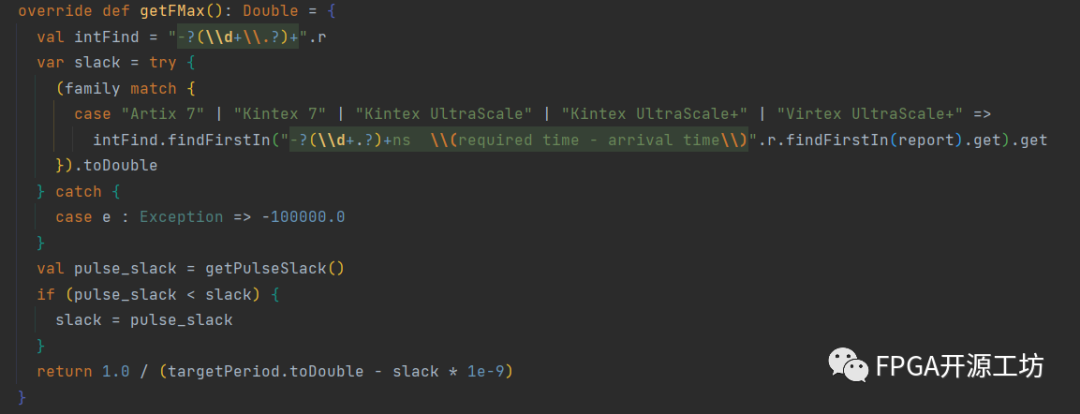

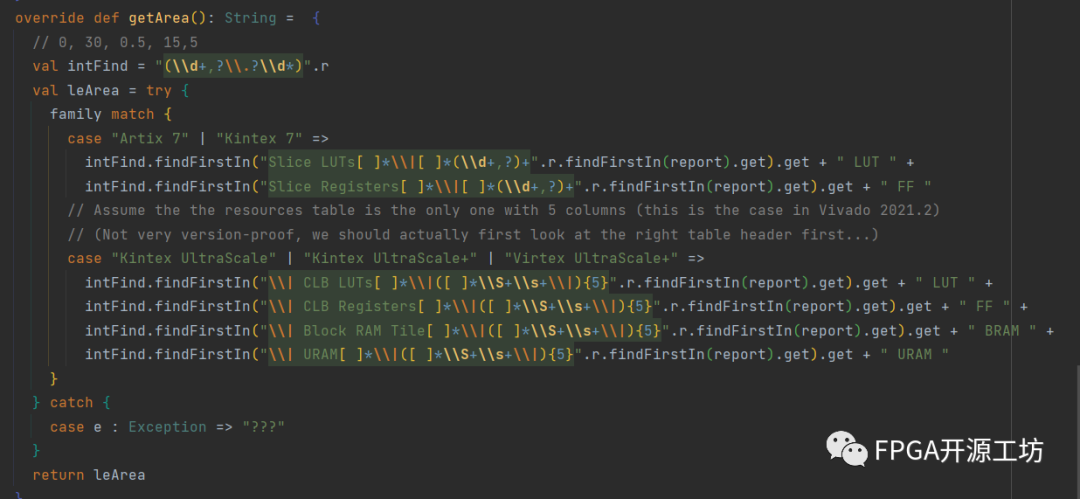

之后便可以获取到当前RTL能够跑到的最大频率和所需的资源了。可以看到A7和K7返回的是利用的LUT和FF,而KU,VU等器件把BRAM和URAM的资源利用也得到了。

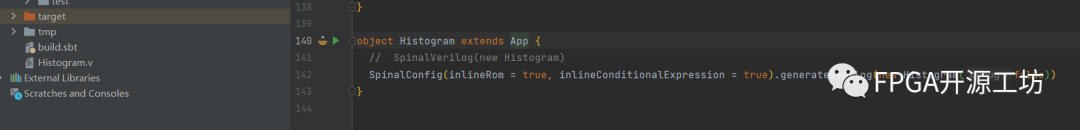

通过一个直方图均衡化的例子来说明这个VivadoFlow如何评估资源的消耗。

通过上面的代码指明vivado的路径,工作路径,以及目标器件和频率就可以愉快的开始等着频率和资源的利用报告了。

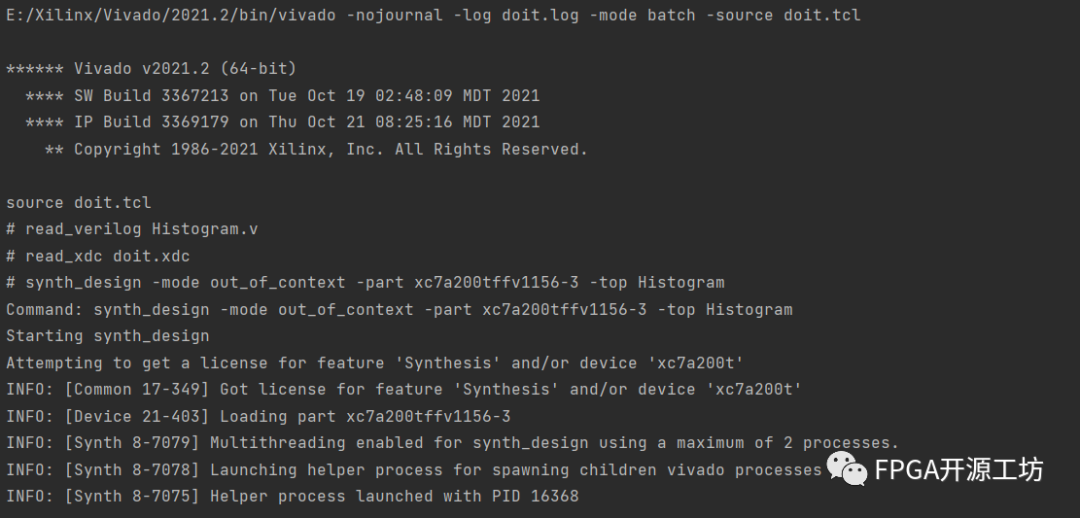

可以看到IDEA的窗口已经开始打印相关的log了。

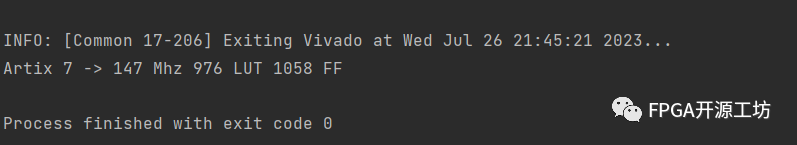

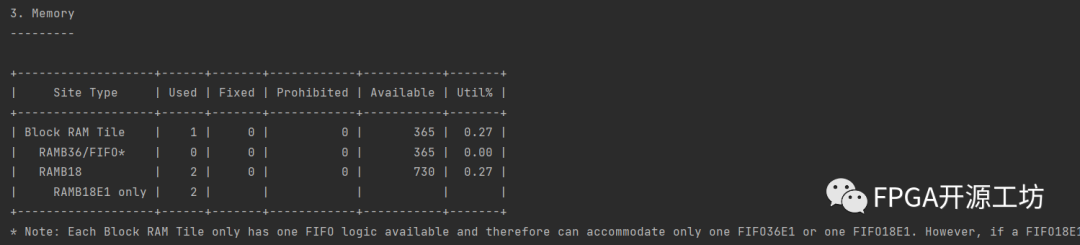

可以看到实际能够跑到的频率只有147M,资源利用了976个LUT,1058个FF,因为选了A7的器件,所以BRAM的利用并没有输出。但是可以在中间日志中看到。

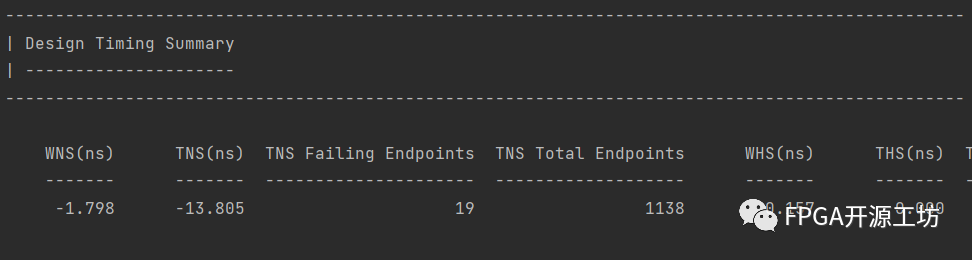

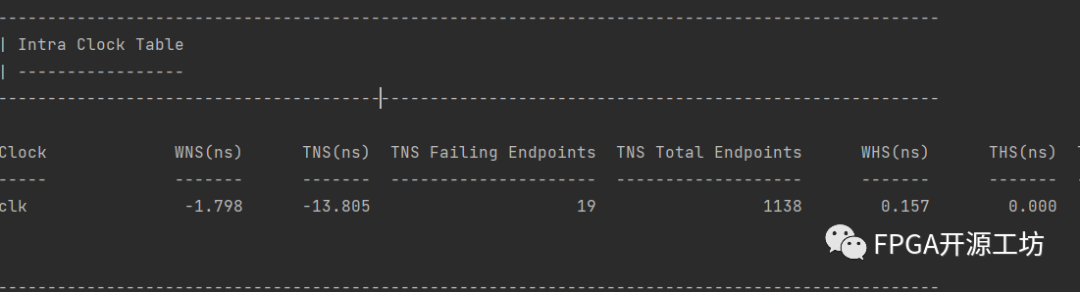

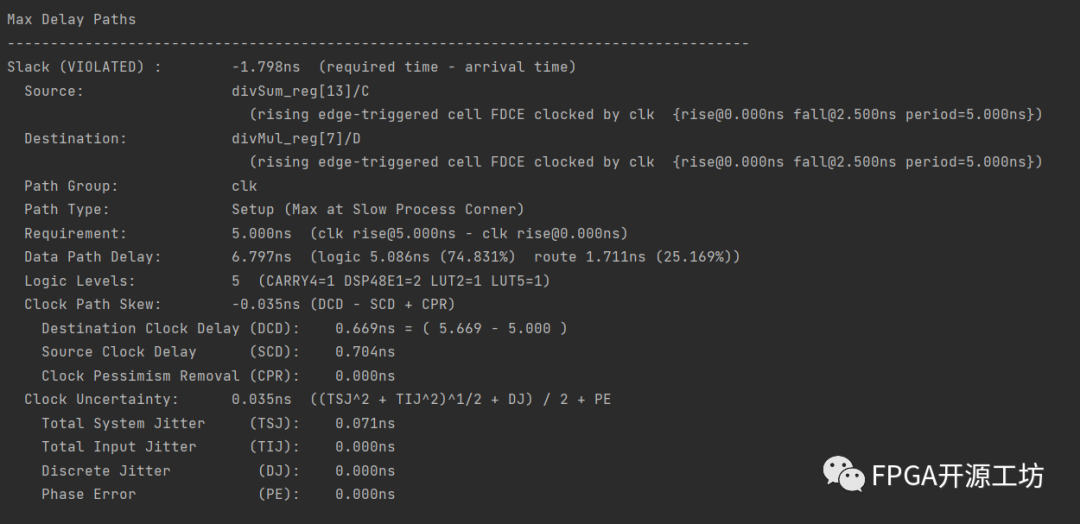

我们在之前设置的目标频率是200MHz,但是经过评估之后只能跑到147M,说明我们还需要优化下现在的代码,继续查看日志,可以看到建立时间不满足。具体不满足的地方在日志中也有输出。

Intra 说明是同一时钟下的,不存在跨时钟的问题,当然这个在我们设计的时候已经确定了。

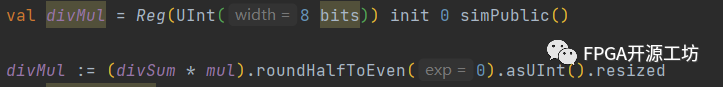

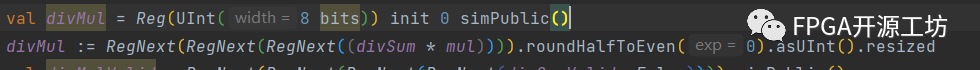

通过上面的日志可以确定是divSum和divMul之间的时序不满足。这一部分是一个乘法和截尾操作。乘法被映射到DSP上,我们知道xilinx的DSP内部有几级的寄存器,如果把这几级寄存器给利用起来那么就可以提高时钟频率,所以可以通过打拍的方式,让这几个寄存器被DSP所吸收掉,从而达到时序收敛的目的。(PS:如果是异步复位的寄存器是不能被7系列的FPGA的DSP所吸收的)

所以两种不同的代码如上。

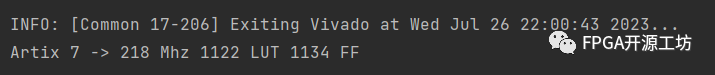

经过评估后可以跑到218MHz,的确有性能上的提升。

这个只是一个很小的模块,可以这样很快完成设计上的探索。

当我们要进行不同实现方式的探索的时候,便可以这样快速的完成,不断的完善模块的架构。

责任编辑:彭菁

-

SpinalHDL Simulation性能提升测试2023-08-06 1936

-

SpinalHDL BlackBox时钟与复位2023-05-04 1582

-

SpinalHDL设计错误总结相关资料分享2022-10-24 2482

-

SpinalHDL开发环境搭建步骤相关资料分享2022-10-17 2522

-

SpinalHDL里如何实现Sobel边缘检测2022-08-26 2070

-

如何在SpinalHDL里启动一个仿真2022-07-26 4047

-

SpinalHDL是如何让仿真跑起来的2022-07-25 2627

-

在SpinalHDL中的代码组织结构如何实现Component参数化设计呢2022-07-21 2552

-

在SpinalHDL中关于casez的使用2022-07-06 4627

-

在SpinalHDL中的对应关系及声明形式2022-07-03 2546

-

聊一聊SpinalHDL 1.6.1引入的blackbox inline功能2022-06-29 1847

-

在SpinalHDL里实现优雅的添加待跟踪波形信号2022-06-22 1669

-

从Verilog到SpinalHDL2021-12-20 406

-

如何实现SpinalHDL 环境搭建2021-08-24 9677

全部0条评论

快来发表一下你的评论吧 !