数字电路设计中的一款强大工具—Verilog编程语言介绍

嵌入式技术

描述

01

功能和特点

Verilog是一种硬件描述语言,用于描述数字电路的结构和行为。与传统的编程语言不同,Verilog更加注重电路的行为和时序特性。它能够精确地描述数字电路中的逻辑功能、寄存器、组合逻辑等元素,并且可以模拟电路在不同输入下的输出结果。

Verilog特点

·硬件级描述:Verilog可以直接描述数字电路的结构和行为,而不需要过多的关注底层硬件细节。这使得设计者能够更加专注于电路功能和性能的实现。

高层抽象:Verilog提供了高层抽象的能力,可以使用模块化的方式组织电路设计。这样可以方便地复用已有的模块,提高设计效率。

仿真支持:Verilog可以通过仿真工具进行功能验证和时序分析,帮助设计者发现和解决潜在的问题。仿真还可以用于验证设计在不同输入情况下的正确性。

综合与实现:Verilog可以通过综合工具将代码转化为实际的硬件电路,然后进行布局布线和实际物理设计。这使得设计者能够更好地了解设计的资源占用和时序约束。

ONE

下面介绍Verilog的一些基础知识:

02

模块描述

Ⅰ模块定义

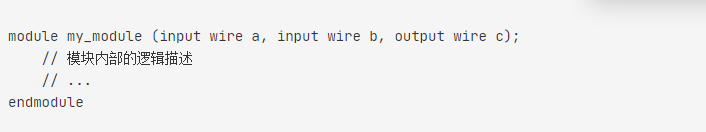

Verilog程序由一个或多个模块组成。模块是Verilog中的最基本单位,用于描述特定的电路功能。以下是一个简单的模块定义的示例:

在上面的示例中,我们定义了一个名为my_module的模块,它有两个输入(a和b)和一个输出(c);

注意事项:每个模块应单独处于一个.v文件中,模块名即为文件名(规范代码!)

Ⅱ 模块输入输出信号

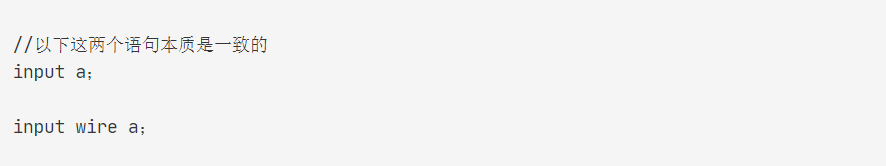

输入:input

输出:output

在上述模块中我们用到了input输入信号,通过模块的输入输出端口都可以看出模块的信号,若不写信号类型则默认为wire类型信号~

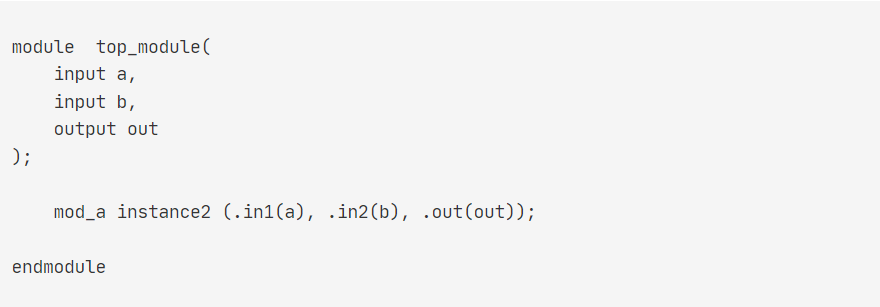

Ⅲ 模块实例化

如下图所示,top_module的两个输入端口连接到次级模块(mod_a)的输入端口,那如何在top_module模块模块中使用mod_a模块的功能呢?这就需要通过模块实例化,可以把top_module看成C语言中的主函数,次级模块mod_a看成普通函数,这样就可以在主函数中调用其他函数来完成相应的功能~

在top_module中实例化mod_a的方式为:

模块实例化语法:模块名 实例名(定义连接port的信号);

03

逻辑块(always、generate)

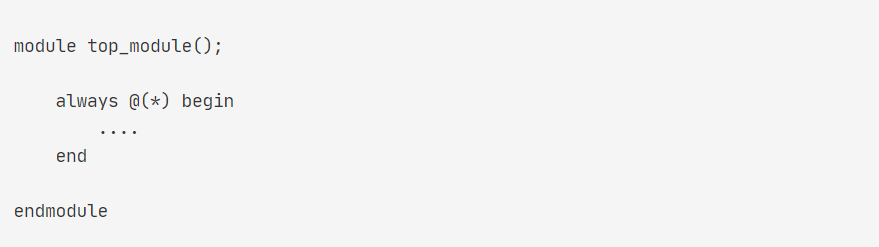

Ⅰalways逻辑块

always块可构建 组合逻辑块 和 时序逻辑块,复杂的逻辑操作都需要处于该逻辑块中,如if、case、for等;

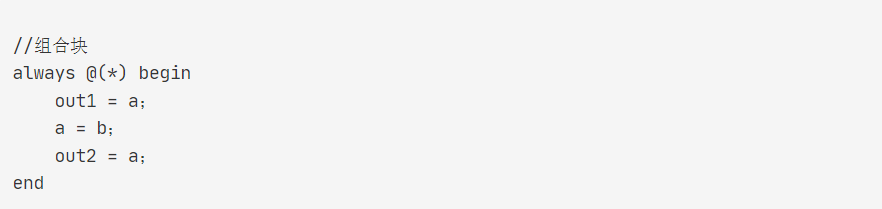

1、组合逻辑块

① always逻辑块中任意信号变化时立即触发,执行begin - end之间的语句;

② begin - end用于将多条语句组成一个代码块,只有一条语句时可省略;

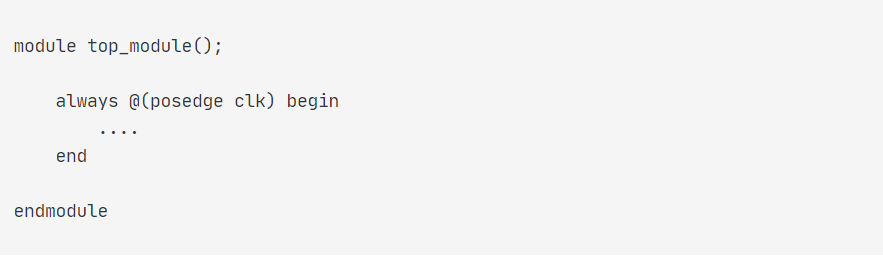

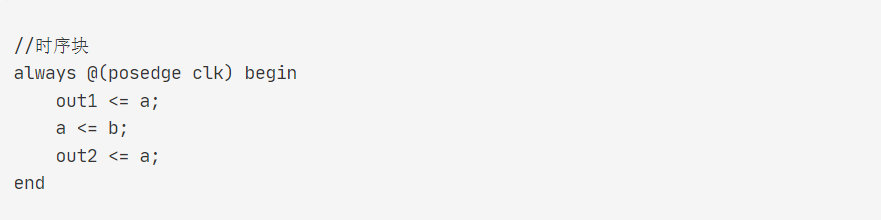

2、时序逻辑块

① clk 信号的上升沿触发;

② posedge: 上升沿;

③ negedge: 下降沿;

Ⅱ generate逻辑块

generate主要结合for循环使用,主要用途有:

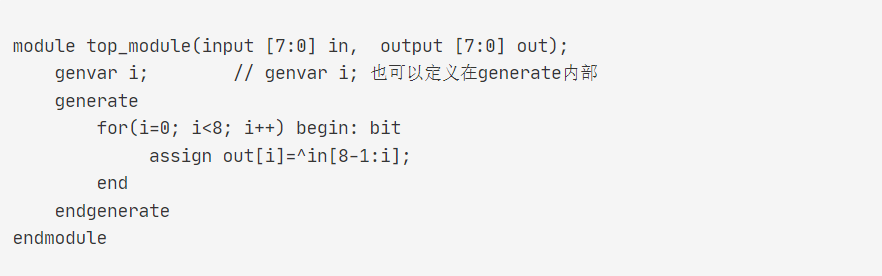

· 对向量中的多个位进行重复操作;

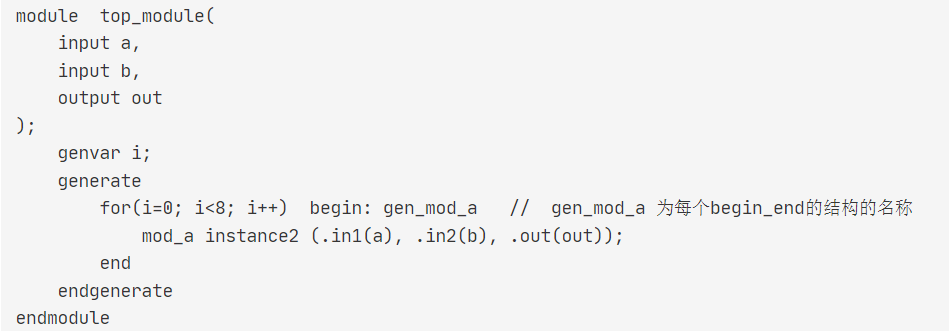

· 对同一个模块进行多次重复实例化(主要用途);

1、操作向量:

2、模块重复多次实例化:

注意:模块多次实例化时必须写每个begin_end结构的名称(gen_mod_a);

04

赋值方式

Verilog 中赋值方式有三种:连续赋值、阻塞赋值、非阻塞赋值;

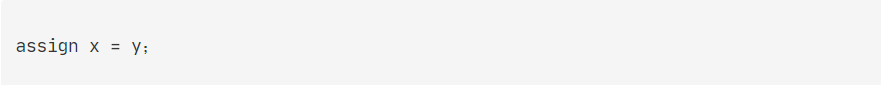

1、连续赋值(assign)

该语句表示把x和y两个信号进行连接,真实的物理连接!

不能在always块中使用;

2、阻塞赋值(=)

在组合always块中用阻塞式赋值;

执行顺序:按照begin_end语句块中的顺序依次执行,上述输出结果为:out1 = a ,out2 = b;

3、非阻塞赋值(<=)

① 时序always块中用非阻塞赋值;

② 执行顺序:begin_end中所有语句并行执行,上述输出结果为:out1 = a ,out2 = a;

05

一些小建议

Verilog编程语言广泛应用于数字电路设计、FPGA设计、芯片设计等领域。无论是从事硬件设计的工程师,还是对数字电路感兴趣的学生,都可以通过学习Verilog来提高自己的设计能力。

当然,学习Verilog并不是一蹴而就的过程。初学者可以通过阅读相关的教材和资料,进一步学习Verilog的内部原理和基础语法。此外,还可以结合实际的电路设计案例进行练习,逐步提高自己的编程能力。

总而言之,Verilog是一种强大的硬件描述语言,用于描述数字电路的结构和行为。它具有硬件级描述、高层抽象、仿真支持和综合与实现等特点,广泛应用于数字电路设计领域。如果你对数字电路设计感兴趣,那么Verilog是你需要掌握的必不可少的技能之一 ~

审核编辑:刘清

-

招聘:数字电路设计师2015-02-27 3564

-

数字电路设计与Verilog HDL2015-07-16 13842

-

分享一款不错的基于可编程逻辑器件PLD的数字电路设计方案2021-04-30 1929

-

基于LabVIEW的数字电路设计和仿真2010-03-30 1328

-

数字电路设计2009-08-26 3122

-

基于可编程逻辑器件的数字电路设计2009-11-16 1952

-

《VHDL与数字电路设计》2011-07-11 1457

-

数字电路中的FPGA和verilog教程2016-01-18 741

-

使用FPGA设计数字电路时的综合工具介绍2020-07-24 2483

-

Verilog数字系统设计——复杂数字电路设计2(FIFO控制器设计)2021-12-05 733

-

数字电路设计的基本流程2022-07-10 9915

-

verilog与其他编程语言的接口机制2024-02-23 1783

-

如何使用 Verilog 进行数字电路设计2024-12-17 2203

-

数字电路编程语言介绍2025-01-24 1915

-

数字电路设计中:前端与后端的差异解析2025-02-12 2207

全部0条评论

快来发表一下你的评论吧 !