SiC MOSFET的设计和制造

电子说

描述

首先,是一张制造测试完成了的SiC MOSFET的晶圆(wafer)。

芯片表面一般是如图二所示,由源极焊盘(Source pad),栅极焊盘(Gate Pad)和开尔文源极焊盘(Kelvin Source Pad)构成。有一些只有Gate pad,如上图的芯片就没有Kelvin source pad。

图二.芯片表面

在这里我们仔细观察芯片的周围有一个很窄的环形,它的作用主要是提升芯片的耐压,我们叫耐压环(Edge termination Ring),通常是JTE结构,其实一个芯片主要就是由三部分构成:Terminal Ring,Gate Pad,Kelvin Source Pad和开关单元(Active Cell)。芯片外围一圈是耐压环,Gate pad把栅极信号传递到每一个Cell上面,然后里面是上百万个Active Cell。

通常大家关注比较多的是Active Cell,因为芯片的开关和导通性能主要是和Active Cell有比较大的关系。在这里我们把芯片的layout还有各个部分的作用特点总结一下,这样方便大家对芯片有一个更好的认识。

耐压环

(Edge termination Ring)

环绕着芯片的开关单元,目前大多数采用JTE结构;

有效控制漏电流,提高SiC器件的可靠性和稳定性;

减小电场集中效应,提高SiC器件的击穿电压,SiC MOSFET的击穿电压和具体的每一个开关单元有关,同时和耐压环也有很大的关系;

防止离子迁移,JTE技术可以用于抑制移动离子的漂移,从而提高SiC MOSFET的可靠性和稳定性。

其实耐压环的最主要的作用就是提升芯片的耐压,SiC MOSFET的耐压和Active Cell有关系,但是芯片边缘的场强很大,及其容易导致边缘击穿,所以这就是JTE的作用所在。在一些高压的器件中,甚至JTE的面积会大于Active Cell的面积。

栅极焊盘,开尔文源极焊盘

(Gate Pad,Kelvin Source Pad )

栅极pad主要作用就一个,把栅极的信号传输到各个开关单元,同时提一下,安森美的芯片是集成了栅极电阻的,这样在模块封装上可以节省空间和一些成本。

开尔文源极主要是增加了开关速度,减小开关损耗。不过在做并联使用的时候,就需要特别的设计来使用它。

开关单元

(Active Cell )

电流导通和关闭的路径;

所有的单元是并联;

固定的单元特性下,单元的数量决定了整个芯片的导通电阻大小和短路电流能力;

目前主要分为平面和沟槽两种结构。

现在,我们已经对SiC MOSFET的表面layout有了认识,在SiC的芯片里Edge terminal和Active Cell是非常重要的两部分,安森美在JTE的设计上具有丰富的经验,在SiC MOSET上已经从M1发展到了M3,通过几代的技术迭代发展,JTE设计仿真和制造非常的成熟。我们来总结一下JTE的一些特点和一些设计考虑因素。

SiC JTE(结延伸区)是用于改善硅碳化物(SiC)功率器件电压阻断能力的结构。SiC JTE的设计对于实现所需的击穿电压并避免因器件边缘处高电场而导致的过早击穿至关重要。

以下是SiC JTE设计的一些关键考虑因素:

1. JTE区域的宽度和掺杂:JTE区域的宽度和掺杂浓度确定器件边缘处的电场分布。较宽和重掺JTE区域可以减少电场并提高击穿电压。

2. JTE的锥角和深度:JTE的锥角和深度影响电场分布和击穿电压。较小的锥角和较深的JTE可以减少电场并提高击穿电压。

3. 表面钝化:表面钝化层对于减少表面泄漏并提高击穿电压非常重要。需要特别为SiC JTE器件精心设计和优化钝化层。

4. 热设计:SiC JTE器件可以在比其Si对应物更高的温度下工作。但是,高温也可能降低器件性能和可靠性。因此,在SiC JTE设计过程中应考虑热设计,如散热和热应力。

总体而言,SiC JTE设计是一个复杂的过程,涉及各种设计参数之间的权衡。需要进行仔细的优化和仿真,以实现所需的器件性能和可靠性。

Active Cell开关单元 – SiC MOSFET的核心

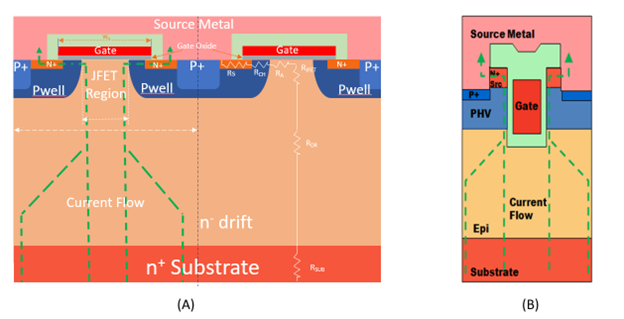

我们可以把MOSFET(硅和碳化硅)根据它们的栅极结构分成两类:平面结构和沟槽结构,它们的示意图如图三所示。如果从结构上来说,硅和碳化硅MOSFET是一样的,但是从制造工艺和设计上来说,由于碳化硅材料和硅材料的特性导致它们要考虑的点大部分都不太一样。比如SiC大量使用了干蚀刻(Dry etch),还有高温离子注入工艺,注入的元素也不一样。

图三.MOSFET的平面结构与沟槽结构

当前国际上的SiC MOSFET绝大部分都采用了图三A的平面结构,有少部分的厂家采用了图三B的沟槽结构。从发展的角度来看,最终都会衍生到沟槽结构。但是目前的平面结构的潜力还是可以继续深挖的,而沟槽结构也没有表现出它们应当有的水平,在这里我们引入一个统一的尺度来衡量它们的性能 - Rsp(Rdson * area),标识的是单位面积里的导通电阻大小。平面结构的SiC MOSFET具有可靠性高,设计加工简单的优点。

安森美SiC MOSFET器件优化了导通损耗、开通损耗、反向恢复损耗以及短路时间,使得它们在客户应用中达到最优化的一个效率。

SiC MOSFET的平面结构的Active Cell的设计制造方向主要是减小开关单元间距也就是pitch值,提升开关单元的密度,减小Rdson,提升栅极氧化层的可靠性。

如图三A中的结构为了尽可能的减小导通电阻,需要调整开关单元的间距,pitch值和Wg也就是栅极的宽度有一定的关系,pitch值变小,Wg也相应变小,这个对于栅极的可靠性是有一定好处的,在SiC MOSFET里,栅极氧化层(Gate Oxide)非常的薄,小于100纳米,因此在SiC的生产工艺中使用了干式蚀刻的方法来控制加工的精度。

根据图三A中的导通电阻示意图,我们可以得出Rdson = Rs + Rch + Ra + Rjfet + Rdrif + Rsub, 在这里面Rch和Ra占比最大,超过60%以上,所以它们变成了设计和工艺优化的一个重点方向之一。不过也不是一味的减小开关单元栅极的宽度就可以减小Rsp,栅极的Wg宽度减小到一定范围,反而会导致Rsp变大,在设计的时候需要综合考虑以上的参数相互之间的影响,这样才能获得一个比较理想的优化结果,安森美经过几代的工艺迭代发展,其平面结构的SiC MOSFET上已经在性能,良率、可靠性等方面发展得相对成熟。

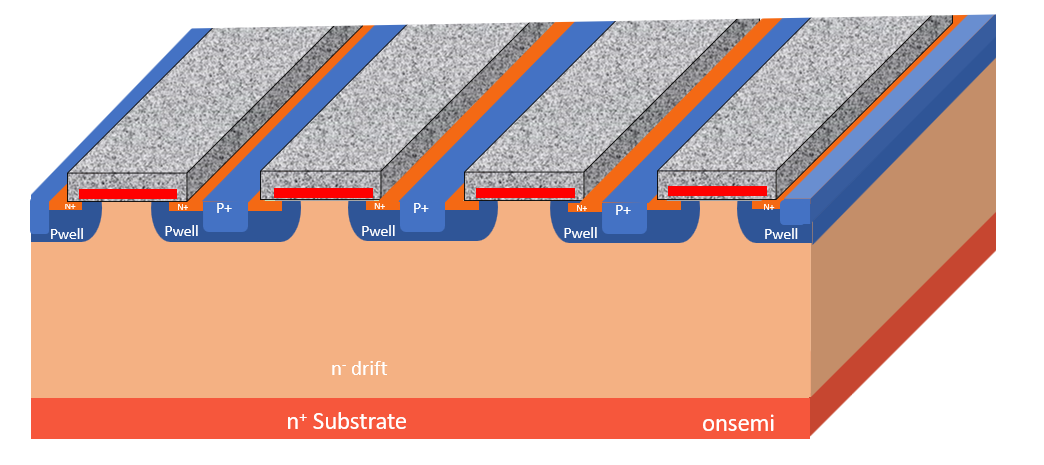

在芯片里,每个active cell是并联在一起的,图四是一个芯片的截面图的示意图,在这里采用的是带状结构的布局。从这里大家会对于芯片可以有更形象的了解。

图四.芯片的截面图

以下是SiC MOSFET Rdson设计的一些关键考虑因素:

1. 通道宽度和掺杂:SiC MOSFET的通道宽度和掺杂浓度会影响Rdson和电流密度。较宽和重掺的通道可以降低Rdson并提高电流承载能力。

2. 栅极氧化层厚度:栅极氧化层的厚度影响栅极电容,进而影响开关速度和Rdson。较薄的栅极氧化物可以提高开关速度,但也可能增加栅极漏电流,并增加氧化层击穿失效的风险。

3. 栅极设计:栅极设计影响栅极电阻,进而影响开关速度和Rdson。较低的栅极电阻可以提高开关速度,但也可能增加栅极电容。

总体而言,SiC MOSFET Rdson设计是一个复杂的过程,涉及综合考虑各个参数之间的相互影响。需要进行仔细的优化和仿真并且进行试验和测试,以实现所需的器件性能和可靠性。

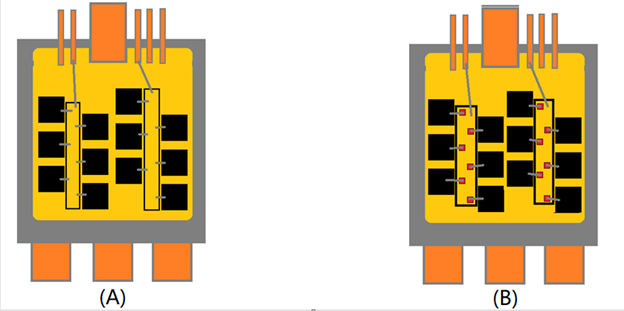

集成片上栅极电阻

安森美所有针对主驱逆变器开发的SiC MOSFET都集成了栅极的电阻,我们可以从图五看到有无电阻的区别。图五A是不需要栅极电阻(芯片上集成了),图五B是需要额外加一个栅极电阻。

图五.有无栅极电阻的区别

集成栅极电阻会给模块设计和制造带来一些好处:

简化了模块绑定线的工艺,降低了失效率。

减少了焊接电阻到DBC的工艺

降低了BOM和制造成本

便于封装的相对小型化设计和制造

SiC MOSFET的设计制造工艺非常复杂,本文对其流程与一些关键考虑因素进行了简要介绍,希望能让大家对SiC MOSFET的设计和制造有一个概念。

来源:半导体封装工程师之家

审核编辑:汤梓红

-

为何使用 SiC MOSFET2017-12-18 6042

-

SiC-MOSFET的应用实例2018-11-27 6069

-

SiC-MOSFET与Si-MOSFET的区别2018-11-30 11057

-

沟槽结构SiC-MOSFET与实际产品2018-12-05 4847

-

搭载SiC-MOSFET和SiC-SBD的功率模块2019-03-12 3435

-

罗姆成功实现SiC-SBD与SiC-MOSFET的一体化封装2019-03-18 3146

-

SiC-MOSFET有什么优点2019-04-09 4690

-

SiC功率器件SiC-MOSFET的特点2019-05-07 5701

-

SiC MOSFET:经济高效且可靠的高功率解决方案2019-07-30 4257

-

浅析SiC-MOSFET2019-09-17 6420

-

【罗姆SiC-MOSFET 试用体验连载】SiC MOSFET元器件性能研究2020-04-24 2156

-

SIC MOSFET2021-04-02 2664

-

SiC-MOSFET器件结构和特征2023-02-07 1574

-

SiC MOSFET的器件演变与技术优势2023-02-27 1552

-

车规级SiC MOSFET制造技术进展2023-11-07 1078

全部0条评论

快来发表一下你的评论吧 !