半导体行业制造工艺解析

描述

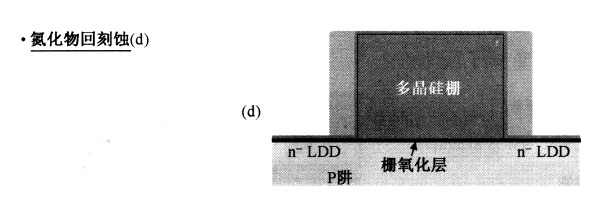

使用重离子可以形成源/漏扩展(SDE)浅结(见下图),通常PMOSSDE使用BF;,而NMOSSDE管使用Sb+重离子或As+。

对于侧壁间隔层的形成,经常使用氮化物和氧化物。如下图所示,CVD沉积的氧化物作为刻蚀停止层,LPCVD氮化物形成侧壁间隔层的主要部分。

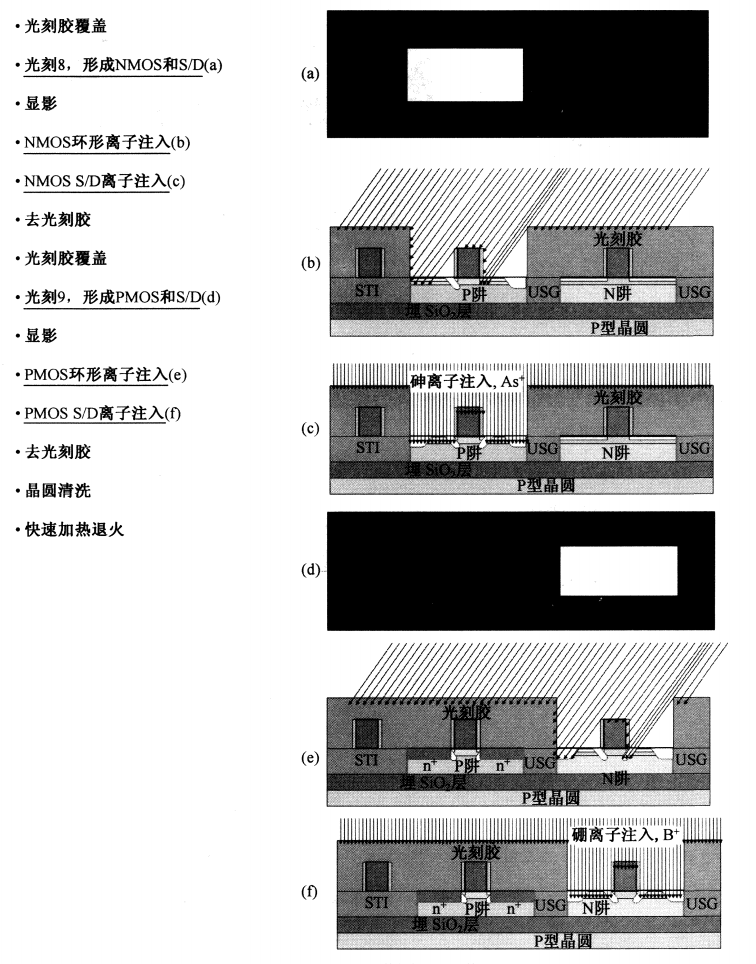

下图显示了CMOS形成的环形结和源/漏结。环形注入是一个大倾角离子注入过程,通常需要两次或四次注入过程,这取决于MOSFET处于一个方向还是两个方向。环形注入技术用于防止器件的串通。

为了获得低的电阻,钛硅化物的晶粒尺寸必须大于0.2um。当栅的宽度小于0.2um时,钛硅化物的应用将受到挑战。0.18um技术节点后,钴硅化物开始取代钛硅化物应用于栅极。由于钴与空气或湿气接触时,钴很容易被氧化形成氧化钴,所以使用氮化钛覆盖钴防止其与湿气接触。利用集成配套工具,钴和氮化钛采用不同的PVD反应室沉积。

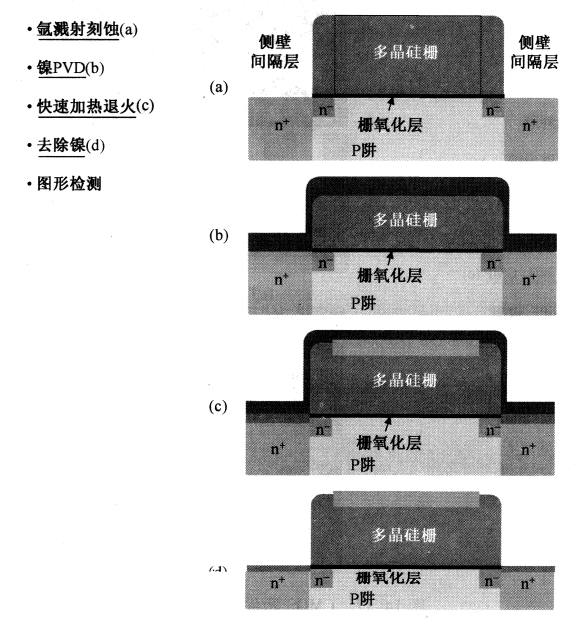

当器件尺寸进一步缩小到纳米技术节点时,CoSi2的退火温度(约750摄氏度)对于MOSFET微小的热积存已经太高。镍硅化合物(NiSi)可在温度低于500摄氏度下形成,所以被广泛用于65nm及更小的技术节点。

镍沉积前,需要氯溅射刻蚀去除硅表面原生氧化层,否则,由于接触电阻过高而导致IC芯片发生故障。由于NiSi热稳定性不高,镍容易与硅反应并穿通结面而引起漏电。在PVD靶材中,铂(Pt)合金化并在晶圆表面形成NiPtSi以获得更好的硅化物稳定性。可以使用电子束检查(EBI)系统监测镍扩散对成品率的影响。下图显示了硅化物形成工艺流程。

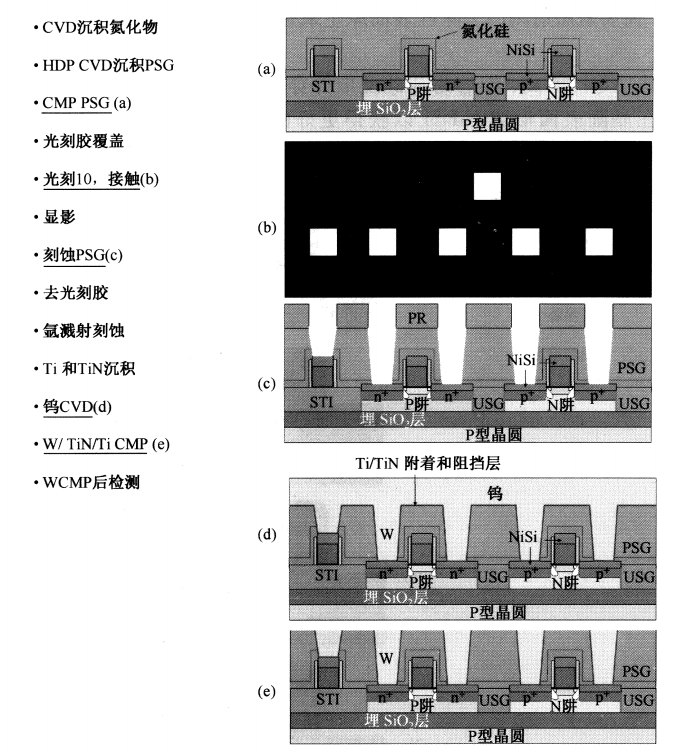

需要氮化物层防止磷从PSG中扩散到有源区。由于热积存的限制,利用PECVD氮化硅在较低温度(小于580摄氏度)下沉积取代LPCVD氮化物沉积(沉积温度为750摄氏度)。对于小尺寸器件(小于0.18um),PMD热再流动的热积存很小,因此硅酸盐玻璃中不再需要硼,PSG取代BPSG材料形成PMD。PSG利用CMP平坦化而不是热再流动。钙仅用于局部互连,以及源/漏、金属与硅化物之间的栓塞。钛和氮化钛作为阻挡层和钨附着层。

对于一些先进技术节点的CMOS工艺,USG用于ILD0,氮化物层用于应力缓冲层应变沟道,从而提高载流子的迁移率和MOSFET的性能。

接触非常关键,因为它将晶圆表面上的器件和各层的金属线互连。如果接触孔刻蚀不完全,金属导线将无法和器件相连,这将导致成品率下降。

PVD钛广泛用于减少接触电阻,氮化钛(TiN)作为镑附着层。如果没有TiN,钨薄膜将不会与硅晶圆表面很好地附着,这将导致裂纹并使钧薄膜从晶圆表面脱落,最后在晶圆上产生大量颗粒污染。TiN可以利用PVD和CVD沉积。当器件特征尺寸不断缩小时,接触孔的深宽比将变得很大,PVD工艺将不再提供足够的台阶覆盖,因此CVDTiN工艺更受欢迎。下图显示了CMOS器件接触示意图。

审核编辑:汤梓红

-

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测2025-04-15 1781

-

半导体行业工艺知识2024-12-07 2625

-

半导体制造工艺之光刻工艺详解2023-08-24 3356

-

《炬丰科技-半导体工艺》半导体行业的湿化学分析——总览2021-07-09 4932

-

《炬丰科技-半导体工艺》IC制造工艺2021-07-08 4739

-

MEMS工艺——半导体制造技术2021-04-08 4457

-

半导体制造的难点汇总2020-09-02 4920

-

半导体工艺2014-04-09 4036

-

半导体器件与工艺2012-08-20 45931

-

半导体制造2012-07-11 5178

-

半导体工艺讲座2009-11-18 97335

-

有关半导体工艺的问题2009-09-16 5842

-

标题:群“芯”闪耀的半导体行业2008-09-23 5559

全部0条评论

快来发表一下你的评论吧 !