信号时钟回沟分析设计

描述

|| 前言

作者一直觉得,善待和重视每个产品。产品简单,但是背后隐藏的东西却很多。量产近十年的产品,因为缺芯问题也不得不改版。尽管不想改,但是市场供应非常严峻。那既然这样,就正确一次到位,当然在市场面前发现一次到位几无可能。因为复杂系统,缺一种芯片和缺十种芯片最终是一样的,都无法有效生产出货。

改板出来,变化有点大了,改板的话也就没有改多少,cpu换了,电源全部换了,业务芯片全换了,增加了fpga,电源架构相比上板也基本全变了。除了产品大的架构,基本上和新产品一样。

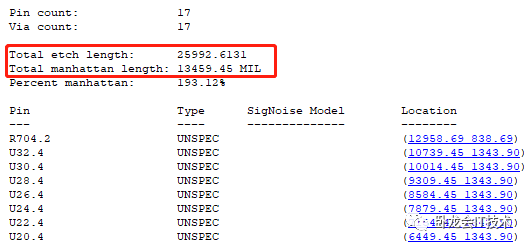

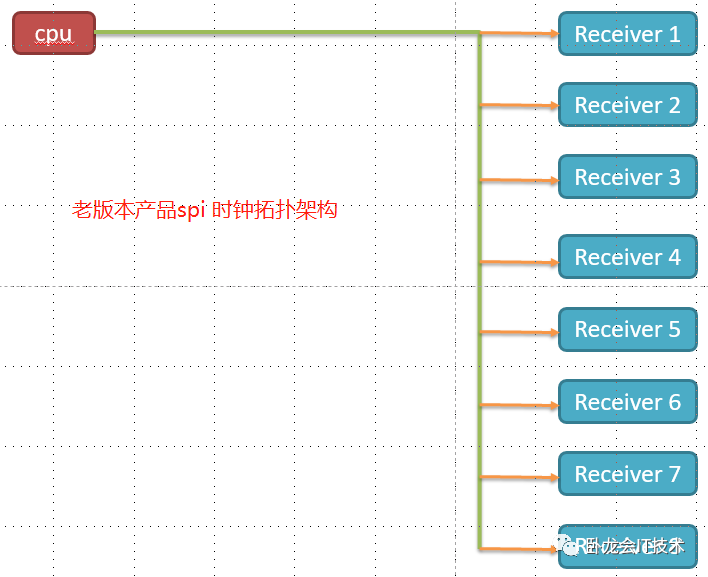

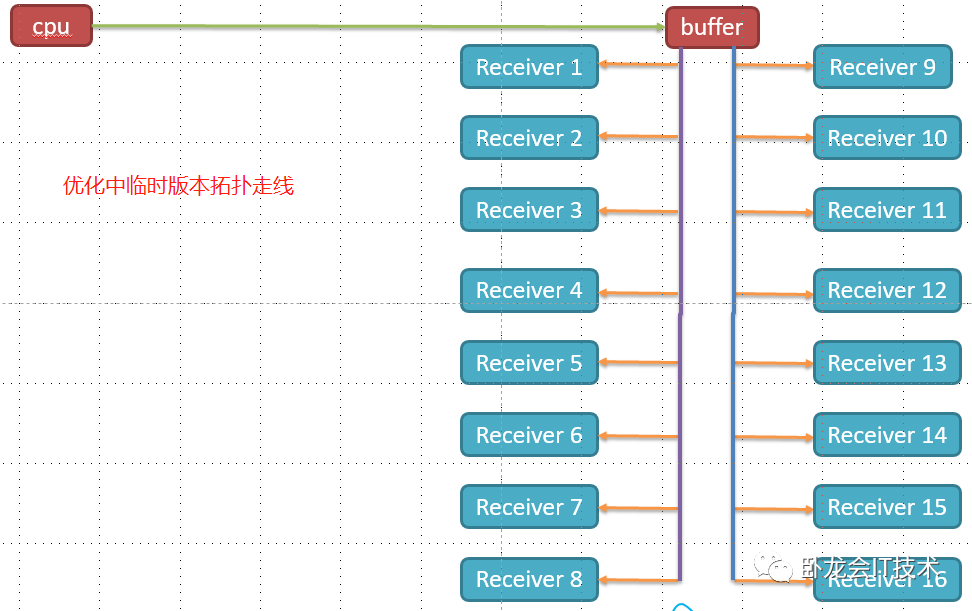

这不变化最大的其实最没有引起注意的是,之前业务芯片是一颗负责两路,新的芯片是一颗负责一路,然后就翻番了;然后spi从过去的1驱8改为1驱16了,因为芯片翻番走线尺寸也同时完全翻番(业务芯片QFN封装且外围电路高压低压配置一应俱全,单元电路面积较大)。

然后作者就觉得这事悬了,提出过优化拓扑的呼声意见在群情激奋大干快干的口号中也被淹没了。

但是信号质量饶过谁,这不就翻车了。

|| 正文

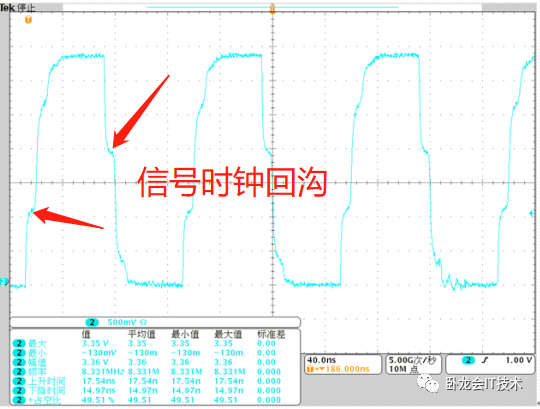

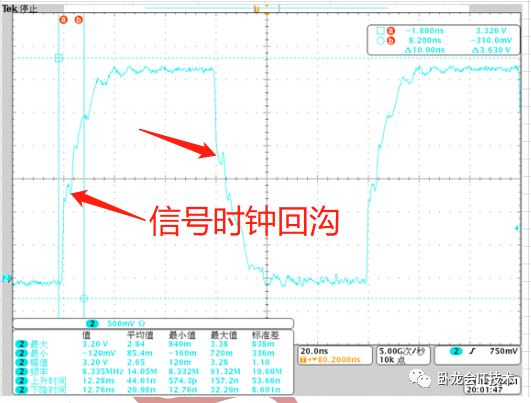

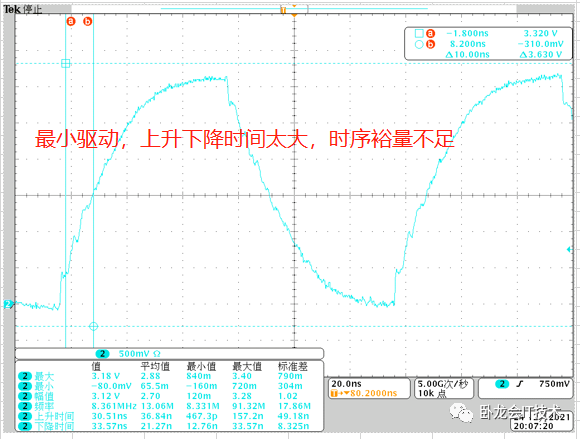

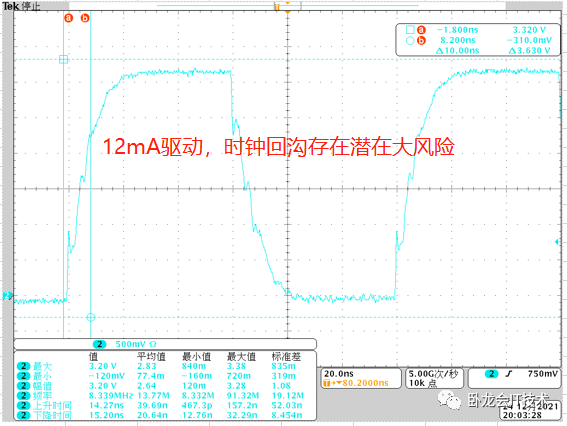

信号回沟不可怕,时钟回沟就有点要老命了。正常情况我们是杜绝时钟边沿上有回沟,特别是在非稳定区间及临界点上的回沟,更是绝不接受的。

事已至此,说啥都是虚的,作者提倡实际行动走起来!

边仿边测是王道,只仿不测是高手,只测不仿要么是高手(已经完全从理论经验积累上杜绝了),只测不仿要么是渣渣(太过于沉迷浅显的认知理解了)。

分析

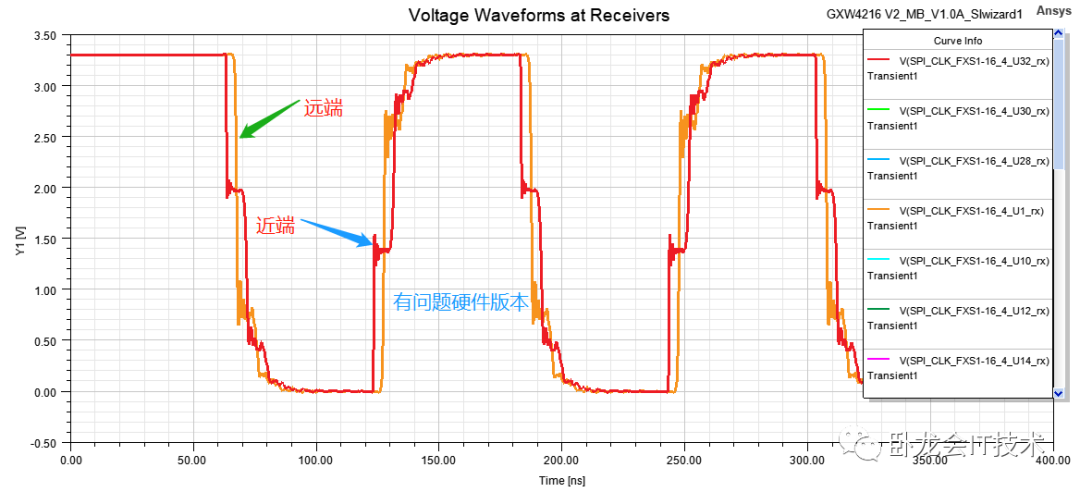

实际走线已看过,长得有点超出我的想象了,而且是一驱16啊,负载容性效应,走线寄生效应及反射叠加。近端的质量可想而知了,现在唯一的意思希望是提升驱动力看看能否明显好转点。

当然很不幸,驱动力已经是最大等级了。

分析设计

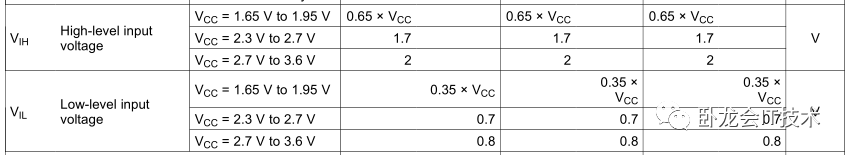

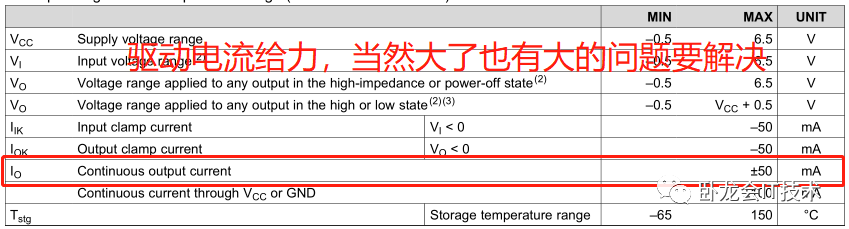

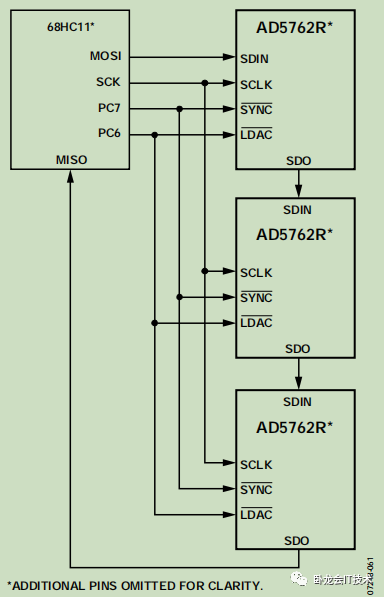

作者认为需要出大招了,上buffer。上buffer干嘛,缩短有效传输路径,增加驱动能力解决边沿时间过长及反射明显影响。

器件有了,该搞拓扑了。拓扑是个啥,就是连连看。

仿真结果

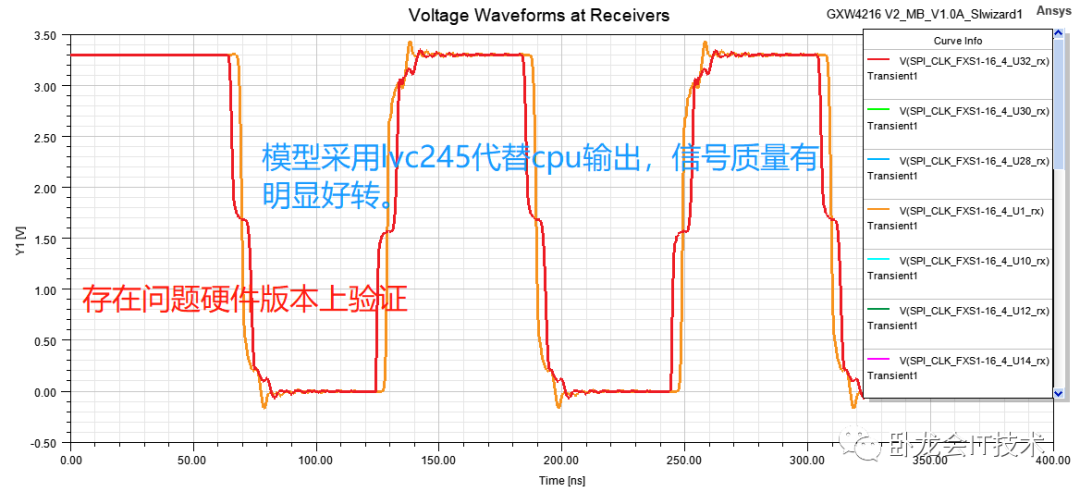

需要说明下,仿真过程中我们并没有使用实际器件模型,都是使用友商相应模型代替评估。仿真和实际测试结果偏差稍大点原因如下:

驱动电流达不到实际处理器输出12mA驱动,驱动电流最大10mA;

示波器探头影响,尽管测试中已经使用有源探头进行测试;

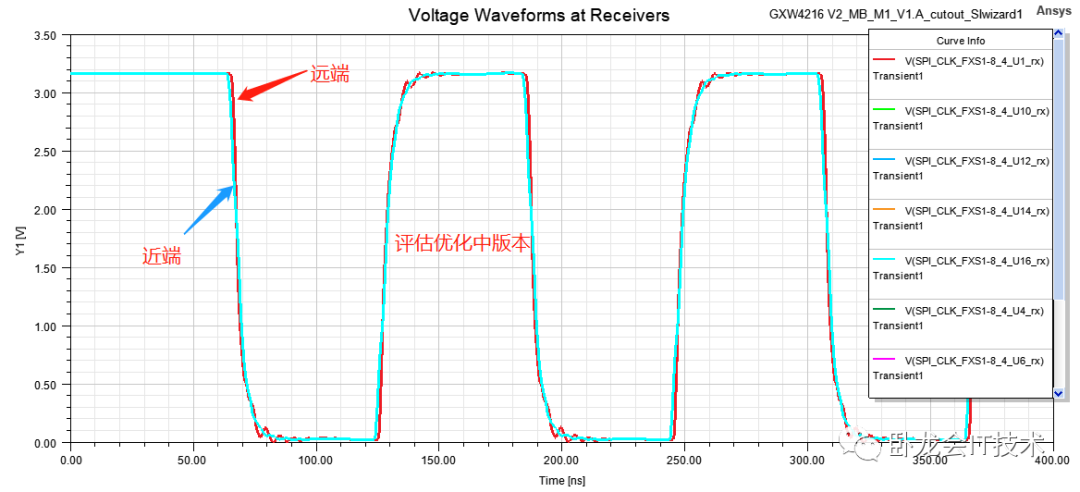

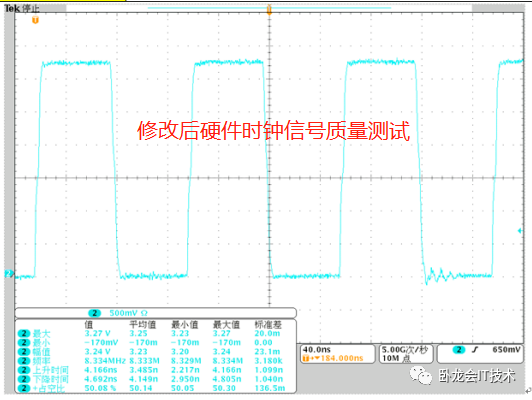

修改拓扑后,buffer输出段业务芯片上的时钟信号。信号质量明显去除回沟且边沿时间裕量较大。

|| 总结

作者一直认为存在即合理,其实在出现问题时候已经想到十多年前复杂通讯系统班上的jtag链接菊花链方式,但是很不幸使用的芯片不支持,但是芯片支持through模式,可以省却部分网络走线例如片选、多组输入。但是距离这种菊花链拓扑还是多了点复杂程度需要考虑注意。

-

时钟信号测试有回沟怎么办?测试点位置与芯片DIE分析2020-11-26 11546

-

信号反射的几个基本问题分析2019-10-16 8470

-

时钟信号回沟与测试点位置有关吗2020-11-25 2553

-

请问时钟信号回沟与测试点位置有关吗?2020-12-15 1739

-

测试中遇到的25MHz时钟信号回沟问题汇总2017-09-19 24563

-

时钟有回沟?什么原因会导致信号波形边沿的回沟?2020-12-18 25819

-

技术分析时钟有回沟还有救吗2021-03-17 1294

-

高速信号与高频信号的区别2022-09-14 6134

-

一个25MHZ时钟信号的单调性问题测试分析2023-06-13 3900

-

高速信号线跨沟对眼图抖动的影响分析2025-06-04 994

全部0条评论

快来发表一下你的评论吧 !