功率MOSFET基本结构:沟槽结构介绍

模拟技术

描述

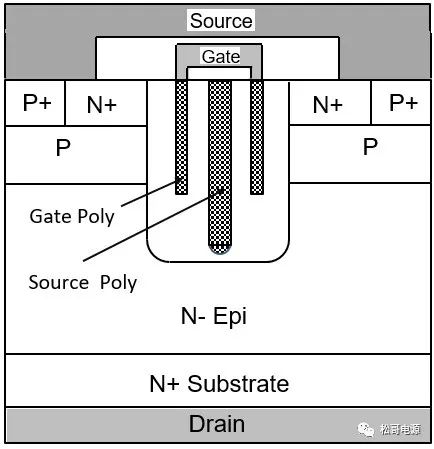

1. 沟槽双扩散型场效应晶体管

垂直导电平面结构功率MOSFET管水平沟道直接形成JFET效应,如果把水平的沟道变为垂直沟道,从侧面控制沟道,就可以消除JFET效应。

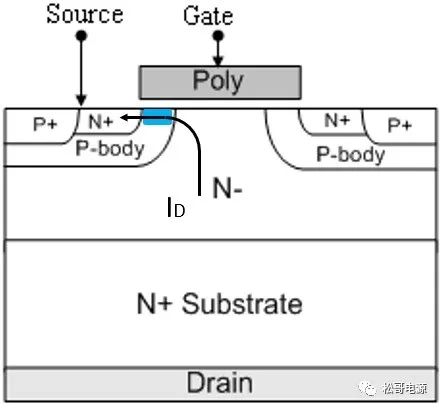

(a) 水平沟道

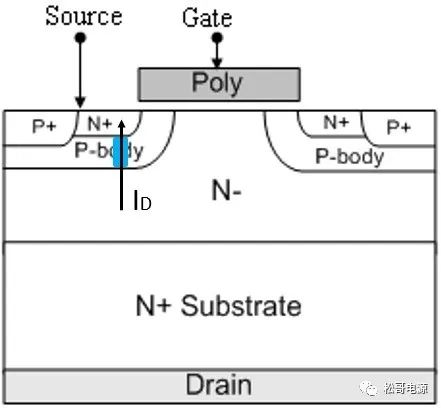

(b) 垂直沟道

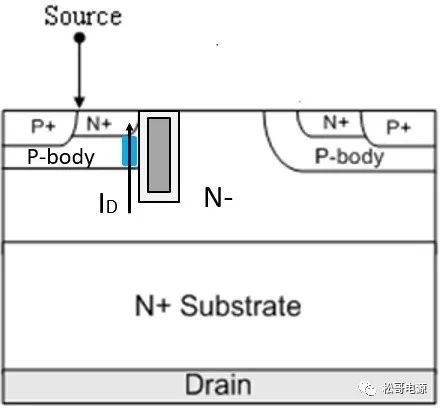

(c) 栅极沟槽

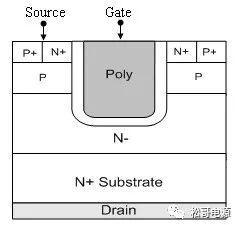

(d) 沟槽结构

图1. 沟槽结构功率MOSFE管

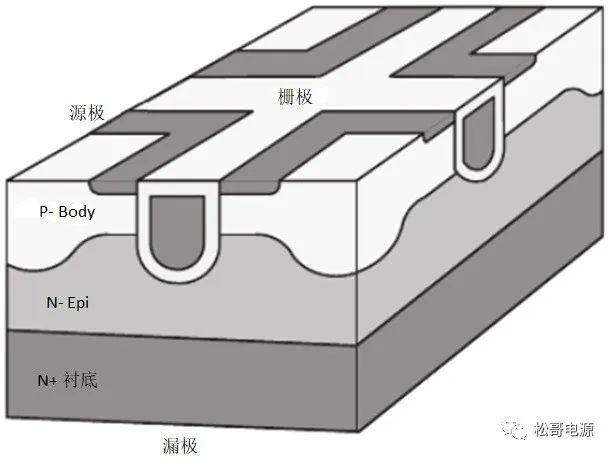

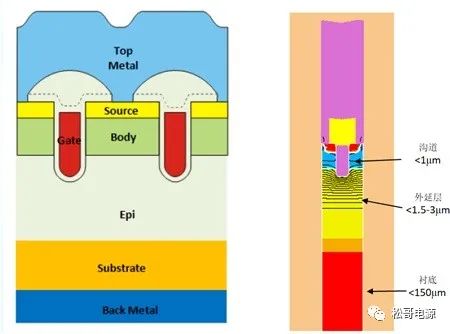

为了形成这种垂直沟道结构,必须在N-外延层中开沟槽,沟槽表面制作氧化层后,在沟槽内部填充多晶硅形成栅极;在沟槽氧化层外侧,通过二次扩散掺杂,形成P-体区,并在P-体区内部形成N+源极区。这种结构制作过程中,需要开沟槽(Trench),称为沟槽结构功率MOSFET管、Trench结构功率MOSFET管。

(a) 沟槽结构立体图

(b) 沟槽结构单个晶胞

(c) 沟槽结构多个晶胞并联

图2 沟槽结构功率MOSFET管立体和截面图

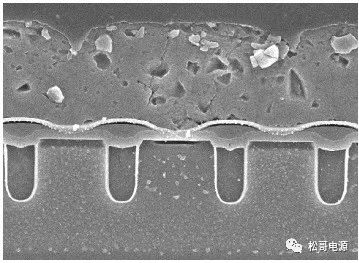

这种结构将栅极埋入基体中,形成垂直沟道,实际上就是使用内部深度来换取芯片表面面积,电流通路从下部衬底漏极,垂直流过N-外延区、沟道和N+源极区,沟道和电流方向平行,没有横向JFET寄生结构,因此,没有JFET效应和JFET电阻,导通电阻非常小;栅极水平方向截面积可以使用很小尺寸,栅极宽度远小于平面结构,寄生栅极漏极电容Cgd,即反向传输电容(米勒电容)Crss,大幅减小,开关损耗大幅降低;栅极宽度小,栅极所占用面积减小,晶胞单元尺寸(Cell Pitch)可以做得更小,芯片流过电流面积增大,芯片面积得到更为充分利用。同样芯片面积,单元尺寸更小,就可以制作更多单元,提高晶胞和沟道单位密度,进一步降低导通电阻。

如果单纯提高单元密度,输入电容Ciss和反向转移电容Crss也会增大,在高频工作条件下会削减低导通电阻获得的优势。这些电容可以通过调整沟槽内侧栅极氧化层厚度,特别是沟槽底部栅极氧化层厚度,来优化和降低这些寄生电容,这也导致生产工艺变得复杂。

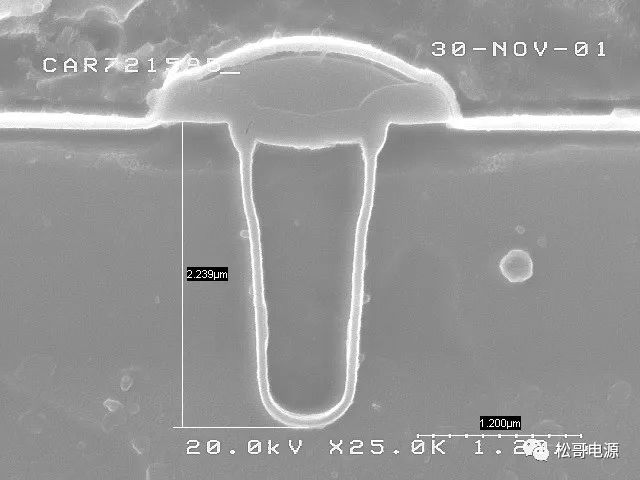

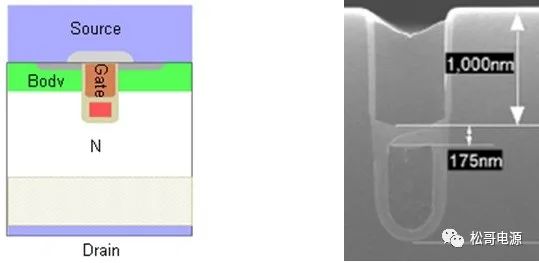

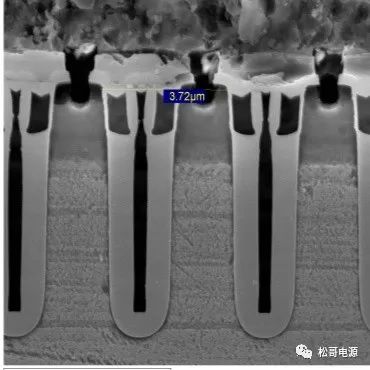

早期采用V型沟槽,由于沟槽底部尖角容易形成局部电场集中而产生高电场,影响器件可靠性,现在常用沟槽为U型沟槽。沟槽结构P-体区和N-漂移层形成PN结,称为J1,这个PN结电场强度大,耗尽层区域在P-体区会延展扩大,因此,沟道宽度和P-体区厚度必须相应增大,来保证要求击穿电压,这样会增大沟道电阻。PN结J1高电场在沟槽栅极氧化层中也会产生高电场,特别是沟槽底部拐角处,高电场产生空穴和电子对,影响器件的可靠性。沟槽底部表面圆滑度可以缓解这个问题,但是,氧化层电场强度还是非常大。

沟槽结构导通电阻小,开关速度快,满足现代电力电子技术高频高效、高功率密度的要求。这种结构内部需要开挖沟槽,工艺复杂,沟槽侧壁平直度、沟槽底部表面圆滑度,都影响器件性能,所以,各个单元一致性、跨导特性和雪崩能量比平面结构差,对工艺控制的要求比平面高。沟槽结构主要适用于低压和中压功率MOSFET,如30V功率MOSFET管用于高频非隔离BUCK变换器,80V、100V器件用于通讯系统模块隔离电源,100V、150V器件用于通讯系统热插拔电路。

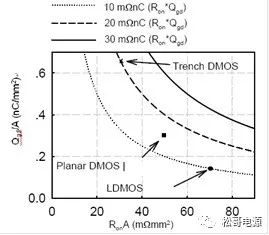

三种结构功率MOSFET管导通电阻和Qgd关系如图所示。

图3 三种结构的导通电阻和Qgd关系

沟槽结构功率MOSFET管漏极和源极电压,依然由低掺杂N-外延层所承担,电压越高,外延层厚度越大,外延层电阻和器件耐压的2.5次方成正比,外延层电阻是影响总导通电阻主要因素之一。

图3 沟槽结构MOSFET管各部分导通电阻

2. 屏蔽栅(隔离栅)SGT结构

为了提高电源系统效率,降低导通损耗,使用低导通电阻沟槽结构功率MOSFET管,内部芯片面积就会增加;芯片面积增加,栅极和漏极面积都会增大,寄生电容Crss、输入电容Ciss和输出电容Coss都会增大,在高频工作时候,功率MOSFET管开关损耗、驱动损耗都会急剧增加。功率MOSFET管导通电阻RDS(on)和寄生电容是相互矛盾参数,为了减小导通电阻,就必须增加硅片面积;硅片面积增加,寄生电容就会增加,因此对于一定面积硅片,只有采用新工艺技术,才能减小寄生电容。

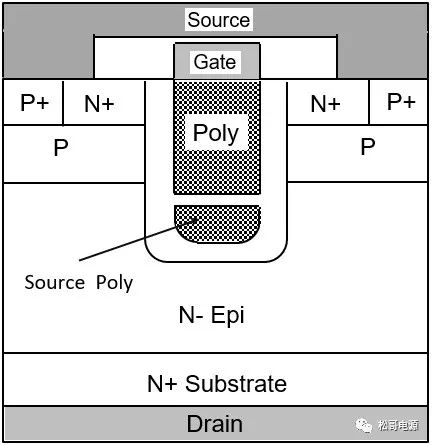

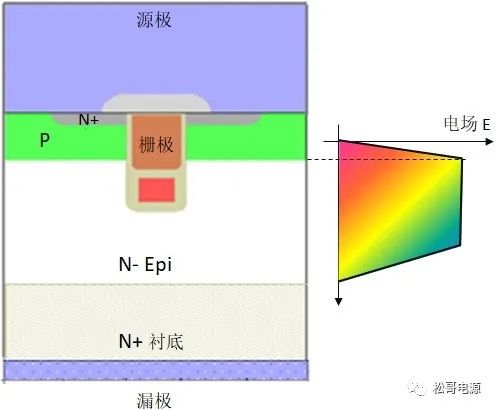

功率MOSFET管开关损耗主要与Crss、即漏极和栅极电荷Qgd相关,如果减小漏极和栅极相对区域产生的电荷,就可以减小电容Crss值。最为直接方法就是:在沟槽结构MOSFET管栅极沟槽最下面,也就是沟槽底部,引入一个低电位结构,这样,沟槽底部栅极氧化层外面N-外延层中,在反偏状态下,这种结构会辅助由P-Body和N-Epi构成PN结J1进行横向耗尽,形成电场强度更均匀分布耗尽层,从而实现更高击穿电压。这种结构栅漏电容Cgd大部分被转化为栅源电容Cgs,相当于降低漏极和栅极相对区域产生的电荷,从而极大减小寄生电容Crss值,提高功率MOSFET管开关速度。

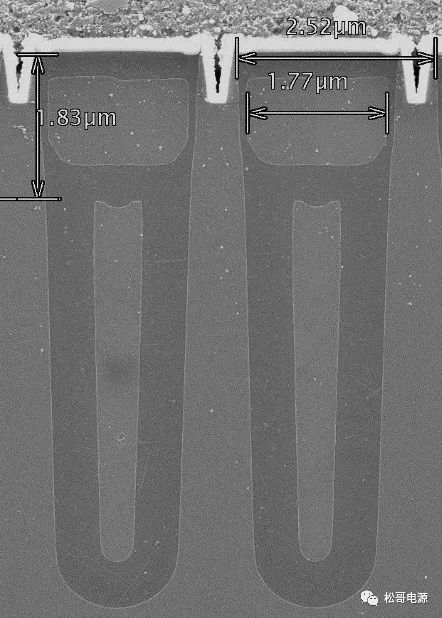

将沟槽中填充多晶硅,分为上、下二部分,二部分之间用氧化层彼此隔离。下面部分连接到源极,上面部分连接到栅极,就可以实现上面结构和功能。这种结构在普通沟槽结构栅极与漏极之间加了一个屏蔽层,称为屏蔽栅技术Shielding Gate Technology,这种结构普通沟槽结构栅极分开为上、下二部分,也称为隔离栅技术Split Gate Technology。这种技术二种名称英文缩写相同,因此,统一称为SGT技术。

(a) SGT单个晶胞结构 (b) SGT截面

图4 SGT结构功率MOSFET管

工艺设计时屏蔽栅可以使用上下结构,也可以使用左右结构。使用上下结构屏蔽栅单元尺寸(沟槽宽度)可以做的更小,主要用于低压功率MOSFET管;左右结构需要较宽沟槽,制作沟槽深度更深,电荷平衡效果更强,能够在更深区域提高电场,主要用于中压功率MOSFET管。

SGT结构功率MOSFET管极大降低漏极栅极米勒电容Crss(Cgd),减少开关过程中米勒平台持续时间,降低开关损耗,器件可以工作在更高频率。这种结构在沟槽底部栅极氧化层外面N-外延层中形成耗尽层,把附近N-外延层电场抬高,将普通沟槽结构N-外延层中三角形电场,变为梯形电场,从而大幅提高器件耐压。

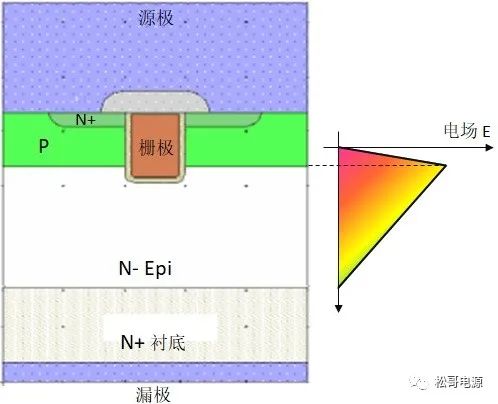

N-外延层为低掺杂,P-体区为高掺杂,功率MOSFET管漏极和源极加上电压,产生耗尽层时,耗尽层在P区扩散距离非常小,在外延层N-区扩散距离大,因此,可以认为耗尽层基本在外延层N-区扩散,器件耐压主要由外延层N-区承受。PN结结合面处,电场强度最大,电场强度沿着外延层N-向着衬底方向逐渐降低,器件耐压就是电场强度对耗尽层长度积分,也就是耗尽层长度和对应电场强度的曲线所包围面积。

(a) SGT上下结构

(b) SGT左右结构

图5 上下结构和左右结构的SGT

(a) 沟槽结构电场

(b) SGT结构电场

图6 沟槽结构和SGT结构内部电场分布

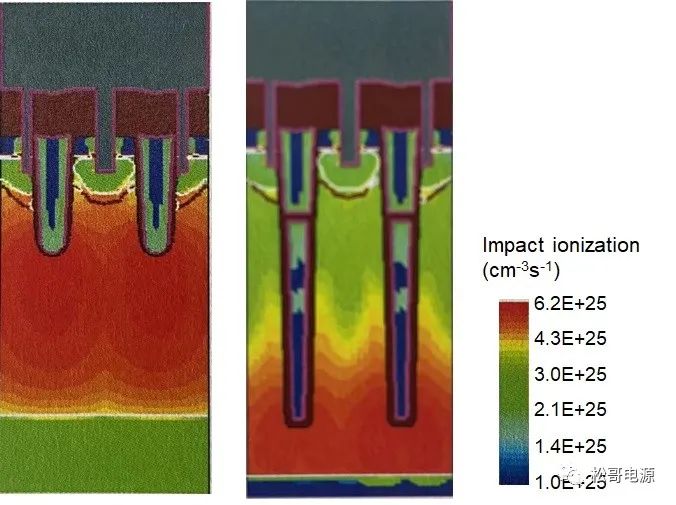

(a) 击穿Trench碰撞电离率 (b) 击穿SGT碰撞电离率

图7 击穿碰撞电离率对比

外延层厚度相同时,SGT结构功率MOSFET管内部为梯形电场,电场强度更高,耐压更高。对于相同耐压,SGT结构功率MOSFET管可以使用更薄外延层,外延层越薄,RDS(on)越低;更薄芯片更有利于内部沟道和外延层电阻产生热量传导出来,降低芯片热阻。目前,中、低压功率MOSFET管中,SGT技术取代沟槽结构,应用中占主导地位,实现开关电源和电力电子系统进一步向高频、高效率和高功率密度的技术方向发展和提高。

审核编辑:刘清

-

产品工程代表

2024-12-23

0 回复 举报好 收起回复

产品工程代表

2024-12-23

0 回复 举报好 收起回复

-

沟槽型SiC MOSFET的结构和应用2025-02-02 1965

-

功率MOSFET基本结构:平面结构2023-06-05 2359

-

沟槽结构SiC MOSFET常见的类型2023-04-01 3259

-

功率晶体管的结构与特征比较2023-02-23 1321

-

SiC MOSFET的结构及特性2023-02-16 5616

-

SiC-MOSFET和功率晶体管的结构与特征比较2023-02-08 1301

-

沟槽结构SiC-MOSFET与实际产品2018-12-05 4698

-

SiC-MOSFET功率晶体管的结构与特征比较2018-11-30 5443

-

功率MOSFET结构及特点2016-10-10 7430

-

世界首家!ROHM开始量产采用沟槽结构的SiC-MOSFET2015-06-25 2556

全部0条评论

快来发表一下你的评论吧 !