基于HFSS的3D多芯片互连封装MMIC仿真设计

电子说

描述

作品概述

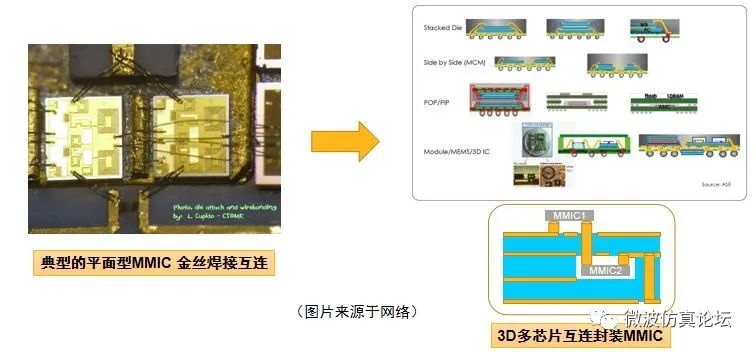

相对于传统平面型的金丝键合焊接的MMIC应用,三维(3D)多芯片互连封装MMIC以其高集成度、低损耗、高可靠性等性能优势,正逐步在先进电路与系统中得到应用。而3D封装引入的复杂电磁耦合效应,在传统MMIC仿真设计上并未包含。本设计基于HFSS,充分考虑实际封装寄生效应,建立了完整的3D多芯片互连精准模型,并给出了封装前后仿真结果对比分析。

仿真应用背景

平面型互连向3D集成互连发展

仿真结果分析、展示

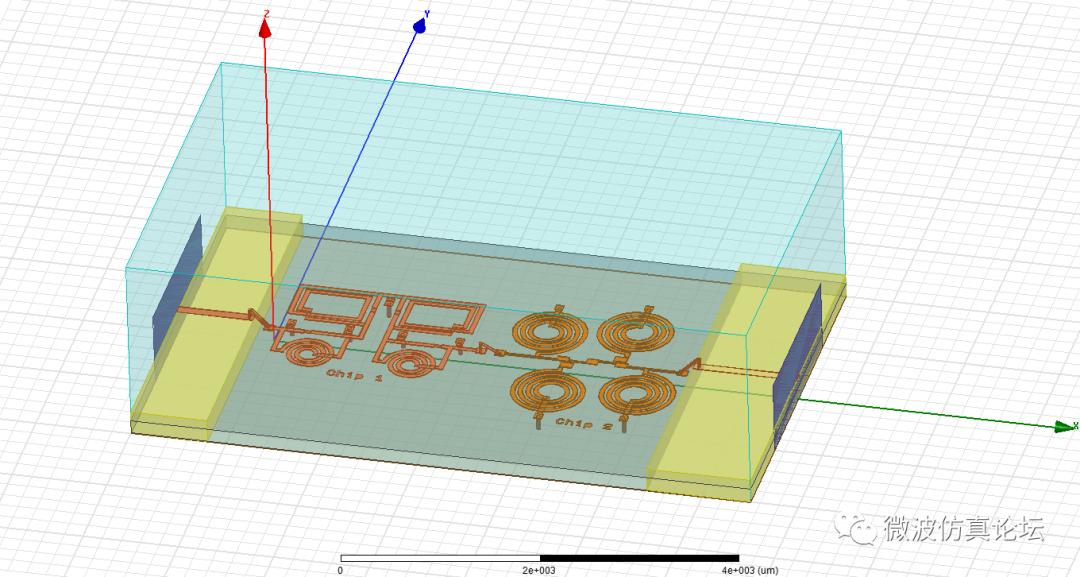

本设计用两个MMIC 互连展示

考虑两种连接情形分别建模与仿真

Case1:平面型金丝键合仿真模型

Chip1和Chip2为两个滤波器芯片;

Chip1和Chip2通过金丝键合;

输入和输出微带线采用陶瓷基板。

平面型金丝互连仿真模型

平面型金丝互连仿真结果

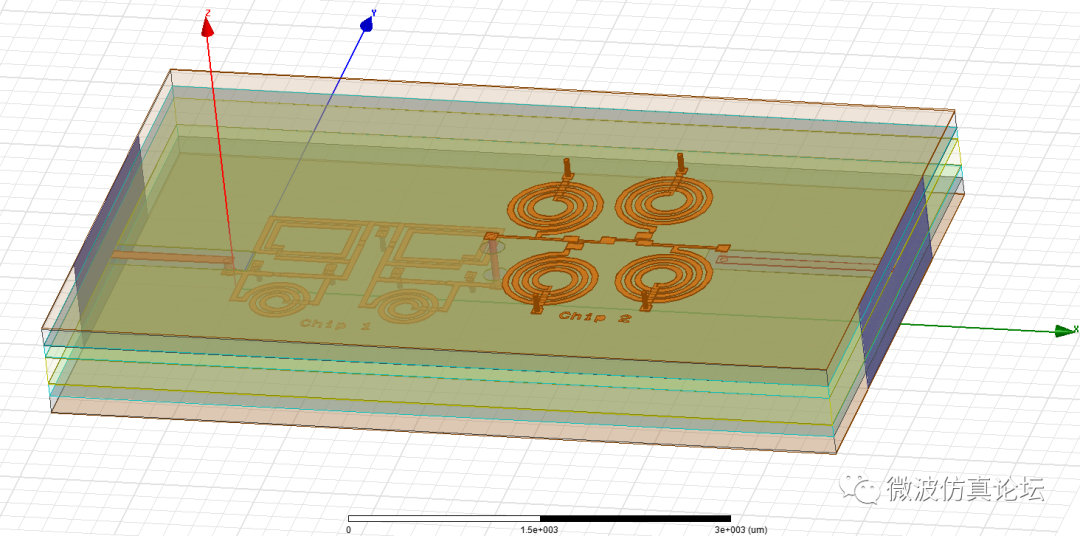

Case2:3D集成互连仿真模型

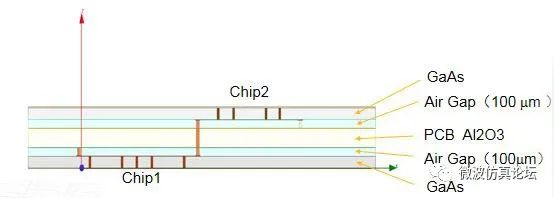

Chip1和Chip2,与Case1相同的两个滤波器芯片;

Chip1和Chip2通过通孔、铜柱或金球实现信号互连;

采用同样的陶瓷基板作为芯片的载体。

此处的空气腔高度设为100 μm。

截面图

3D集成互连仿真模型

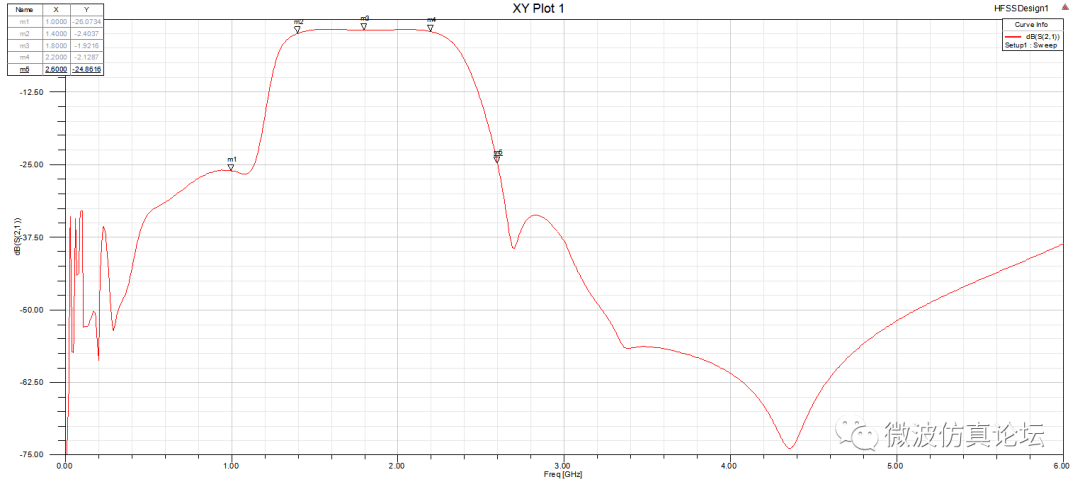

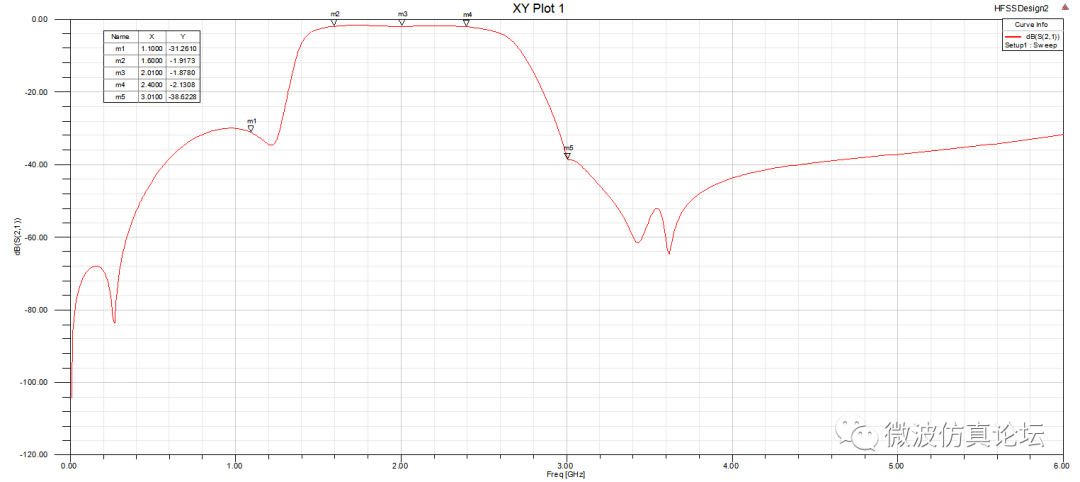

3D集成互连仿真结果

通带变为:1.6GHz~2.4GHz

原设计通带(Case1):1.4GHz~2.2GHz

频段偏移约10%。

小结

1,相较于平面型金丝互连,两个MMIC芯片3D集成互连之后,发生一定频偏,频带向高偏移约10%。

2,引起频偏可能的原因:

1) 3D集成的互连结构(通孔、铜柱、金球等)的寄生效应引起频偏,但相较于芯片中元器件如电感电容而言,该寄生参数相对较小,与金丝的寄生参数量级相当,故影响作用微小。

2) 3D集成引入了较小的空气腔,本设计空气腔高度为100μm(工程实践中会比这高度更低),带来了新的寄生效应,经分析,当空气腔高度为芯片基板3倍左右时,频偏现象可忽略。

3,通过本设计可以看出,应用于3D集成封装的芯片电路,若单纯采用传统平面型MMIC设计,3D封装后会造成一定的性能偏差。因此,需有针对性的做完整的3D集成封装MMIC优化设计,确保3D封装后满足电路指标要求。

审核编辑:汤梓红

-

一文详解多芯片封装技术2025-05-14 2618

-

3D封装技术能否成为国产芯片的希望?#芯片封装面包车 2022-08-10

-

HFSS高频电磁场仿真应用2016-04-22 8777

-

AD16的3D封装库问题?2019-09-26 5078

-

3D封装技术及其发展2011-09-16 3644

-

3D元件封装库2016-03-21 2843

-

英特尔逻辑芯片3D堆叠技术“Foveros” 将实现世界一流性能2018-12-14 3437

-

3D封装技术定义和解析2020-05-28 7516

-

新型2.5D和3D封装技术的挑战2020-06-16 8827

-

利用HFSS软件进行3D可视化建模2021-05-10 6855

-

2.5D/3D芯片-封装-系统协同仿真技术研究2022-05-06 1474

-

分享一下小芯片集成的2.5D/3D IC封装技术2022-08-24 5957

-

3D封装结构与2.5D封装有何不同?3D IC封装主流产品介绍2023-08-01 5606

-

3D封装架构的分类和定义2025-10-16 2266

-

烧结银:3D封装中高功率密度和高密度互连的核心材料2025-12-29 883

全部0条评论

快来发表一下你的评论吧 !