verilog的数据类型

verilog的数据类型

描述

1、常量

整数:整数可以用二进制数b或B,八进制o或O,十进制d或D,十六进制h或H表示,例如:8‘b10101010表示8位位宽的二进制数;

x和z:x代表不定值,z代表高阻值,例如,5’b0x111,第四位不定值,3‘bz00表示最高位为高阻值;

下划线:在位数过长时可以用来分割位数,提高程序可读性,如8’b0101_0101;

参数 parameter:可以用标识符定义常量,运用时只使用标识符即可,提高可读性及维护性,如可以定义parameter width = 8 ;定义寄存器 reg [width - 1 : 0] a;即定义了八位宽度的寄存器;

参数的传递:在一个模块中如果有定义参数,在其它模块调用此模块时可以传递参数,并可以修改参数;

注意:parameter可以用于模块间的参数传递,而localparam仅用于本模块内使用,不能用于参数传递。localparam多用于状态机状态的定义;

2、变量

变量是指在程序运行过程中可以改变其中的值,常见的变量类型主要有wire型和reg型

wire型

wire类型变量,也叫网络类型变量,用于结构实体之间的物理连接,如门与门之间,不能储存值,用连续赋值语句assign赋值,定义为wire[n-1 : 0] x ;其中n代表位宽,如定义wire x; assign x = y ;是将y的结点连接到连线x上;

reg 型

reg类型变量,也称为寄存器变量,可用来储存值,必须在always语句内使用。通常可以定义为:reg [n-1 : 0] a ;表示n位位宽的寄存器, 如reg[7 : 0] a ; 表示定义8位位宽的寄存器a。

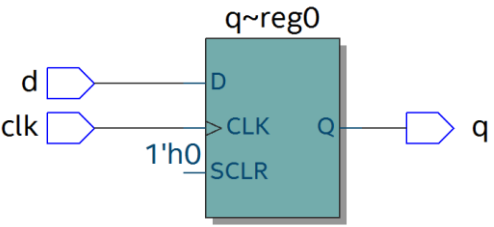

module cs (d, clk, q) ;

input d ;

input clk ;

output reg q ;

always @ (posedge clk)

begin

q <= d ;

end

endmodule

寄存器的结构图

以上便是关于verilog的常见数据类型的相关知识,希望对你有所帮助。

-

[4.2.1]--4.2verilog数据类型jf_75936199 2023-03-09

-

Verilog 变量声明与数据类型二2021-08-06 2008

-

Verilog 变量声明与数据类型一2021-08-10 4593

-

verilog的数据类型及逻辑系统2016-01-08 340

-

vhdl数据类型2018-03-30 1890

-

verilog的数据类型2020-09-28 3553

-

Struct结构数据类型2022-07-25 3806

-

结构数据类型(Struct)及应用案例2022-07-27 2639

-

什么是数据类型转换2023-02-23 2434

-

定义数据类型2023-03-03 1768

-

Verilog中的基本数据类型2023-05-12 11694

-

Verilog最常用的2种数据类型2023-05-29 3441

-

Verilog基本语法之数据类型2023-06-18 4208

-

Redis的数据类型有哪些2023-10-09 1398

-

plc数据类型怎么理解和应用2023-12-19 6470

全部0条评论

快来发表一下你的评论吧 !