浅谈电子组装的混合工艺发展

制造/封装

描述

摘要

电子组装行业在中国落地生根已有30多年的历程,从人工手插件DIP、自动化插件机AI、到目前很普及的表面贴装技术SMT,这些工艺在中国、特别是广东的深圳、东莞,用得炉火纯青。

但是随着晶圆技术的发展和多种先进封装技术的出现,电子产品设计的复杂程越来越向晶圆级的设计方向靠拢,芯片的引脚间距的趋势跟摩尔定理一样,越变越小,SMT 的工艺及设备发展难度越来越大,已无法适应电子产品设计的发展需求。

从芯片封装从2D、2.5D到3D的发展,以及SIP和MEMS等元器件的封装变化,电子组装技术也完全可以借用芯片封装的发展思路进化,因此电子组装的混合工艺路线也就越来越清晰了。

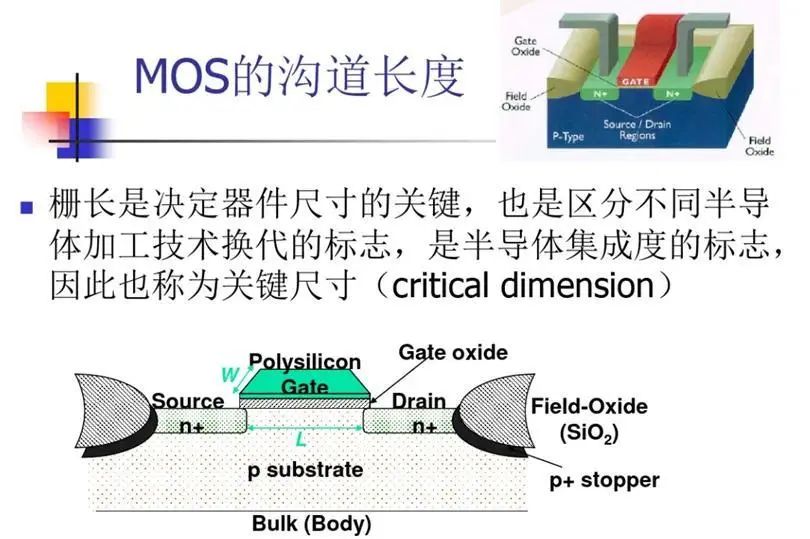

晶圆制程工艺从90nm发展到45nm,再到22nm,进而14nm、10nm、7nm、5nm、3nm、2nm这些激进的制程工艺飞速推进,引爆了各种先进工艺的深度演化。这个纳米级的制程工艺的内涵到底是指什么?多少纳米的工艺制程指的是MOS 晶体管的源和漏的距离,也就是栅极距离(Gate Length)。栅极距离越小,在相同的面积里能蚀刻出更多的MOS 晶体管。

Gate Length是决定MOSFET 的关键尺寸,制程节点以0.7倍的速度减小,单位面积芯片上晶体管数量以2倍的速度增加。

相同单位面积里的MOS晶体管数量不断以2倍的速度增加,芯片的封装尺寸虽然不可能也是以2倍的速度增加或者不增加,但是芯片封装引脚间距(PICTH)确是实打实的在不断缩小,Fine Pitch以前定义的是引脚中心间距小于0.5mm,对于现在来说0.5mm或0.4mm已是很平常的间距了,引脚中心间距从0.5mm,到0.4mm、0.35mm、0.3mm、0.25mm、0.2mm、0.15mm等。

这些变化给我们目前应用最广泛的SMT工艺带来巨大挑战。首先的锡膏印刷工艺,其次是钢网制作,再次是辅料锡膏成本的上升,还有回流焊接的短路、虚焊、少锡等等相应品质问题的挑战。

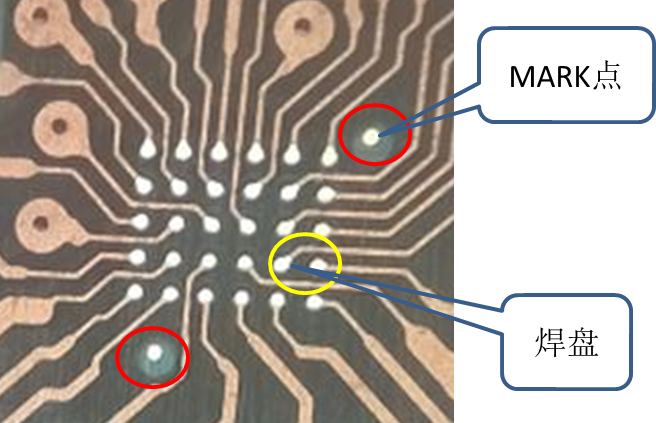

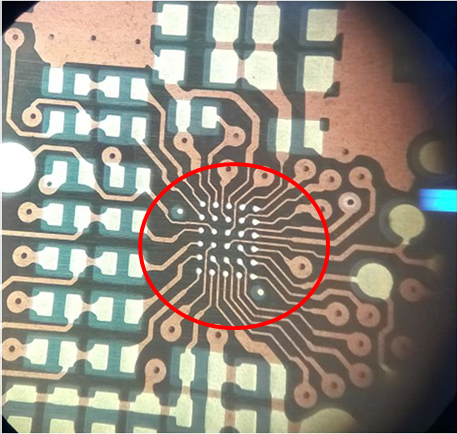

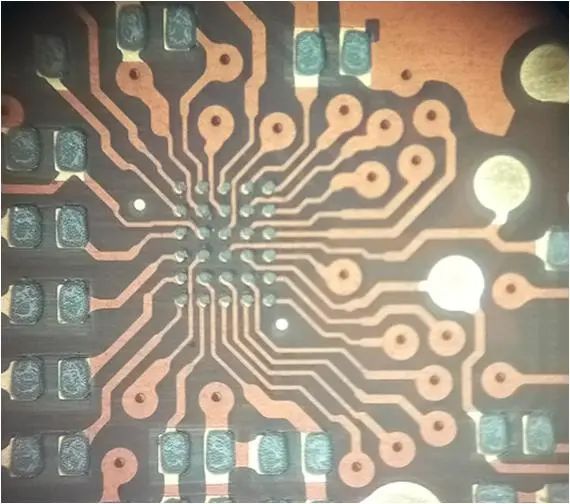

一款FPC模块产品的IC引脚间距为0.2mm,锡膏印刷制程已突破了极限。Pitch为0.2mm的IC设计,两引脚间还需走一根引线,FPC的基板焊盘LAYOUT尺寸已小到0.06mm,跨入了um级工艺制程。

IC引脚Picth为0.2mm焊盘尺寸为0.06mm

对于此种精细间距的芯片及um级的焊盘设计,普通的SMT工艺良品率很低,成本及效率上是无法接受的。只能采用非常规的工艺流程:

先在FPC或芯片引脚上植锡,形成锡球,检查在焊盘上形成锡球的良好性;再在对应的位置刷上助焊膏,贴装芯片,过炉回流,完成精细间距芯片的电气性能联装。

此种工艺方法的好处是检查方便、直观,同时采用助焊膏的方式进行焊接,极大地减少连焊的不良,提高产品良率,制造成本完全可以接受。在FPC上预植锡点的方法是效率高、良品率是4个9,芯片焊接后的良品良也是在99.9%以上。

但是有些产品采用SMT锡膏焊接方式也无法实现元器件的电气性能的联装,就必须采用其它方式,如邦定工艺、ACF工艺等与PCBA联装工艺差别很大的工艺方法完成了。

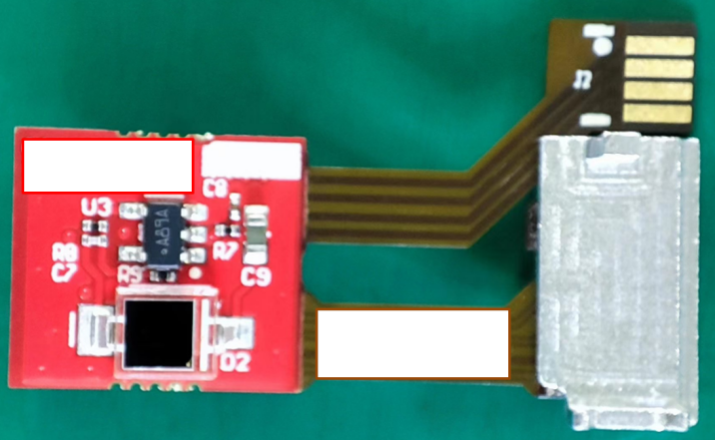

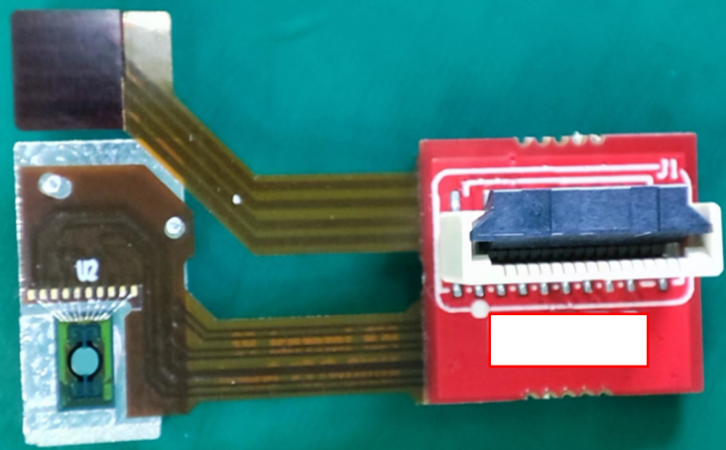

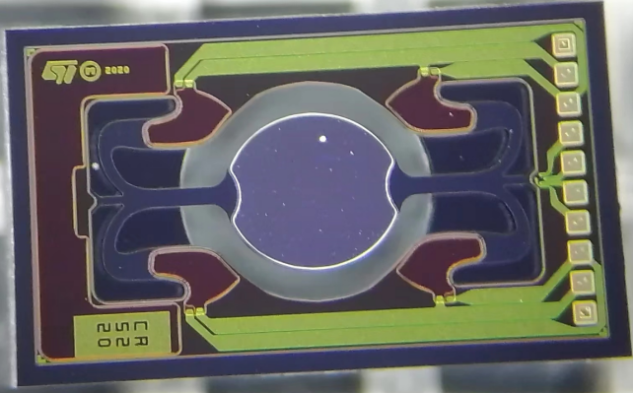

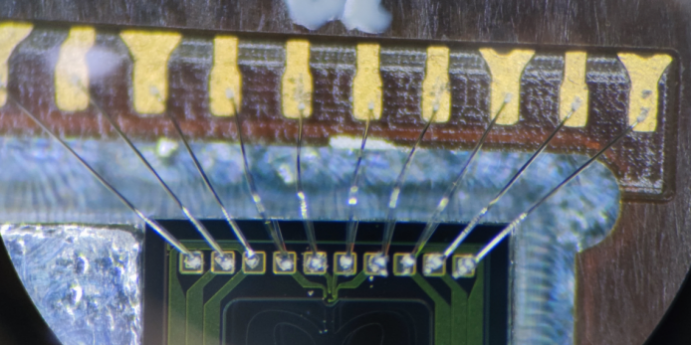

产品上有一元件(传感器,不能承受高温如回流焊接高温)无法采用SMT方式焊接,对元件外观表面的要求在20倍的放大镜下观察不得有脏污,SMT的无尘车间环境也无法满足生产要求,因此采用芯片封装工艺之一的邦定工艺进行:邦定车间环境及工艺参数(不需高温)可以符合元器件的电气性能联装的要求。

传感器元件 邦定工艺

从上述两例生产工艺可以说明,传统的SMT工艺不再是单一的工艺,在特殊元器件的要求还得引入其它制程工艺来完成相关产品的生产,从而产生了电子组装的混合制程工艺,生产效率、品质及制造成本都可满足客户的要求。

碰到一些有特殊要求的元器件联装,传统的制程工艺需要打破,引进其它制程工艺,同时也看到邦定工艺不再仅用于芯片封装制程,ACF工艺也不仅限于COG/COB/COF的产品上。

电子组装的混合工艺也不仅限于所提到的工艺制程,只要敢于打破常规思路,新的工艺就会层出不穷,思路就源源不断地涌现。

传统的电子组装SMT技术的发展不仅限于锡膏制程、红胶制程,它的发展已逐步与半导体的先进封装工艺融合在一起,且步阀在加快;半导体封装形式也在不断推出新的制程,如SIP、FC、POP、PIP等封装制程工艺里也融合了SMT技术。半导体封装技术与传统的电子组装技术区域界限日趋模糊,已是你中有我、我中有你,共同应付市场产品的需求。

在制造业高度市场化的今天和未来,电子组装制造业的制程工艺必然是各种先进制程工艺的混合体,单一的工艺模式在日趋激烈的市场竟争中很难存活,同时对我们的工程技术人员也提出知识整合、融汇的要求。

作者简介

从事电子组装行业近25年,经历了DIP、AI及SMT的工艺发展,曾供职于世界前三强的电子制造企业及芯片封装企业,制定了企业的PCB LAYOUT规则,制定企业内的QFN封装元器件焊接标准。目前在深圳市则成电子股份有限公司,任职技术总监。

审核编辑:汤梓红

-

SMT组装工艺流程的应用场景2023-10-20 1258

-

SMT组装工艺流程的应用场景(多图)2023-10-17 3129

-

电子成品组装薄膜面板制作工艺对比2023-03-24 1718

-

什么是微组装技术 微组装设备的核心工艺2021-10-14 13191

-

不同类型的PCB组装工艺指南2020-10-20 3053

-

常用的电子组装工艺筛选方法2020-02-29 2160

-

刚柔性PCB制造工艺技术的发展趋势2019-08-20 4880

-

倒装晶片的组装工艺流程2018-11-23 4935

-

SMT贴片加工技术的组装方式介绍2018-09-18 2464

-

【转】SMT贴片加工的发展特点及工艺流程2016-08-11 7733

-

含铅表面组装工艺和无铅表面组装工艺差别2016-07-13 3452

-

表面安装pcb设计工艺浅谈2012-08-20 2842

-

浅谈项目教学在电子工艺实训环节中的应用2010-01-16 1307

-

浅谈回流焊工艺发展2009-04-07 4950

全部0条评论

快来发表一下你的评论吧 !