Verilog UDPs的语法说明

电子说

描述

1、UDP的使用场景

User-defined primitives (UDPs) 翻译过来就是用户自定义原语,常常用于构建组合逻辑模型和时序逻辑模型。

我们编写Verilo代码时,定义寄存器使用的是reg 和always@(*clk*),运行VCS RTL仿真时,VCS能够识别此类信号是寄存器,能够模拟其行为模型。

然而在使用VCS进行网表仿真时,此时网表中寄存器名称是这样的SDFF*_XXXX,其中SDFF_XXXX是每个寄存器类型对应的标准Cell的名称。

SDFF_XXXX是每个Fab厂家独有的名称,且在Verilog规范中并没有相关术语,那么VCS等EDA仿真工具是如何识别并且模拟其器件行为的呢?

实际上进行网表仿真时,EDA工具会读取对应SDFF_XXXX的UDPs模型,从而进行SDFF_XXXX的行为模拟。

2、UDPs的语法说明

2.1. 2种类型

UDPs的分为combinational UDP(组合逻辑)和 sequential UDP(时序逻辑)。

combinational UDP用于构建组合逻辑模型,常见有mux模块.

sequential UDP用于构建寄存器和Latch模型,sequential UDP可以是边沿触发,也可以是电平触发。

2.2.基本语法规范

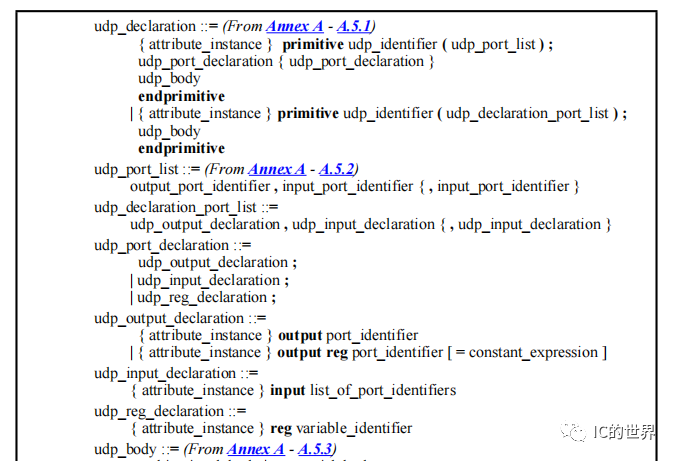

UDP建模使用primitive表示建模开始,类似module,endprimitive表示建模结束,类似endmodule。

UDP模型在描述层级上与module/endmodule属于同一等级,因此primitive/endprimitive不能出现在module/endmodule内部,就像不能在一个模块里出现module~module~endmodule~endmodule.

//语法错误 module xxx(); primitive endprimitive endmodule

每个UDP有且只有一个输出,并且输出只有三种状态,0, 1, or x,不支持Z状态。

每个UDP可以由多个输入信号,如果输入信号为z,则当做X对待。时序UDP至少允许9个输入信号,组合UDP至少允许10个输入信号。

每个UDP不支持定义inout类型的信号

时序UDP的输出信号应该使用reg申明。

组合UDP的输出信号不能使用reg申明。

时序UDP可以使用initial语句定制仿真开始前output信号的初始值

2.3.UDP state table(状态表)

UDP模型使用状态表来描述模型的行为,

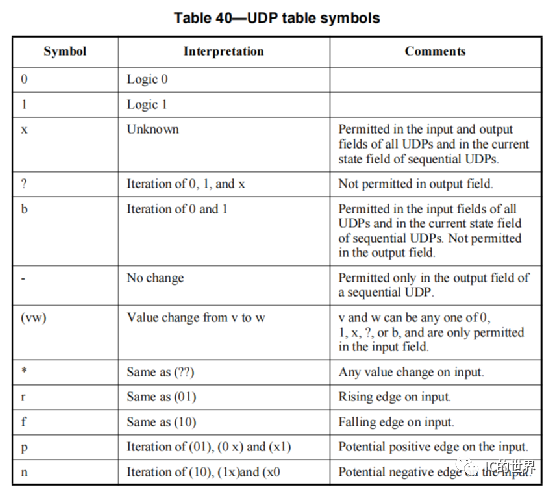

状态表中使用的各类变量见表40。例如r表示上升沿,f表示下降沿。*表示数值改变。

状态表中的每行以分号结束。

状态表本质上就是一个输入信号/输出信号组合的列表。

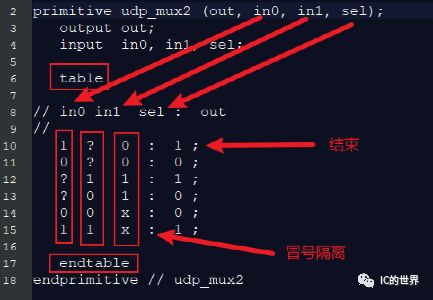

组合UDP状态表中有一个冒号“:”,用于隔离输入和输出信号。

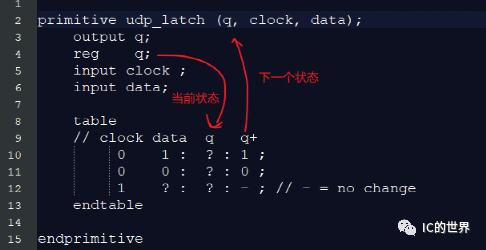

时序UDP状态表中有当前状态,还有下一个状态,因此有2个冒号“:”,用于隔离输入、输出(当前状态)和下一个状态。

组合UDP模型中,如果输入信号状态组合在状态表中没有指定,则输出会是X。

2.4.UDP结构

本节可忽略,直接看案例

3、组合UDP案例

如下案例为2选1的mux,sel为1时,out为in1;sel为0时,out为in0。

请注意:信号列表中,输出信号out在第一个。状态表中,out处于最后一列。

4、电平触发时序UDPs

如下案例为一个低电平触发的latch。

使用reg申明了一个内部变量,表示当前状态q,即当前udp的输出状态。

table中的q+代表的是下一个有效周期的输出状态。

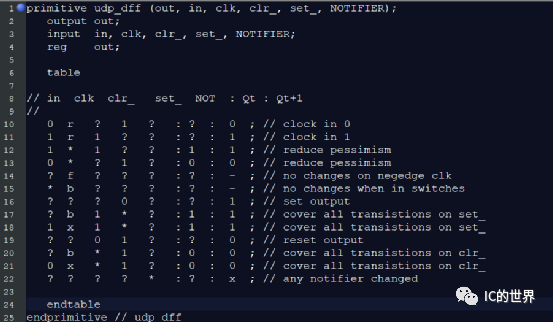

5、边沿触发时序UDP

如下所示为一个上升沿触发寄存器的模型。

其中NOTIFIER信号用于建立时间和保持时间检查,通过建立时间和保持时间检查,则NOTIFIER不变,时序检测不通过则NOTIFIER翻转,udp_dff输出为x态。

6、小技巧

将primitive类比成module,将endprimitive类比成endmodule,将table 类比成case,将endtable类比成endcase,你就知道该怎么写UDP模型了。

7、总结

虽然使用UDP能够构建网表时序逻辑和组合的逻辑的行为模型,但是仿真终究是仿真,无法做到与实际芯片行为完全一致,特别是在部分信号为X态时。因此网表仿真中如果X态的出现导致仿真出现问题,此时不代表电路真的存在问题,需要仔细分析原因,其中需要重点分析UDP模型是怎么写的。

-

Verilog HDL的基本语法2012-08-15 3464

-

Verilog HDL语法2016-01-24 8846

-

verilog HDL语法总结2020-03-16 3061

-

Verilog基础语法2021-05-27 3591

-

verilog是什么?基本语法有哪些?2021-09-18 2015

-

可综合的Verilog语法和语义2012-05-21 521

-

Verilog_HDL的基本语法详解(夏宇闻版)2012-10-08 2111

-

Verilog HDL实验练习与语法手册2016-05-11 918

-

常见的Verilog行为级描述语法2018-09-15 10853

-

FPGA视频教程之Verilog语法基础的详细资料说明2019-03-01 1703

-

Verilog HDL的基础知识详细说明2019-07-03 1658

-

有关Verilog中的一些语法详细资料说明2019-07-25 1772

-

Verilog语法进阶2021-05-06 802

-

Verilog HDL入门教程-Verilog HDL的基本语法2022-01-07 2020

-

Verilog语法中运算符的用法2024-10-25 3386

全部0条评论

快来发表一下你的评论吧 !