数码管的显示原理及其实现方式

描述

在数字FPGA电路中,作为入门级别的外设除LED灯外,数码管算是使用频率最多、应用范围最广的一个核心集成外设了,因此学习数码管的使用非常有必要,下面一起来看看数码管的显示原理及其实现方式吧!

1. 数码管显示原理

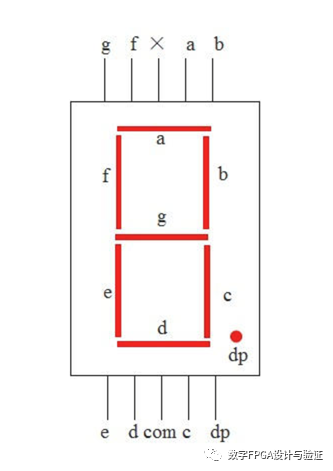

数码管是电子设计中常用的外设设备之一,用来显示一些数据数值。常见的数码管有单个的以及多个共用一起的,那么首先由最简单的单个数码管的原理介绍,方便大家的理解。如下图a所示:

图a单个数码管内部结构

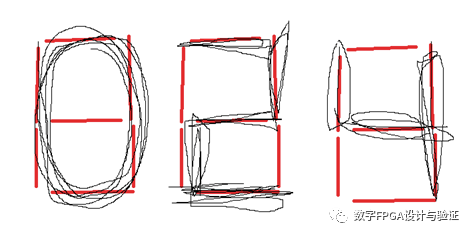

这就是一个常见的单个数码管内部的结构造型,可以理解成7个长方形的LED小灯组成,由这些小灯的亮灭状况来组成数码管显示的不同数值,下面我以手绘图展示几个数字的情况,大家应该能更清楚直观的明白其工作原理,如下图b所示:

图b显示数字024

这里是三个单独的数码管,分别显示数字0、2、4,所以数码管的原理可以简单的理解为点亮小灯的组合排列即可(具体内部电路的可以参考后面的附录,因为其不属于数字电路的内容,故放在附录中),明白了数码管的原理那么再来实现这部分的操作就很简单啦,下面就一起具体看看是如何实现的吧。

2. 数码管显示部分的程序实现

在日常生活中灯的亮灭是通过开关来进行控制,开可以理解为一个高电平的指令,关则相反,而在数字电路中,逻辑电平高低分别用1和0来进行表示,因此要实现点亮数码管的功能,也就可以通过0和1来进行控制a~g这七个小灯,比如让数码管显示1那么只需要b、c这两个小灯点亮就可以了,那么下面就来实现数码管显示部分的程序,使用的Verilog语言:

module one_digit(

input [3:0] data,

output [7:0] seg

);

reg [7:0] seg;

always @(data) begin

case(data)

4'h0:seg = 8'b11000000;

4'h1:seg = 8'b11111001;

4'h2:seg = 8'b10100100;

4'h3:seg = 8'b10110000;

4'h5:seg = 8'b10010010;

4'h4:seg = 8'b10011001;

4'h6:seg = 8'b10000010;

4'h7:seg = 8'b11111000;

4'h8:seg = 8'b10000000;

4'h9:seg = 8'b10010000;

4'ha:seg = 8'b10001000;

4'hb:seg = 8'b10000011;

4'hc:seg = 8'b11000110;

4'hd:seg = 8'b10100001;

4'he:seg = 8'b10000110;

4'hf:seg = 8'b10111111;

endcase

end

endmodule

以上就是基于的是LUT查找表的原理所写的单个数码管显示的程序。

3. 数码管程序的验证

当写完一部分语法验证没有错误、编译能够成功的程序后,下面要做的就是核心的功能验证,那么对于上面的数码管程序如何进行验证呢?

对于FPGA设计的验证来说,常见的验证方式有两种:a.仿真验证b.下板验证,当身边没有合适硬件板卡的时候,仿真验证往往是不错的选择,这个时候借助一些EDA工具,可以方便的验证好设计的程序逻辑功能是否正确,Modelsim就是这样一款便于仿真验证的工具,当然进行仿真验证的时候也需要进行激励的输入(编写一部分代码),下面对这个数码管的程序使用仿真验证的方式看看效果吧,如下图c所示:

图c数码管仿真结果

可以从仿真波形的高低判断出对应的数码管内部LED小灯的亮灭情况,由此排列组合推断出实际的数码管显示情况,以此作为仿真验证判断的依据,下面给出仿真验证的程序:

`timescale 1ns/1ns

module TB_one_dight;

reg [3:0]data;

wire[7:0]seg ;

one_digituut(

data,

seg

);

initial begin

data= 0;

#100;

repeat(16)begin

data= data+ 1;

#100;

end

$stop;

end

endmodule

至于实物验证的部分的话,建议结合相关的硬件板块配套例程来进行学习验证,这里就不做板卡推荐了,FPGA板卡以实物配套为文档教程为准。

-

基于51单片机实现动态数码管显示2023-07-17 17178

-

数码管静态显示原理2021-11-22 2012

-

如何实现多个数码管同时显示呢2022-03-02 4931

-

数码管显示实验2008-09-28 16140

-

数码管的驱动方式2009-11-06 4332

-

LED数码管显示分类及其典型应用电路2012-07-31 13107

-

数码管(静态显示)【汇编版】2015-12-29 1118

-

动态数码管显示程序2016-01-12 1212

-

数码管的结构与驱动方式2017-05-05 12783

-

数码管显示的多种方式2017-09-06 2535

-

单片机中的数码管显示原理及其实现2021-11-11 998

-

MCS-51实现静态数码管的显示2021-11-25 930

-

静态数码管和动态数码管2022-01-12 2374

-

LED数码管的显示方式和驱动方式2024-05-30 6282

-

7段数码管的显示方式有哪几种,各自的特点是什么?2024-08-28 3011

全部0条评论

快来发表一下你的评论吧 !