verilog的逻辑运算符

描述

写在前面

之前曾经整理过verilog的各类运算符的表达方式,但是在学习的过程中并未深入研究关于逻辑运算符的相关知识,导致在实际使用过程中错误频出,下面是我从网络上整理的相关verilog的逻辑运算符的相关知识,希望对各位有所帮助。

分类

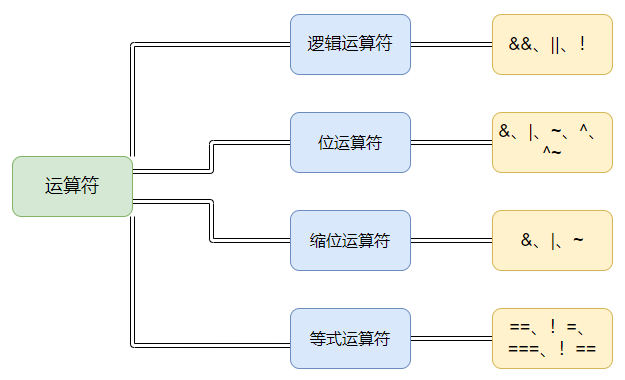

按照常见的几类verilog逻辑运算符可以将其分为以下几类

逻辑运算符:&&、||、!

&&和||是双目运算,用在两个数之间;!为单目运算符用在数字之前

在N = A xx B的逻辑运算中,A、B、N都只存在两个值:true or false,二者在机器中表示1和0;在进行操作时A与B的数据宽度可以不等

位运算符:&、|、~、^、 ^~

其中的&、|、^、 ^~ 均为双目运算符,~为单目运算符;相较于逻辑运算符,位运算符的核心是按位,二者具体的区别可以通过综合后的RTL视图进行区分

需要注意的是位运算符与逻辑运算符一样,两个运算数可以是不同长度,在运算的过程中右对齐,且缺少的位数将用0补齐

缩位运算符:&、|、~

又称为缩减运算符,为单目运算符;对单个操作数进行递推运算,运算结果得到的是一位二进制数

补充:异或同或也可以进行缩位运算,其中的缩位异或常用于奇偶校验

等式运算:==、 !=、=== 、 !==

进行数值的比较操作,相较于==而言===会更加严格;后者在比较时会对高阻态和不定态进行比较

以上便是关于verilog的逻辑运算符的一些基础知识,欢迎各位交流学习。

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

逻辑运算符两侧运算对象的数据类型是2023-11-30 3218

-

C语言中逻辑运算符的使用方法及优先级关系2023-08-21 5632

-

KUKA机器人的逻辑运算符2023-07-21 3770

-

C语言基础知识(4)--运算符2023-06-15 6271

-

Go语言运算符主要包括哪些呢?2023-05-26 1664

-

C语言逻辑运算符优先次序2023-03-09 4197

-

逻辑运算符与表达式2023-02-21 3570

-

什么是逻辑运算符2023-02-09 3416

-

python运算符是什么2022-02-21 3278

-

逻辑电路与逻辑运算符2021-07-16 1463

-

逻辑运算符是什么2021-07-14 1390

-

C语言中的逻辑运算符是怎么样的2020-02-20 5010

-

单片机的逻辑运算符和位运算符是什么?数字电路中的常用符号2018-10-03 28121

-

条件运算符是什么_条件运算符有哪些2017-11-16 11545

全部0条评论

快来发表一下你的评论吧 !