DUV与EUV***的芯片加工流程详解

制造/封装

描述

近日清华提出的SSMB-EUV光源技术忽然引发了公众极大的兴趣。一个说法是,中国可以建加速器产生EUV光源,不同频率的光源可以给28nm、14nm、7nm、5nm等多种芯片制程使用,用“光刻厂”替代ASML一台台的EUV***,以出人意料的创新思维打破美国封锁。这个设想“通俗易懂”,感觉先进的国产***一下有希望了。 公众对SSMB-EUV这种很难懂的同步辐射光源产生兴趣,根本原因是希望突破美国技术封锁,将清华的研究产业化,帮助生产出高性能***。 本文从产业工程角度,重点介绍芯片制造与光刻的一些相关技术细节,也介绍SSMB、EUV、同步辐射等相关的科学原理。了解足够的工程技术细节和科学原理之后,对于“光刻厂”这类有趣的设想,就能正确看待了。

本文要点: 1. SSMB-EUV***是有技术背景的,中国已经有实际的研发投资,确实是未来***的一个发展方向。 2. 分析DUV与EUV***进行芯片加工的流程,工业生产对***性能的要求是超乎一般人想象的。 3. SSMB-EUV***需要突破的技术困难,可能是哪些。千万不能以为找到一个好方向,就能很简单地突破***。

一、芯片制造产业常识

将四价硅掺杂加入少量三价硼和和五价磷做出PN结,再加上金属氧化物做个控制门,就能做成某类晶体管。海量晶体管密集排列,按特定设计互相连接,就是芯片。芯片制造最关键一步是晶圆加工,在FAB工厂里,在高纯度的硅晶圆(wafer)上面,做出一个个的相同的裸芯片(die)。前面需要做出硅晶圆,后面需要将die切开,加盖、加引脚、封装、测试,难度都相对低。

首先要有概念,工业应用意义上的芯片产量是海量的,不然成本太高。如近日引发轰动的某爆款手机的芯片,业界估计有1000万颗的量,后因需求火爆增至1500-1700万颗,又再上调到2000万颗。

上千万颗芯片,如何在不太长的时间内制造出来?关键是一片wafer上能一次性制造出大量完全一样的die。以12寸晶圆(指英寸,还有8寸、6寸的)为例,它的直径是约300毫米,面积是70659平方毫米。先进芯片的晶体管密度能达到惊人1平方毫米1亿个,整个芯片有上百亿个晶体管,完成复杂的5G基带与手机SOC功能。假设一个die面积是140平方毫米,一片wafer上就可能有约500个die的位置。

芯片制造有“良率”的概念,简单地说,如果这500个die在FAB加工完毕,下单的商家拿去一测,发现有400个是功能合格的“活”die,良率就是80%。先进芯片加工的良率有时不高,但也不会太低,不然没有商业意义了。如按50%估计,一片wafer也应该有200个以上的die是活的。

FAB工厂的产能一般用每月能加工多少万片wafer来说明,多的可以1个月10万片,少的也有1万片。如果每月1万片,每片200个活die,一个月就有200万颗芯片,一年能生产出2000万颗以上的芯片了。

有些不懂的人会以为,芯片制造全靠***,工厂就是有个核心机器***,晶圆送进去,里面用光在上面把芯片“刻”出来,主要的加工就完成了。如有的人说,买到100个***,就能建100条芯片生产线,可能就是这么简单理解的。

其实更合适的说法是,芯片上的晶体管是“蚀刻”出来的。用等离子体物理冲击或者化学药水浸泡之类的办法,在wafer上造出沟沟槽槽,最后就把晶体管的形状挖出来了。但是哪挖哪不挖,这是由光刻引导的。可以说,凡是要蚀刻了,都要先光刻,通过“掩膜板”(mask,光罩)告诉蚀刻冲哪下手。而且挖沟槽的的办法非常复杂,有时要反复地挖,经常还要在上面沉积覆盖一层各种材料。每一步做完,还得清洗。

实际FAB加工晶圆的步骤极为复杂,多的可能要上千步,光刻就要反复做多次,一般需要多个***。一个复杂的先进制程芯片,用于光刻的一套光罩就可能有好几十个。重要步骤需要精度高的***,也有精度要求低些的,可以用低配的***。如wafer上的晶体管层做好以后,在上面做连接的金属导线层,精度要求就低不少,因为可以象建楼房一样,分成好几层来放导线,每一层导线的间隔可以宽一些。

一片wafer开始加工,到最终变成die交付给客户,因为步骤很多,过程可能要几个月。这往往是因为,生产线上的机器,不只是生产一个芯片,会排班加工别的wafer。如何安排,将不同芯片的wafer在指定的时间送到指定的机器上,是FAB生产流程管理的重要问题。即使全力保证一个芯片的加工流程先跑,工序多的,一片wafer怎么也要一两个月才跑完。

客户让FAB加工芯片,不是下单就有,即使追加订单,也要过几个月才有。无论如何,几个月就能生产出上千万颗芯片,这是海量的加工能力,量上来了,单个芯片才不会太贵。所以,FAB的生产能力是芯片工业应用的关键,一个月要起码能处理一万片这么多的wafer。

而且,***处理一个wafer,不是一次能完事的,基本会来好几次,有时要多重曝光,要上十次。所以,即使只处理一个芯片产品,一个月只做1万片,一个***可能也要做10万次光刻。FAB是周末也不敢让机器停的,要排班开工,一个月30天,每天可能要光刻3000次,***平均一个小时做一百次光刻,是很常见的节奏。

因此,从工业生产的角度粗略估算,***要1分钟不到就把一片wafer上的几百个die都光刻完。每个die分到的光刻时间,只有0.1秒这个级别。如果搞不过来,就得加多个***并行处理了。

先进的***就是这么快速运作的。一片wafer放在工作台上,工作台在磁悬浮系统操控下,不停地游动,看上去根本就没有静止。其实这是在“步进扫描”,工作台在按某种自动程序走走停停,停下来就是对准了,在0.1秒时间内光线打下来瞬间完成光刻,把光罩上的图案投影到某个die的区域(实际是shot,可以简单理解成一个die的大小),和上面涂的特种光刻胶发生“光化学反应”,完成曝光。曝光快速完成,工作台又快速步进扫描到下一个位置,看上去和没停一样。走走停停的加速度非常大,对工作台运动控制、定位的精准度要求非常高,这也是***制造的最核心难点之一。

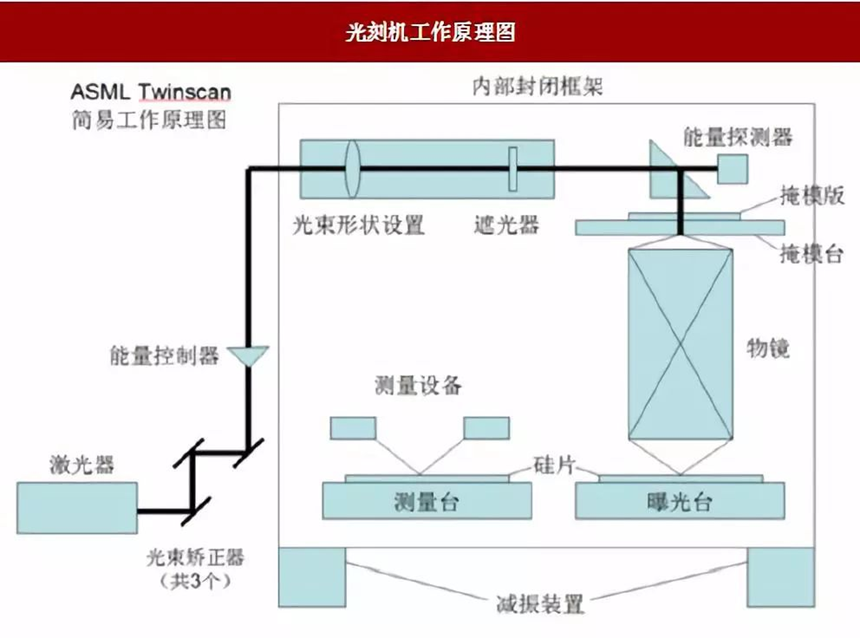

ASML的***型号有TWINSCAN的说法,从运作录像上看,是两个工作台在下面游动。这并不是两个工作台同时在进行光刻,而是一个在步进扫描光刻,一个在“预对准”。预对准是说,测量台上一片wafer上几百上千个die的区域,先用量测工具扫描一通,判断好是怎么排列的,每一步要跳多少纳米过去才能精确对准,把这些数据先记下来。等在光刻的那个工作台处理完了,立刻就把预对准的这个工作台挪过去,按测量好的数据安排好步进扫描的自动程序开始光刻。

无论是EUV***还是DUV***,都是很先进的机器,关键在于工业生产的量和速度要求非常高。如果慢腾腾地每一步都要重新对准,假设***一分钟才能处理一个die,一天也就处理1000多个die,只能搞完一两片wafer,那工厂不要开门了,早赔死了。

这是一般人不知道的,不理解***要快速自动精准连续运作,对要求有多高不清楚,容易低估工业应用级别***的性能要求。

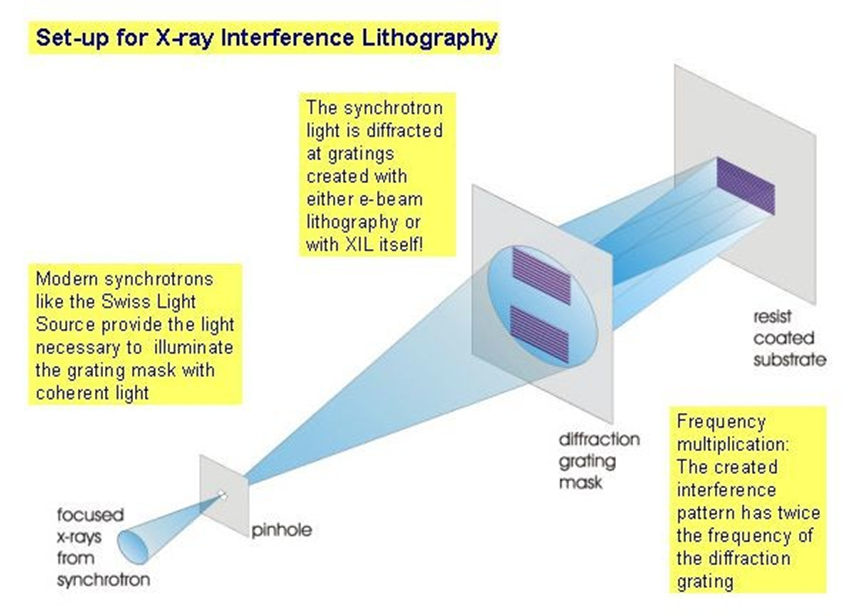

用同步辐射EUV光源进行芯片加工,其实不是新鲜事。最早的时候,研究者就是用同步辐射加速器的EUV光源进行芯片工艺研究的,现在也一直都有,经常有论文。如保罗谢勒研究所,长期用瑞士的同步辐射加速器探索EUV光刻的新技术,在学术界,EUV光源也称之为软X光。但是这类研究的特点是不讲究“量产”,也不需要省时间,慢慢地做几片,测一些数据,就可以发表有探索意义的发现了。以前没有能工业应用的EUV光源,就是这么搞研究的。 从产业角度看,芯片业最重要的还是要工程应用,要量产,要经济意义上成立。通过上面的计算可知,这个要求特别高,量产的良率与生产速度不可思议地高。如果对芯片制造产业流程没有深入了解,会很难想象,现代的FAB怎么可以如此快速地加工生产出海量的芯片。 这也是有个过程的,一开始手工制造芯片,或者半自动半手工,产量都高不上去。1977年7月,邓小平与30位科技界代表在人民大会堂座谈,半导体学界的王守武说:“全国共有600多家半导体生产工厂,其一年生产的集成电路总量,只等于日本一家大型工厂月产量的十分之一。”这就是手工与自动的区别,看着芯片制程差距不大,实际背后的制造流程差异很大,技术水平差异很大。

现在,中国一天可以生产10亿颗芯片了,进步非常大,都是自动化机器干出来的。芯片制造已经必然是机器自动做的,人只能去管理机器。机器生产芯片,各个流程在非常快速地流转,是标准的流水线生产模式。只是芯片FAB生产线容易出问题被迫停下,需要很多有技术的人来维护生产线顺畅运行,这一点比其它商品的生产线要困难得多。

二、DUV、LPP-EUV光源

上面说的芯片制造过程,对传统芯片(28nm及以上)和先进制程芯片(14nm及以下)都是通用的。目前用的***主要是DUV的,193nm波长的光源是ArF(氟化氩)准分子激光器生成的,浸润式***光在水中折射后波长变成134nm。 前面还有汞灯光源(不是激光),g线***是436nm波长,i线***是365nm波长。还有KrF(氟化氪)准分子激光器的248nm光源。 根据瑞利准则公式和实践结果,193nm***的分辨率是波长的三分之一,能用来做65nm的芯片。

浸润式***的134nm波长,按规律可以做45nm的芯片。但是镜头在水里效应提升,又通过OPC补偿算法(光罩上图形的角上,弄成特定的复杂形状而非原来的方形,最终成像反而会更接近方形),最终分辨能力提升到了28nm。这就是经典的28nm芯片的由来,坊间有所谓“28nm***”的说法,其实是193nm的光源。

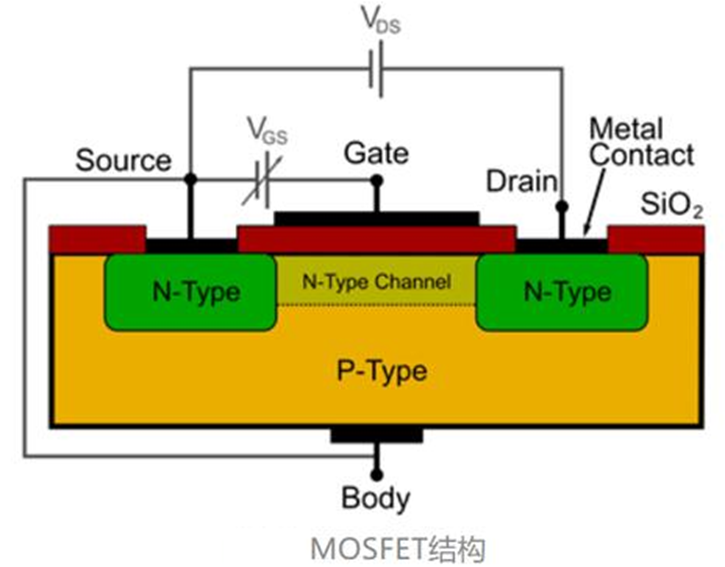

28nm及以上制程的传统芯片,里面的晶体管是MOSFET,可以理解为一种平面的晶体管,有个控制门Gate,从上往下这“一个方向”施加电压,控制晶体管的0-1导通状态。28nm指的是Source和Drain两个栅极之间的宽度,整个晶体管有100nm以上这么宽。

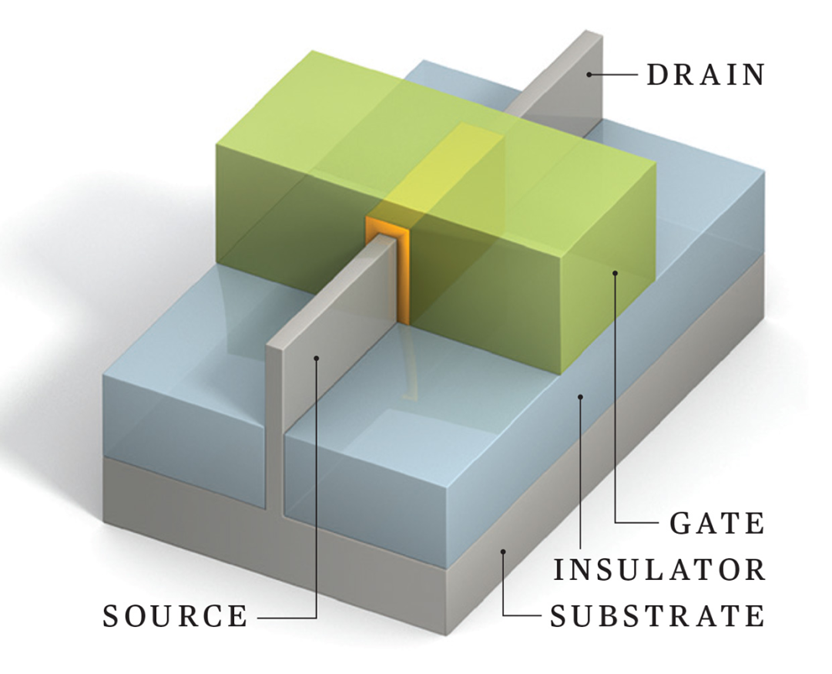

FINFET晶体管就升级成“立体”的,如上图,绿色的Gate从上方、左方、右方三个方向去施加电压影响晶体管导通状态。三个方向的立体影响,比MOSFET的一个方向的平面影响要灵敏,所以FINFET晶体管的功耗更低、主频更快。但是这个晶体管,就要象鱼鳍一样,造出往上伸出的薄薄的fin,工艺要复杂多了。需要注意,FINFET晶体管在wafer上也还是一层,并没有堆出几层来,众多晶体管还是平面排列的,只是fin是立体结构对控制电压敏感了。 用DUV浸润式***和FINFET晶体管工艺,可以造7nm-14nm制程的芯片。主要的办法是多重曝光,最多是四重曝光。简单地比喻,先在wafer上造出28-28-28-28nm这样间隔的线条,然后挪动14nm,再来做一套28-28-28-28nm间隔的线条,就能用双重曝光组合出14-14-14-14nm间隔的线条。如果四重曝光,就能组合出7-7-7-7nm间隔的条纹。

当然这只是类比,实际要复杂得多,但是基本原理就是把本来一张光罩做的事,拆成很多张光罩来做。到7nm,工艺就非常麻烦了,光罩数量需要非常多,但是业界优秀的公司居然真的用DUV***实现了7nm芯片量产。 值得注意的是,28nm及以上的传统芯片,它的“制程”是实打实的,说28nm真实栅极距离就是28nm。而先进芯片的7nm-14nm,包括再往下的5nm、4nm、3nm芯片,栅极宽度并不是标称的值。

各家制造芯片的公司各自声称,根据功耗等性能指标的改进,按摩尔定律算出来一个“等效面积”(PPA,Power Performance Area),说是7nm,实际测量可能是10nm。英特尔说的10nm工艺就是实在的,说是10nm,指标相当于别家的7nm了。 可以看出,用DUV***来做7nm芯片,已经“穷尽”了招数,才能用193nm的光源,得到7nm的效果。浸润式、镜头改进、OPC补偿、多重曝光、晶体管立体化、等效面积,这才从193nm光源形式上实现了7nm的效果。用DUV***加工先进芯片,工艺非常麻烦,良率低、成本高。 大家都知道,后面业界是用13.5nm的EUV光源改善了状况,所以才叫EUV***。为什么从193nm光源直接就跳到了13.5nm?之前436-365-248-193nm这样降,后面不应该是再降一点么?

本来确实是这个想法,业界(主要是日本尼康)试了157nm的F2(氟气)准分子激光器光源,***也造出来了。悲剧的是,157nm波长的光,很容易被各种材料吸收掉,曝光性能很不好,要抽成真空来才行,很麻烦。所以业界放弃了157nm波长***,类似波段的光都有被材料吸收掉的严重问题。光源需要通过反射、折射,经过空气、镜面、物镜到达wafer,必须还有足够能量用于曝光,不能被吸收得功率不足了。 最终发现13.5nm的EUV光源,经过反射以后,强度可以用来搞光刻。这是实验的结果,有很长时间的探索过程。 前面说了,工业应用的EUV***要能快速准确地曝光,0.1秒这么短的时间就要和光刻胶反应好,光的功率也要足够。当工作台将wafer移到特定位置时,强度足够EUV光线就得过来,这非常困难。

目前工业应用的是二氧化碳激光打在锡滴上,产生EUV光,再经过复杂的光路反射到达wafer。 这是锡滴产生EUV光源的GIF演示 这就是LPP-EUV光源(LPP,Laser-produced Plasma),二氧化碳激光打在不断滴落的锡滴里,产生不多的一些EUV光。然后用11个镜子不断反射过滤,最终将这些EUV光引导到wafer上。由于锡滴产生的EUV光不多,主要是别的杂质光源,如何过滤、聚集、矫正光束,非常麻烦,需要很高水平的镜片系统。 据说EUV***的镜片,是世界上最光滑的物体之一,超过了中子星表面。而且镜片也要非常大,超过一米的直径。如果把镜片放大到地球这么大,表面粗糙度也只有0.2毫米。这是因为镜面反射会放大误差,只有把镜面做得极为光滑平整才行。

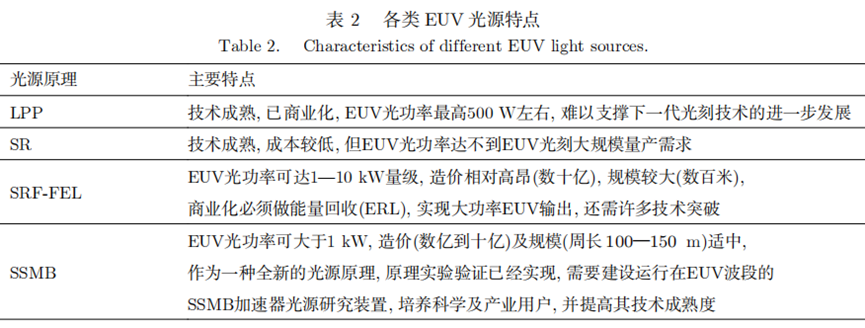

经过多次反射以后,即使光束每次反射仍然有70%的能量,11次也只剩下了2%的能量了。因此,LPP-EUV光源就需要生成巨大的能量。ASML的EUV***是美国Cymer公司负责光源(也是EUV***断供中国的技术源头),需要每秒发射5万次高功率二氧化碳激光轰击锡滴,技术难度非常高。 因此,EUV***比DUV***难得多。DUV光源是准分子激光器直接产生的,EUV光源只能间接产生一些。但是DUV***的镜头组、对准系统,也是非常困难的,精度要求也非常高了。EUV光刻的精度要求更高,但相比DUV光刻,主要还是光源系统更为复杂。因为光源的能量绝大多数浪费掉了,还有额外的散热问题,风冷水冷一堆麻烦事。 还有坏消息,EUV***的光源功率做不上去了,也就是500W。EUV***对于3nm芯片加工就有些吃力了,成本很高,一般客户已经不敢下单了,有需求不足的问题。再往下做,不是成本的问题,是光源的功率不够了。 业界需要找到更好的光源,而SSMB-EUV光源就是选择之一。

三、SSMB-EUV同步辐射光源

这是清华唐传祥、邓秀杰2022年在《物理学报》上发表的《稳态微聚束加速器光源》综述文中的总结。综述文显然对SSMB成为更好的EUV光源抱有较大希望。 相关的科学“师承”与重要成果大约是: 1. 1971年,赵午从台湾到纽约州立大学石溪分校师从杨振宁。杨振宁让赵午学习科朗的加速器课程,1974年赵午博士毕业时,很有眼光地说服他不要选前途不大的高能物理领域,把加速器当主要研究方向。赵午成为加速器领域的顶尖学者,在美国斯坦福大学线性加速器中心任职。

2. 2010年,赵午与博士生Ratner提出了SSMB的设想,但学术界和业界没人有兴趣。2015年赵午意识到,要主动在学术会议上宣传想法。 3. 赵午成为清华大学客座教授,杨振宁也在清华,帮助建立了SSMB研究团队。 4. 清华团队与德国团队合作,2018年在德国马普所的ELBE环形加速器上进行了改进实验。之后取得了突破,数据很好,开了茅台庆祝,相关成果2021年发表在《自然》上。 5. 中国意识到SSMB-EUV光源对***研发的关键作用,在雄安进行了科学装置投资建设。

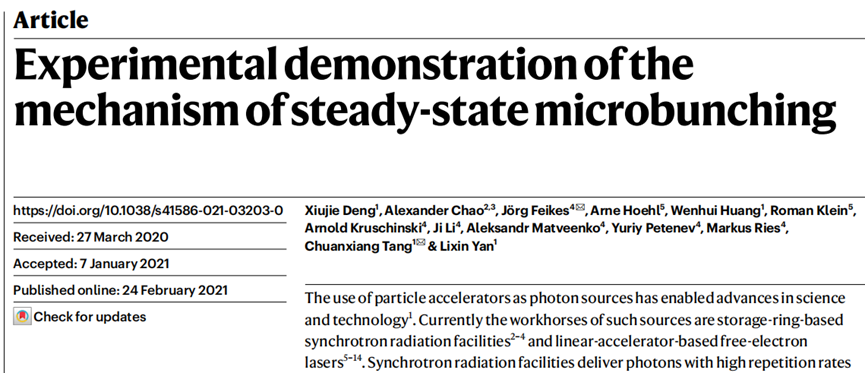

2021年2月,《自然》发表的SSMB论文

从清华2023年初的官方新闻看,雄安SSMB项目出发点就是为了芯片“卡脖子”,有部委支持。可以看出,项目选址地点有了,建筑模型有了,但应该还在落地过程中,啥时能建成不太清楚。 因此,SSMB-EUV光源从科学原理上,国际顶刊《自然》认可。在实际工程上,也已经开干了,落地雄安。所以,这事绝对不是忽悠,研究团队是真的要把SSMB-EUV光源给干出来,数亿的投资应该批下来了。 要注意到,SSMB目前显然还是在科研阶段,雄安在建的SSMB新型加速器,是要建立科研平台,把SSMB-EUV光源的性能提升。这离实际造出EUV***还差很远,不宜过分乐观。

LPP-EUV光源从提出设想到开发成功,到进入实际工业应用量产,有超过20年的时间。ASML开发出EUV原型机用了13年,到实际量产应用,又是近10年。 在卡脖子的压力下,如果科学原理与工程上都是可行的,中国的进度会快许多,但也不太可能立刻解决问题。本文无法对时间进度作出估计,主要还是介绍相关技术背景。其实最重要的还是,SSMB-EUV光源进行工业光刻应用是否可行。只要可行,相信中国一定能干出来。 为了帮助对科学感兴趣的读者理解,后面介绍下SSMB同步辐射光源的科学原理。

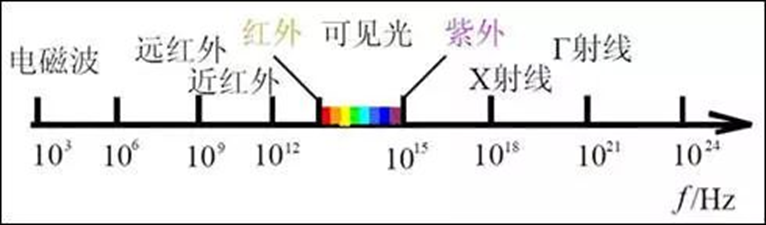

SSMB,就是Steady-State Micro-Bunching,稳态微聚束。这个“聚束”,说的是电子聚集。SSMB光源,是说其中的电子在接近光速的情况下,在磁场中偏转,会在切线方向发出电磁辐射,也就是光。而这就是同步辐射(SR,Synchrotron Radiation)加速器出光的原理。电子在加速器里因为磁场约束绕圈,一秒能几百万圈,相当于存储在环里,一边绕一边发射电磁波。由于电子速度非常高,数量不少,能量也就不低,发出的电磁波就很多。 为什么叫同步辐射,其实是历史的误会,最初发现电子发出切线方向的光,是在通用电器的一个同步加速器里,所以这么叫了。同步辐射光源本身没有啥同步的,特点是全光谱、亮度高、窄脉冲、高准直。

全光谱就是说,从红外到深紫外(EUV)乃至X射线的光谱都有。亮度高,就可以象X光机一样,用来探查物质的内部,而且比X光机功率更高,探查能力更厉害。其中一些EUV光可以用来作光刻研究,前面说了,工业化量产是不行的,效率太低。

“功率较低”就是传统同步辐射光源的弱点。虽然同步辐射光比X光机要更亮,但是人们总想要更高功率,工业应用要求很极端,EUV光刻就是一个。同步辐射光源为什么功率低,是因为电子束长度太大,没有相干性,电子发出的电磁辐射是“非相干叠加”,功率就不高了。

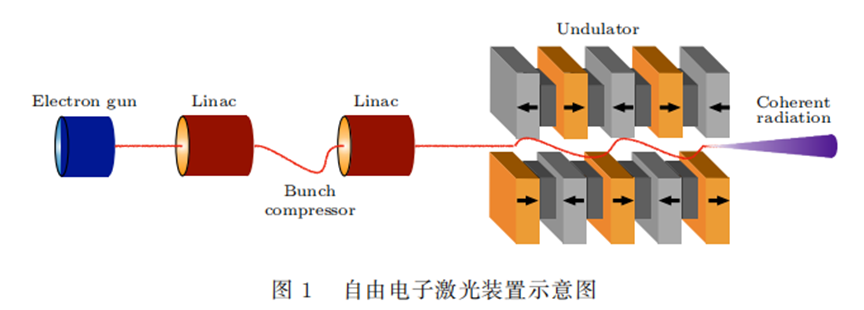

1971年提出的改进办法是“自由电子激光”FEL(free-electron laser),关键是有一个“波荡器”(Undulator)。电子产生后直线加速到接近光速,在波荡器里偏转发出SR。但是与电子转圈的加速器磁场不一样,这个波荡器的磁场是震荡的,通过巧妙的安排,电子束团就会变成“微聚束”长度缩得很短,更加聚集,还有相干性了,出来了“相干辐射”(Coherent radiation),功率指数增加直到上限,亮度能比传统同步辐射高上亿倍,当然是脉冲的。 SRF-FEL(SRF是超导射频)也成为下一代EUV光源的选择之一,功率是强了,但是造价高。注意这个FEL装置是直线放置的。

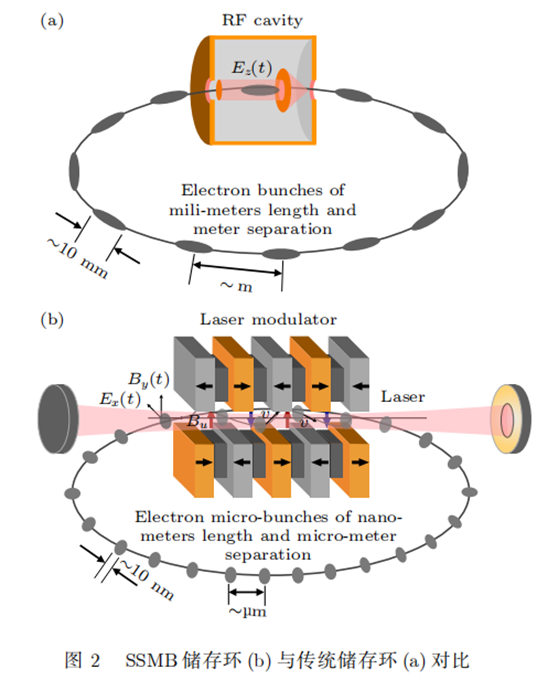

稳态微聚束的关键思想,是在传统同步辐射加速器的电子存储环里面,引入了激光调制。本来电子在存储环里,形成聚束是用“微波射频腔”(RF cavity)做的,改用复杂得多的激光调制系统,加上扭摆磁铁,横向纵向下手调制,巧妙地把电子束更加完美地聚集在一起。SSMB能在《自然》上发表文章,就是说怎么实际下手,证明了电子束形态确实更加完美了。

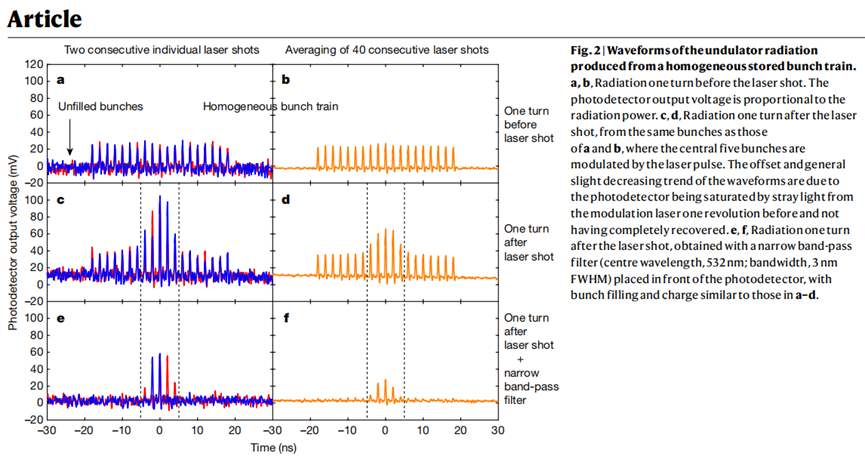

清华与德国团队SSMB实验结果

上图,图ab是没有经过激光调制的波形,是宽的。图cd是激光和磁铁进行了一次调制的结果,中间五个束冒出来了。图ef是加了个滤波的结果,结果更明显了。当然实验只干了一次调制,继续调制应该是有技术困难要克服,是后续工作。

SSMB就产生了和FEL类似的“微聚束”,但是关键还加上了“稳态”。FEL不是稳态,电子团在波荡器里自由互相作用,最后发出强光完事。SSMB是让电子束在存储环里绕圈,这样就有可能是“稳态”的,对于重复发光很重要。也就是两个特性结合:微聚束的相干辐射发强光 + 存储环高重频。

清华研究论文认为,这两个特性结合,SSMB-EUV光源进行光刻就很有潜力。看上去是比直线的SRF-FEL好,更加好控制。让电子束在存储环里转圈,需要发强光了,就让微聚束发出相干辐射,导出EUV光源进行光刻。

据赵午2021年在杨振宁学术思想研讨会上的视频介绍,SSMB-EUV光源做***的优点是:只要三块反射镜(因为SSMB-EUV光源比LPP-EUV光源要纯净),镜片面积要求也小得多,只要十分之一。这看上去是巨大的优点,光源质量上比ASML的EUV***强,整机开发难度肯定能下降不少,镜片的要求就降低了。

但是这巨大优点,前提是SSMB-EUV光源开发成功。SSMB后续开发有不少难点,在《物理学报》的论文综述中都实在地提出了,技术细节较为难懂。一类是微聚束在存储环中产生与维持的问题,一类是SSMB相干辐射发光的问题,都需要很多后续研究。

电子微聚束听上去不错,但是电子在转弯,会纵向滑移,聚束就没法维持了。激光和电子微聚束要以巧妙的角度调制,怎么保持好角度,也很困难。这类实际问题,在工程中会成为巨大的麻烦,让看上去不错的理论结果迟迟无法成功落地,出现一时难以克服的大问题几乎是必然的。

这也是科研中常见的现象,实际搞研发的人一身冷汗,一堆问题等着解决,在加班加点绞尽脑汁。外界看见点苗头,就说得好象成功在即了,美国技术封锁马上完蛋了。有些人甚至把北京的加速器图片拉来说是光刻厂,其实完全不相干。

个人判断,SSMB-EUV是一个好方向,从理论上很有潜力,相比LPP-EUV光源优势明显。如果最终SSMB加速器建成,成功地提供EUV光源进行光刻,这确实是一个模式突破,从小型的EUV***,变成靠大型装置解决问题。

但是最终成功还有两大步要跨越。一个是SSMB加速器落地雄安,产生出了高质量的EUV光源,搭建好以大科学装置为基础的研发平台。再一个是以优质的SSMB-EUV光源为基础,以量产为目标,研发适配的EUV***,虽然难度应该比ASML的LPP-EUV光源的***要低,但也是很困难的。

EUV***有光源、工件台、物镜、激光干涉仪等关键部件,每个部件的开发都非常难。更困难的是,将所有部件组合成完整的系统时,互相匹配会很困难,甚至顾此失彼发生冲突。

一个研发选择是,清华SSMB加速器出光以后,不是直接研发EVU***,而是先与DUV***对接,光束能量损失较小,先在难度低一点的平台上完成阶段任务。

这几大步即使成功,时间不会太短。但是,中国在美国倒逼帮助下,开始想各种办法解决极为困难的科学与工程问题,许多人将奇思妙想与工程实现结合,这个过程将是激动人心的。越是困难的问题,成功的收获越是巨大,我们可以学习了解科学原理与技术背景,并耐心等待。

■ 作者简介 陈经 中国科学技术大学计算机科学学士,香港科技大学计算机科学硕士,科技与战略风云学会会员,《中国的官办经济》作者。

编辑:黄飞

-

一文详解晶圆加工的基本流程2025-08-12 5521

-

数控加工工艺流程详解2025-02-14 4132

-

SMT贴片加工:详解smt贴片加工精度2023-12-20 2286

-

什么是EUV光刻?EUV与DUV光刻的区别2023-10-30 5506

-

国产***EUV与DUV的分类2023-03-20 13871

-

duv光刻机和euv光刻机区别是什么2022-07-10 87847

-

duv和euv光刻机区别2022-07-06 68830

-

芯片制造全流程及详解2021-12-10 18348

-

从EUV到DUV:先进制程离不开DUV2021-04-29 12805

-

解读ASML澄清中芯国际购买协议事件和EUV与DUV的差异性2021-03-15 3449

-

27张详解ASIC芯片设计生产流程的PPT2019-07-16 12269

-

EUV热潮不断 中国如何推进半导体设备产业发展?2017-11-14 6839

-

芯片封装测试流程详解ppt2012-01-13 78093

-

PCB加工流程详解大全2009-11-30 41201

全部0条评论

快来发表一下你的评论吧 !