高压功率MOSFET外延层对导通电阻的作用

描述

1、超级结构

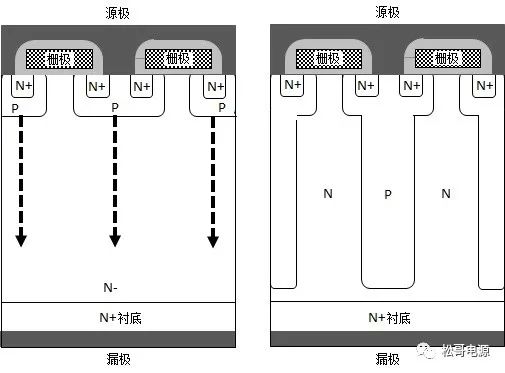

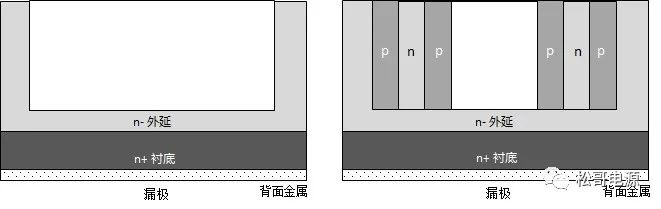

高压功率MOSFET管早期主要为平面型结构,采用厚低掺杂的N-外延层epi,保证器件具有足够击穿电压,低掺杂N-外延层epi尺寸越厚,耐压额定值越大,但是,导通电阻随电压以2.4-2.6次方增长,导通电阻急剧增大,电流额定值降低。为了获得低导通电阻值,就必须增大硅片面积,需要更大晶片面积降低导通电阻,一些大电流应用需要更大封装尺寸,成本随之增加,Crss电容增加导致开关损耗增加,系统功率密度很难提高,应用受到很大限制。

高压功率MOSFET外延层对导通电阻起主导作用,要保证高压功率MOSFET管具有足够击穿电压,同时,降低导通电阻,最直观方法就是:

(1)在器件导通时,形成一个较高掺杂N区,作为功率MOSFET管导通的电流通路;

(2)在器件关断时,去除较高掺杂N区的载流子,方法就是使用PN进行耗尽,保证要求耐压等级。

按照上面原理,将平面结构的P-体区结构一直向下,直到几乎贯穿整个外延层,就可以实现上述要求。超结结构Super Junction高压功率MOSFET管就是基本这种设计思路,这种结构主要特点是几乎贯穿整个芯片厚度P柱和内建横向电场,这种结构在学术上称为超结结构。

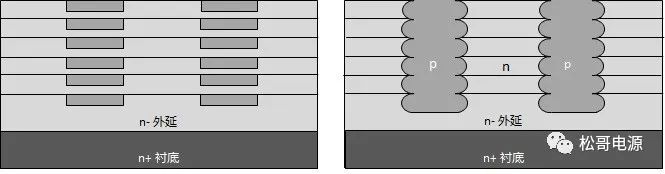

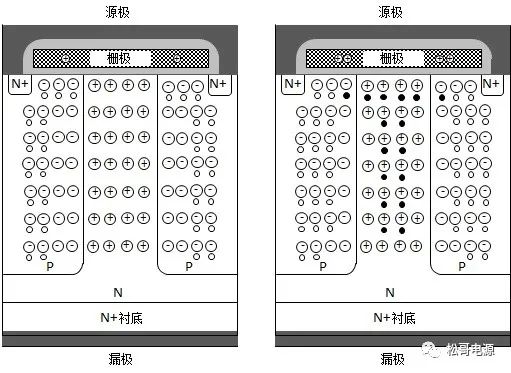

(a)平面结构P区下移 (b)超结结构

1 内建横向电场超结结构

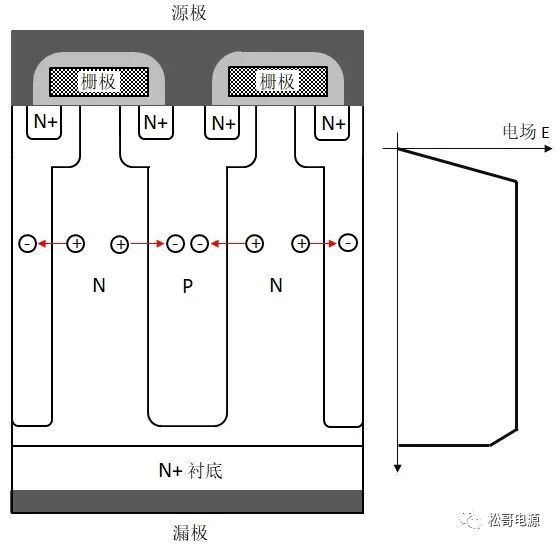

超结结构中,垂直导电N区夹在两边P柱中间,水平方向,N区和P柱二侧都形成PN结;垂直方向,P柱底部和下面外延epi层N形成PN结,栅极下面P区形成反型层产生导电沟道。功率MOSFET管关断时,P柱和垂直导电N形成PN结反向偏置,PN结二侧都会形成耗尽层,建立水平横向电场,这个电场为矩形电场。耗尽层增大,横向水平电场也增大。

随着外加反向偏置电压增大,垂直导电N区和P柱内耗尽层宽度不断增加,直到垂直导电N区和P柱整个区域基本上全部耗尽,几乎全部变成耗尽层,耗尽层横向矩形电场达到非常高幅值,具有非常高的纵向阻断电压。和平面结构对比,横向电场将外延层N-三角形电场变成梯形或矩形电场,提高器件耐压。因此,同样耐压可以减薄器件外延层N-厚度,降低导通电阻。此外,P柱底部与和它相接触外延层N-也形成PN结,反向偏置形时,产生耗尽层,形成垂直电场,进一步提高器件耐压。

图2 超结结构内部电场

MOSFET导通时,栅极和源极电场导致栅极氧化层下部P区反型,形成N型导电沟道;源极区电子通过导电沟道进入垂直N区,中和N区正电荷空穴,垂直N区耗尽层宽度不断降低,直到垂直N区恢复到初始状态。初始状态垂直N区掺杂浓度高,电阻率低,因此导电电流通路导通电阻低。

比较平面结构和沟槽结构功率MOSFET管,超结结构实际综合了平面型和沟槽型结构两者特点,在平面型结构中开出一个低阻抗电流通路沟槽,因此具有平面型结构高耐压和沟槽型结构低电阻特性。内建横向电场高压超结结构,克服了平面高压功率MOSFET管缺点,其工作频率高,导通损耗小,同样面积芯片,可以设计更低导通电阻,因此具有更大额定电流值。

超结结构高压功率MOSFET管需要制作贯穿整个芯片厚度P柱,生产工艺比较复杂,单元一致性较差,雪崩能量不容易控制;超结结构必须严格控制P柱区与外延层N区浓度和宽度,否则二侧不对称耗尽导致中间电荷不平衡,影响超结结构耐压。外延层N掺杂浓度越高,影响越大。

降低漂移区厚度,提高漂移区掺杂浓度,以及降低单元Pitch尺寸,可以进一步降低导通电阻。但是,降低单元Pitch尺寸,必须增加N漂移区掺杂浓度,就必须对N漂移区和P柱区进行精确补偿,必须非常严格控制它们掺杂浓度和宽度。耗尽电荷平衡偏差越大,电压阻断能力损失就越严重,器件雪崩能力和单元一致性越差,对生产工艺和技术要求就更加苛刻。

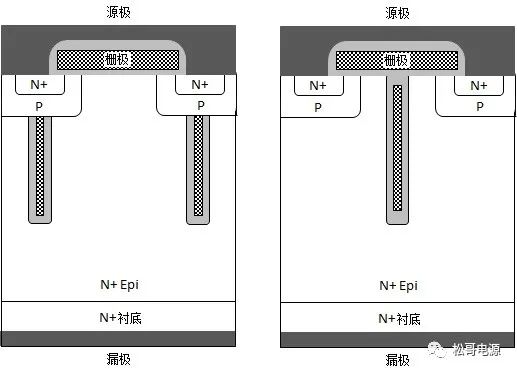

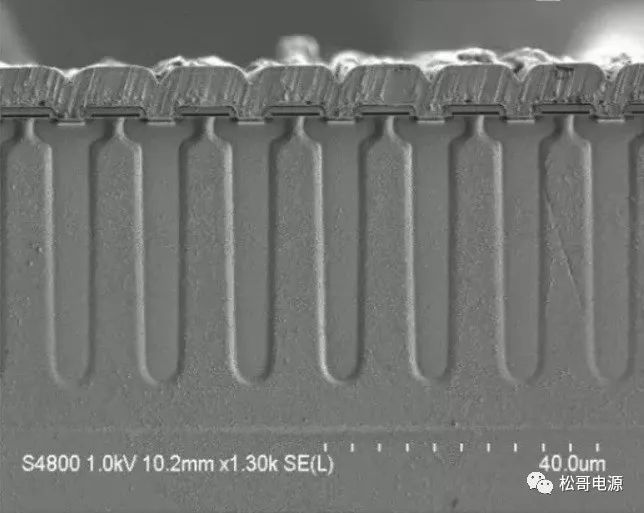

有些中压功率MOSFET管也采用超结技术,降低导通电阻,同时使用较大Pitch尺寸,减少单元相互之间加热效应和电流集中影响,不容易形成局部热点Hot Spot,提高线性区性能。中压功率MOSFET管超结技术,除了采用前面P柱超结结构,还可以使用深沟槽工艺的场板结构。深沟槽场板尺寸,贯穿芯片厚度大部分尺寸,并不完全贯穿芯片整个厚度,在沟槽表面制作氧化层,里面填充多晶硅,多晶硅连接到源极,氧化层隔离多晶硅和N-漂移层。

这种结构相当于在N-漂移层内设计一个隔离场板,隔离场板可以提供移动电荷,器件漏极和源极加上电压阻断时,补偿横向的N-漂移层电子。隔离场板沟槽底部氧化层,承受器件全部漏极和源极阻断电压,其电场强度非常高,因此,沟槽底部氧化层工艺要精确控制,避免沟槽底部局部区域氧化层变薄和防止应力造成局部缺陷产生。

(a) 两侧场板 (b)中间场板

图3 超结场板结构

超结结构纵向电场几乎是均匀分布,隔离场板结构纵向电场分布有2个峰值,1个电场峰值在P体区和N-漂移区PN结;另1个电场峰值在在场板沟槽底部。200V以下中压功率MOSFET管可以采用这种场板超结技术。

新一代超结工艺进一步减小器件晶胞尺寸,沟道和晶胞宽度进一步缩小,两个P柱之间距离非常小,难以形成满足要求的沟道区,因此,采用沟道与P柱相垂直的结构,从而减少沟道区工艺加工难度。

图4 沟道与P柱垂直结构

2、超级结构生产工艺

超结P柱结构和场板结构,生产加工工艺主要有2种方式:

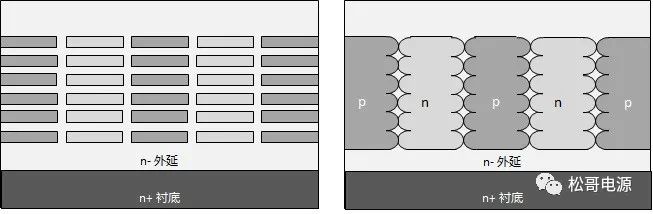

(1)通过一层一层多次外延生长,得到P柱结构或场板结构。

在衬底上外延一定浓度N层,在P柱区域开窗口注入形成P层,然后重复这些工艺,反复多次外延和注入,最后形成超结结构。也可以先在衬底上外延浓度较低N-层,分别在N区和P柱区域采用注入形成N层和P层,然后重复这些工艺,反复多次外延和注入,最后形成超结结构,这种方法均匀性控制更好,增加一次光刻与注入的工艺,成本增加。

(a) 单杂质注入

(b) 双杂质注入

(c) 单杂质注入 (d) 双杂质注入

图5 多层外延工艺

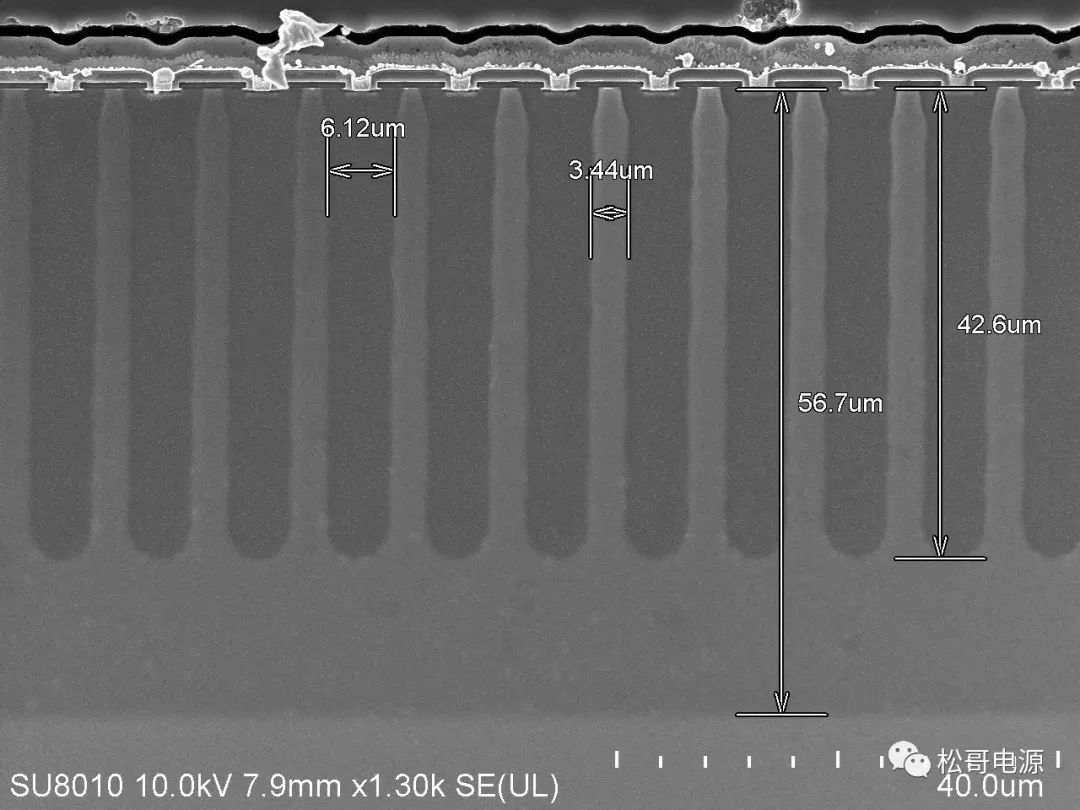

多层外延工艺每次外延层厚度非常薄,外延形成厚度相对固定,超结结构的尺寸偏差小,外延层质量容易控制,缺陷与界面态少。随着器件耐压增大,外延次数和层数增加,而且外延时间长,效率低,导致成本增加。

(

2)、直接开沟槽填充,即深沟槽技术Deep Trench,得到P柱结构或场板结构。

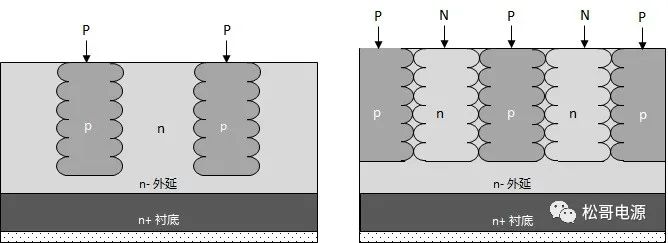

衬底和外延加工好后,在外延层刻蚀出深沟槽,沟槽的深宽比具有一定限制,然后在沟槽内部填充掺杂。可以在沟槽内外延填充P型材料,然后平坦化抛光,形成P住结构;也可以在沟槽侧壁形成薄氧化层结构,再填充多晶硅形成场板结构。另外,使用更宽的沟槽,采用外延或倾斜注入方式,在沟槽内部依附沟槽侧壁,依次形成P和N型区交错结构。

(a) 直接填充

(b) 宽沟槽侧壁注入、气相沉积与外延

图6 沟槽填充工艺

衬底和外延加工好后,在外延层(耐压层)中刻蚀出具有一定深宽比的沟槽,然后在沟槽内部填充掺杂。通常,有4种填充掺杂方式:一是在沟槽内外延填充P型材料,然后采用化学机械抛光平坦化。另外,可以在沟槽中直接通过P型杂质扩散形成P住;同时,还可以在沟槽内的侧壁上形成薄氧化层结构,再填充多晶硅形成场板结构。二是使用非常宽的沟槽,采用倾斜注入方式,同时控制N和P型杂质的注入剂量,分别在沟槽的侧壁上形成N区和P区,依次制作出P和N型区交错结构。三是通过在沟槽侧壁通过气相掺杂形成P型区。四是在沟槽侧壁选择性外延薄层N与P型,形成超结结构。

多次外延工艺相对容易控制,工艺步骤多,成本高;深沟槽工艺成本低,生产效率高,更容易实现较小的深宽比,形成的超结N区与P区掺杂分布均匀,导通电阻和寄生电容更低;但是,深沟槽工艺不容易保证沟槽内性能一致性,特别是深沟槽填充时,要保证沟槽侧面(侧壁)N和P区交界面没有空隙和孔洞,工艺要求特别高。侧壁出现空隙和孔洞,对性能影响在生产线最后检测中无法通过静态参数测量进行删选。

技术平台不一样,工艺不一样,超结结构Pitch尺寸和芯片厚度也不相同。

(a) 多层外延Multiple EPI

(b) 深沟槽直接填充Deep Trench Filling

图7 超结结构的截面图

3、超级结构开关工作过程

超结型结构工作原理及开关工作过程如下。

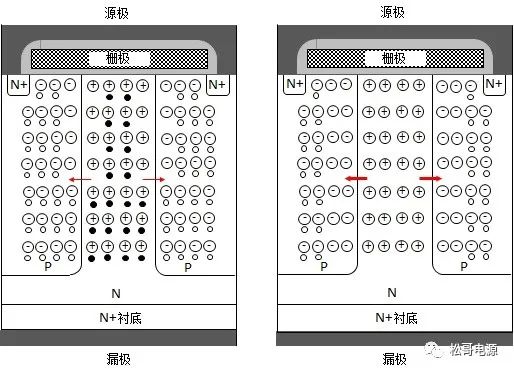

(1)关断状态

垂直导电N区夹在两边P区中间,MOSFET关断时,栅极电压为0,栅极下面的P区不能形成反型层,没有导电沟道。P柱区和垂直导电N区二侧横向形成反向偏置PN结,左边P柱区和中间垂直导电N区形成PN结反向偏置,右边P柱区和中间垂直导电N区形成PN结反向偏置,PN结耗尽层增大,并建立横向水平电场。反向电压足够高时,P柱区底部和外延层N区也会形成PN结反向偏置,有利于产生更宽耗尽层,增加垂直电场。

中间垂直导电N区渗杂浓度和宽度控制得合适,就可以将其完全耗尽,这样中间垂直导电N区就没有自由电荷,内部形成横向矩形电场,且电场幅值非常高,只有外部电压大于内部横向电场,才能将其击穿,所以,这个区域耐压非常高。

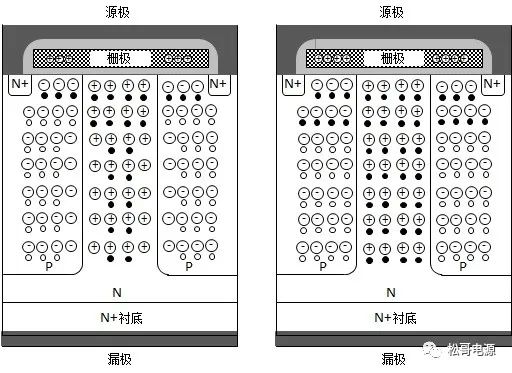

(a) 开始建立耗尽层 (b) 完全耗尽

图8 横向电场及耗尽层建立

(2)开通状态

栅极加上驱动电压时,栅极表面将积累正电荷,同时,吸引栅极氧化层下面P区内部电子到P区上表面,将P区上表面空穴中和,形成耗尽层。随着栅极电压提高,栅极表面正电荷增强,进一步吸引P区内部更多电子到P区上表面,这样,在P区上表面薄层,积累负电荷(电子)形成N型反型层,构成电流通道,即沟道。由于更多负电荷在P区上表面积累,一些负电荷将扩散进入原来完全耗尽垂直导电N区,横向耗尽层宽度越来越减小,横向电场也越来越小。栅极电压进一步提高,栅极氧化层下面P区更宽范围形成N型反型层沟道,电子不断流入垂直导电N区,垂直导电N区回到初始渗杂状态,形成低导通电阻的电流路径。

(a) VGS加正电压 (b) VGS增加形成反型层

(c) VGS增加沟道建立 (d) 沟道加宽完全导通

图9 超结结构导通过程

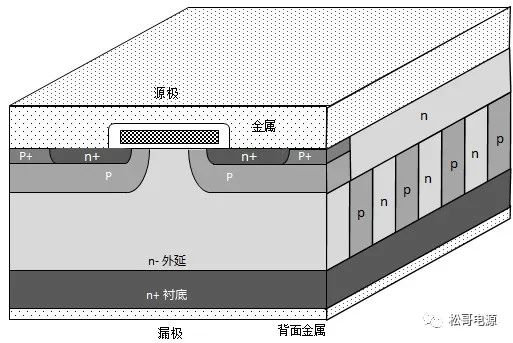

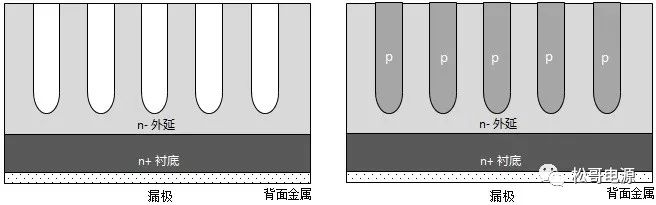

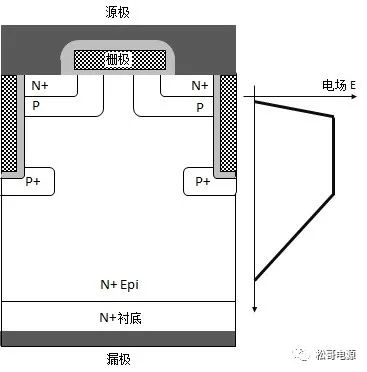

4、高压浮岛结构

另外还有一种介于平面和超结结构中间类型,这种结构内部P区被N-外延层包围,称为P型浮岛结构,电流密度低于超结型,高于普通平面工艺,抗雪崩能力强于超结结构。

图10 浮岛结构

这种结构工作原理是在内部浮岛P区和N-外延层交接处形成耗尽层,将N-外延层三角形电场在中间位置提升,从而提高耐压,这样可以适当减薄N-外延层厚度,降低导通电阻。

P型浮岛需要在N-外延层内部开出较深沟槽,形成P型浮岛结构,然后,沟槽里面填充多晶硅,连接到源极,沟槽深度并没有贯穿整个芯片厚度。沟槽深度越深,P型浮岛结构数量越多,耐压越高,但成本增加。

制作过程使用多次外延或深沟槽工艺,多次外延层数远少于超结结构,浮岛结构P型掺杂浓度控制没有超结严格,只要保证在反向偏压下不完全耗尽就可以,工艺成本低于超结结构;另外,正向导通时,P型浮岛浮空,不会向N-外延层注入非平衡少子,二极管特性好于超结结构。

审核编辑:彭菁

-

MOSFET导通电阻参数解读2025-05-26 3654

-

功率MOSFET基本结构:超结结构2023-11-04 6699

-

平面栅和沟槽栅的MOSFET的导通电阻构成2023-06-25 6094

-

外延层的掺杂浓度对SiC功率器件的重要性2022-04-11 10151

-

降低高压MOSFET导通电阻的原理与方法2022-03-17 3689

-

浅析降低高压MOS管导通电阻的原理与方法2018-11-01 5180

-

超级结MOSFET的优势2018-10-17 3190

-

MOSFET的导通电阻的概念及应用场合介绍2018-08-14 15120

-

三分钟读懂超级结MOSFET2017-08-09 4328

-

功率MOSFET结构及特点2016-10-10 7426

-

IR推出具有基准导通电阻的全新300V功率MOSFET2013-01-22 1624

-

IR推出汽车专用MOSFET系列低导通电阻2010-04-09 1051

-

导通电阻,导通电阻的结构和作用是什么?2010-03-23 5709

全部0条评论

快来发表一下你的评论吧 !